# Versal ACAP SelectIO Resources

# **Architecture Manual**

AM010 (v1.1) November 24, 2020

# **Revision History**

The following table shows the revision history for this document.

| Section                                                                                                                              | Revision Summary                                                                                                        |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 11/24/2020                                                                                                                           | Version 1.1                                                                                                             |  |  |  |  |  |  |

| XP XPHY                                                                                                                              | Removed bullet about XPHY UNISIM primitive.      Updated bullet about QBC and DBC functionality.                        |  |  |  |  |  |  |

| Bidirectional Datapath and Controlling IBUF_DISABLE and DYN_DCI                                                                      | Added new sections.                                                                                                     |  |  |  |  |  |  |

| Table 4                                                                                                                              | Updated Connection (RX) column for CLK_TO_LOWER, CLK_TO_UPPER.                                                          |  |  |  |  |  |  |

| Delays                                                                                                                               | Removed description of tap value from note.     Added sentence that CRSE delay cannot be controlled through the PL.     |  |  |  |  |  |  |

| Controlling Delays                                                                                                                   | Updated section and added Figure 8.                                                                                     |  |  |  |  |  |  |

| Controlling FIFO Modes                                                                                                               | Added note about not registering FIFO_EMPTY as part of the FIFO_RDEN = !FIFO_EMPTY connection.                          |  |  |  |  |  |  |

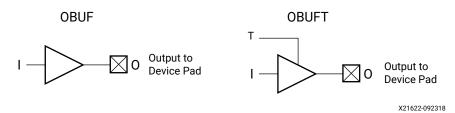

| Tristate Control                                                                                                                     | Rewrote section.                                                                                                        |  |  |  |  |  |  |

| Controlling Tristate Control                                                                                                         | Rewrote first sentence.                                                                                                 |  |  |  |  |  |  |

| Table 14                                                                                                                             | Updated second bullet in Controlled By column for VTC.                                                                  |  |  |  |  |  |  |

| Controlling IBUF_DISABLE and DYN_DCI                                                                                                 | Added PHY SM description and sequence.                                                                                  |  |  |  |  |  |  |

| Register Interface Unit                                                                                                              | Added references to Ports and Attributes sections in most tables.      Undated description of bit [2] in Table 19       |  |  |  |  |  |  |

| Table 19                                                                                                                             | <ul> <li>Updated description of bit [2] in Table 19.</li> <li>Updated description of bits [0], [1], and [2].</li> </ul> |  |  |  |  |  |  |

| Table 20                                                                                                                             | Updated description of bits [0], [1], and [2].                                                                          |  |  |  |  |  |  |

|                                                                                                                                      |                                                                                                                         |  |  |  |  |  |  |

| Table 38                                                                                                                             | Added new table.                                                                                                        |  |  |  |  |  |  |

| Table 41                                                                                                                             | Updated description of bits [9:0].                                                                                      |  |  |  |  |  |  |

| Table 44                                                                                                                             | Updated description of PHY_RDEN, PHY_WREN, DYN_DCI, RST, TX_RST, and IBUF_DISABLE.                                      |  |  |  |  |  |  |

| Table 45                                                                                                                             | Updated description of CONTINUOUS_DQS, ODT_SRC_<0-5>, RX_GATING, TX_INIT_<0-5>, and TX_INIT_TRI.                        |  |  |  |  |  |  |

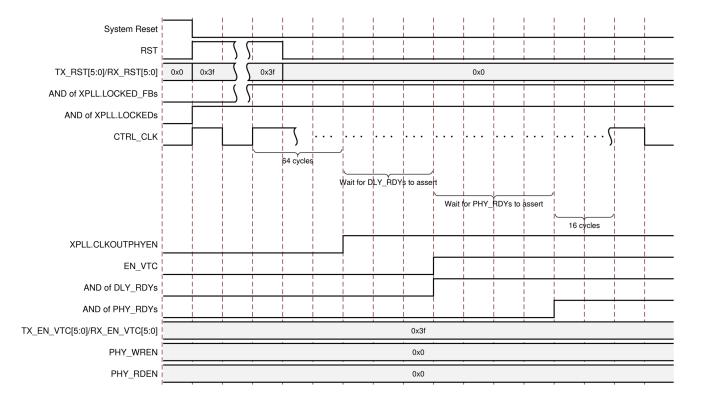

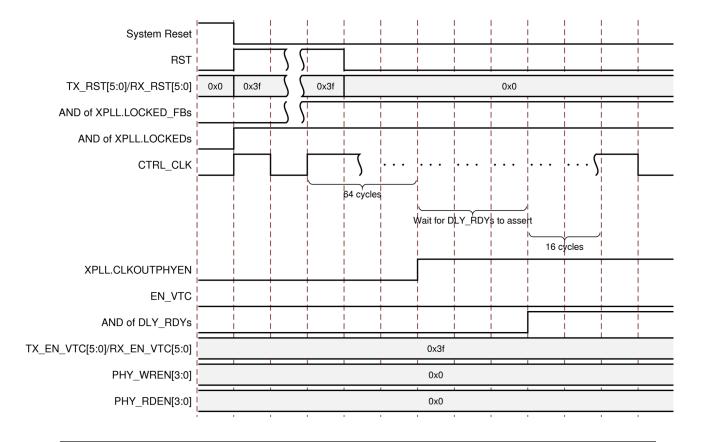

| Reset Sequence                                                                                                                       | Updated section, including both figures.                                                                                |  |  |  |  |  |  |

| XPHY Usage                                                                                                                           | Added Tcl commands to change time value of input and output delays of a NIBBLESLICE.                                    |  |  |  |  |  |  |

| Table 61, Table 62, Table 63, Table 64, Table 65, Table 66, Table 73, Table 74, Table 75, Table 76, Table 77, Table 78, and Table 79 | Removed OFFSET_CNTRL attribute.                                                                                         |  |  |  |  |  |  |

| Table 68 and Table 70                                                                                                                | Updated description of OSC[3:0], OSC_EN[1:0], and VREF.                                                                 |  |  |  |  |  |  |

| Table 73                                                                                                                             | Added VOH (DIFF_SSTL15 ONLY) attribute.                                                                                 |  |  |  |  |  |  |

| Table 76                                                                                                                             | Added note about bidirectional configuration on I/O standards.                                                          |  |  |  |  |  |  |

| Section                                      | Revision Summary                                                               |

|----------------------------------------------|--------------------------------------------------------------------------------|

| Receiver Offset Control                      | Removed section.                                                               |

| Differential Termination Attribute           | Added VCCO requirement for differential impedance block.                       |

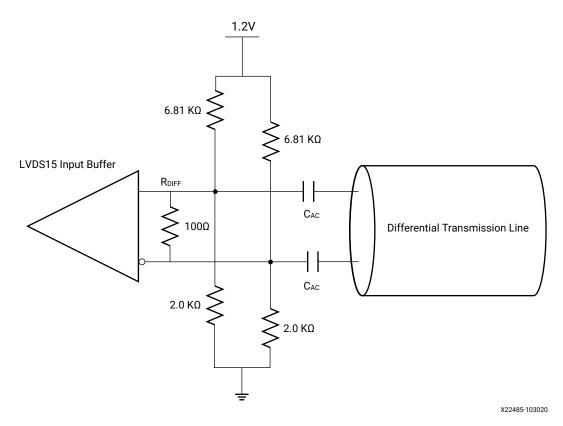

| DQS_BIAS, DC_BIAS, and AC Coupling           | Updated DC_BIAS and AC Coupling Recommendations sections.                      |

| XP IOB Pre-emphasis and Equalization         | Updated first paragraph and Table 92.                                          |

| HD IOL Features                              | Updated DPLL section.                                                          |

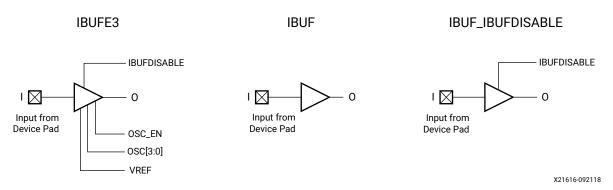

| HD IOB Primitives                            | Removed IBUF_IBUFDISABLE, IBUFDS_IBUFDISABLE, and IBUFDS_DIFF_OUT_IBUFDISABLE. |

| Single-Ended Input Buffer Primitives         | Removed IBUF_IBUFDISABLE throughout.                                           |

| Figure 66                                    | Added new figure.                                                              |

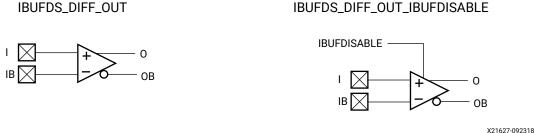

| Differential Input Buffer Primitives         | Replaced IBUFDISABLE with INTERMDISABLE throughout.                            |

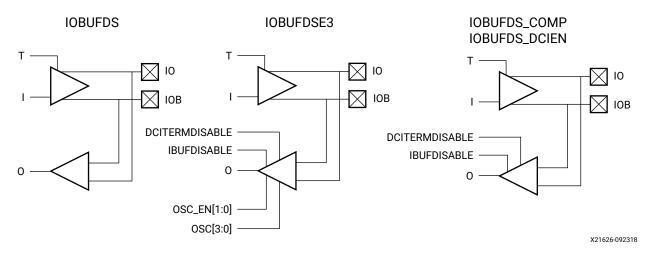

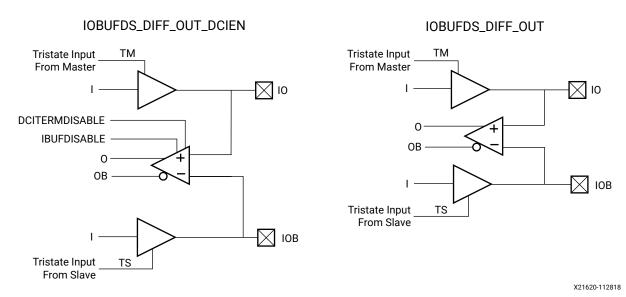

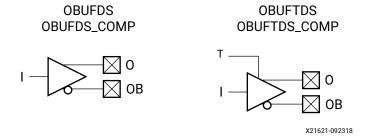

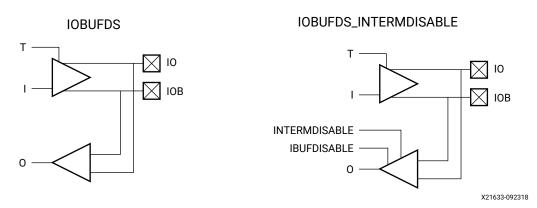

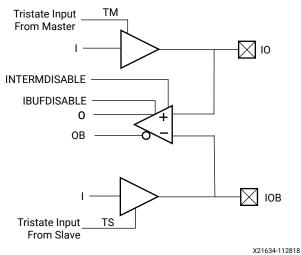

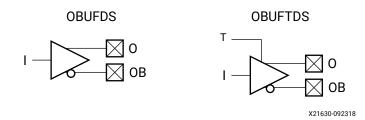

| Differential Bidirectional Buffer Primitives | Corrected primitive names throughout.                                          |

| 07/:                                         | 29/2020 Version 1.0                                                            |

| Initial release.                             | N/A                                                                            |

# **Table of Contents**

| Revision History                                               | 2        |

|----------------------------------------------------------------|----------|

| Chapter 1: Overview                                            | 6        |

| Introduction to Versal ACAP                                    |          |

| SelectIO Resources Features                                    |          |

| SelectIO Resources Architecture                                |          |

| Differences from Previous Generations                          | 12       |

| Chapter 2: XPHY Architecture                                   | 14       |

| XPHY Nibble                                                    | 14       |

| Clocking                                                       | 22       |

| XPHY Features                                                  | 28       |

| XPHY Primitive                                                 | 74       |

| XPHY Usage                                                     | 92       |

| Chapter 3: XP IOL Resources                                    | 94       |

| XP IOL Features                                                | 92       |

| Chapter 4: XP IOB Resources                                    | 106      |

| XP IOB Banking Structure                                       | 106      |

| XP IOB Supported Standards                                     | 108      |

| XP IOB Internal V <sub>REF</sub>                               | 127      |

| XP IOB Driver Control, Internal Termination, and Internal Bias | 129      |

| XP IOB IBUFDISABLE                                             |          |

| XP IOB Pre-emphasis and Equalization                           | 138      |

| Chapter 5: XP Bank Supporting Resources and Corner E           | 3anks140 |

| Clocking Resources                                             | 140      |

| Boundary Logic Interface                                       | 141      |

| Corner Banks                                                   | 142      |

| Chapter 6: HD IOL Resources                                    | 143      |

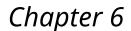

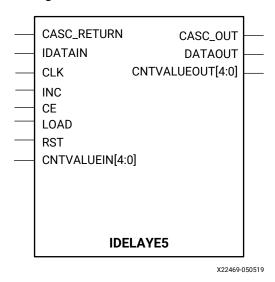

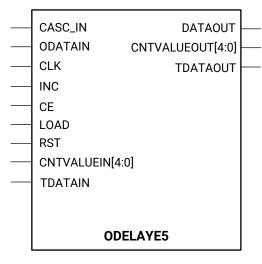

| HD IOL Features                                                | 143      |

| HD IOL Primitives                                  | 144 |

|----------------------------------------------------|-----|

| Chapter 7: HD IOB Resources                        | 150 |

| HD IOB Banking Structure                           |     |

| HD IOB Features                                    | 152 |

| HD IOB Supported Standards                         | 154 |

| Appendix A: Additional Resources and Legal Notices | 164 |

| Xilinx Resources                                   | 164 |

| Documentation Navigator and Design Hubs            | 164 |

| References                                         | 164 |

| Please Read: Important Legal Notices               | 165 |

# Overview

## Introduction to Versal ACAP

Versal<sup>™</sup> adaptive compute acceleration platforms (ACAPs) combine Scalar Engines, Adaptable Engines, and Intelligent Engines with leading-edge memory and interfacing technologies to deliver powerful heterogeneous acceleration for any application. Most importantly, Versal ACAP hardware and software are targeted for programming and optimization by data scientists and software and hardware developers. Versal ACAPs are enabled by a host of tools, software, libraries, IP, middleware, and frameworks to enable all industry-standard design flows.

Built on the TSMC 7 nm FinFET process technology, the Versal portfolio is the first platform to combine software programmability and domain-specific hardware acceleration with the adaptability necessary to meet today's rapid pace of innovation. The portfolio includes six series of devices uniquely architected to deliver scalability and Al inference capabilities for a host of applications across different markets—from cloud—to networking—to wireless communications—to edge computing and endpoints.

The Versal architecture combines different engine types with a wealth of connectivity and communication capability and a network on chip (NoC) to enable seamless memory-mapped access to the full height and width of the device. Intelligent Engines are SIMD VLIW AI Engines for adaptive inference and advanced signal processing compute, and DSP Engines for fixed point, floating point, and complex MAC operations. Adaptable Engines are a combination of programmable logic blocks and memory, architected for high-compute density. Scalar Engines, including Arm<sup>®</sup> Cortex™-A72 and Cortex-R5F processors, allow for intensive compute tasks.

The Versal AI Core series delivers breakthrough AI inference acceleration with AI Engines that deliver over 100x greater compute performance than current server-class of CPUs. This series is designed for a breadth of applications, including cloud for dynamic workloads and network for massive bandwidth, all while delivering advanced safety and security features. AI and data scientists, as well as software and hardware developers, can all take advantage of the high-compute density to accelerate the performance of any application.

The Versal Prime series is the foundation and the mid-range of the Versal platform, serving the broadest range of uses across multiple markets. These applications include 100G to 200G networking equipment, network and storage acceleration in the Data Center, communications test equipment, broadcast, and aerospace & defense. The series integrates mainstream 58G transceivers and optimized I/O and DDR connectivity, achieving low-latency acceleration and performance across diverse workloads.

The Versal Premium series provides breakthrough heterogeneous integration, very high-performance compute, connectivity, and security in an adaptable platform with a minimized power and area footprint. The series is designed to exceed the demands of high-bandwidth, compute-intensive applications in wired communications, data center, test & measurement, and other applications. Versal Premium series ACAPs include 112G PAM4 transceivers and integrated blocks for 600G Ethernet, 600G Interlaken, PCI Express® Gen5, and high-speed cryptography.

The Versal architecture documentation suite is available at: https://www.xilinx.com/versal.

## **Navigating Content by Design Process**

Xilinx® documentation is organized around a set of standard design processes to help you find relevant content for your current development task. This document covers the following design processes:

- System and Solution Planning: Identifying the components, performance, I/O, and data transfer requirements at a system level. Includes application mapping for the solution to PS, PL, and Al Engine. Topics in this document that apply to this design process include:

- Chapter 2: XPHY Architecture

- XPHY Usage

- Chapter 4: XP IOB Resources

- Chapter 7: HD IOB Resources

- Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware platform, creating PL kernels, subsystem functional simulation, and evaluating the Vivado® timing, resource use, and power closure. Also involves developing the hardware platform for system integration. Topics in this document that apply to this design process include:

- Chapter 2: XPHY Architecture

- System Integration and Validation: Integrating and validating the system functional performance, including timing, resource use, and power closure. Topics in this document that apply to this design process include:

- Chapter 2: XPHY Architecture

- Chapter 3: XP IOL Resources

- Chapter 6: HD IOL Resources

- Board System Design: Designing a PCB through schematics and board layout. Also involves power, thermal, and signal integrity considerations. Topics in this document that apply to this design process include:

- Chapter 2: XPHY Architecture

- Clocking

- Chapter 4: XP IOB Resources

- Chapter 7: HD IOB Resources

## **SelectIO Resources Features**

The two primary types of I/O in Versal ACAPs are high-performance XP I/O (XPIO) and high-density HD I/O (HDIO). The XPIO includes dedicated logic to support high-speed interfaces with voltage ranges between 1.0V and 1.5V. HDIO and XPIO banks do not have overlapping voltages or I/O standards. The HDIO supports interfaces with voltages ranging from 1.8V to 3.3V. The HDIO provides logic for both single data rate (SDR) and double data rate (DDR) interfaces at reduced clocking speeds.

#### XPIO Features

The XPIO are grouped into 54-pin banks with supporting resources for both high-performance and low-speed interfaces. Each XPIO can use the XPHY to align, serialize, and de-serialize a data stream. Each XPIO has I/O interconnect logic (IOL) resources to support low-speed SDR and DDR interfaces and coarse data alignment resources. The XPIO input and output buffers support a wide range of single-ended and differential I/O standards along with resources to support a high level of signal quality.

- 1.0V, 1.2V, 1.35V, and 1.5V bank voltage standards

- XPHY logic resources to align and serialize/de-serialize high-speed data streams

- IOL logic resources to provide simplified lower-bandwidth SDR and DDR logic support

- Internally generated V<sub>RFF</sub> support shared across nibble boundaries

- Calibrated output drive support

- Calibrated internal termination

- Internal differential termination

- Internal bias support

- Transmitter pre-emphasis and receiver equalization

- Native support for MIPI D-PHY interfaces

• Supports serialization/deserialization ratios of 1:8, 1:4, and 1:2

#### **HDIO Features**

The HDIOs are grouped into 22-pin banks with supporting resources for low-performance interfaces. Each HDIO has IOL resources to simplify the support for low-speed SDR and DDR interfaces and coarse data alignment resources. In addition to logic, the HDIO output buffers provide resources to drive single-ended and pseudo-differential standards. The HDIO input buffers can receive several single-ended and differential standards. HDIOs are optimized for single-ended, voltage-referenced, and pseudo-differential I/O standards operating at low data rates.

- IOL logic resources support low-speed interfaces with SDR and DDR logic

- IODELAY can provide up to 1.8 ns uncalibrated output delay

- IODELAY can be cascaded with output delay to provide up to 3.6 ns uncalibrated input delay

- 1.8V, 2.5V, and 3.3V bank voltage I/O standard support

- Uncalibrated output drive and slew control

- Internal V<sub>REF</sub> on a bank-wide resolution

- LVDS and LVPECL input support with external termination

# **SelectIO Resources Architecture**

All Versal™ devices have configurable SelectIO interface drivers and receivers, supporting a wide variety of standard interfaces. The robust feature set includes programmable control of output strength and slew rate, on-chip termination, and an internally generate a reference voltage (INTERNAL\_VREF). Each Versal device contain XPIO banks that contain 54 SelectIO pins and can implement both single-ended and differential I/O standards. XPIO banks support the highest speed interfaces powered at or below 1.5V. Some Versal devices contain HDIO banks that can interface with voltage levels between 1.8V and 3.3V. The HDIO banks contain 22 SelectIO pins that can implement both single-ended I/O standards and differential I/O standards. Every SelectIO IOB resource contains input, output, and tristate drivers. The SelectIO pins can be configured to various I/O standards, both single-ended and differential.

- Single-ended I/O standards are, for example, LVCMOS, LVTTL, HSTL, SSTL, HSUL, LVSTL, and POD

- Pseudo-differential standards are, for example, differential HSTL, POD, HSUL, LVSTL, and SSTL

- LVDS is the true differential standard.

#### **Related Information**

XP IOB Resources

HD IOB Resources

## Supply Voltages and Dedicated SelectIO Pins

#### $V_{CCO}$

The  $V_{CCO}$  supply is the primary power supply for drivers and termination. The XP IOB Supported Standards section includes tables that outline the  $V_{CCO}$  requirements for each of the supported I/O standards, and illustrate the  $V_{CCO}$  requirements for inputs and outputs including the optional internal differential termination circuit. All  $V_{CCO}$  pins for a given XP or HD I/O bank must be connected to the same external voltage supply on the board, and as a result, all of the I/O within a given I/O bank must be compatible with the same  $V_{CCO}$  level. The  $V_{CCO}$  voltage must match the requirements for the I/O standards that have been assigned to the I/O bank.

**CAUTION!** Incorrect  $V_{CCO}$  voltages can result in loss of functionality or damage the device.

#### $V_{CCAUX}$

The global auxiliary ( $V_{CCAUX}$ ) supply rail primarily provides power to the receive circuitry. In the I/O banks,  $V_{CCAUX}$  is also used to power input buffer circuits for some of the I/O standards. Additionally, the  $V_{CCAUX}$  rail provides power to the differential input buffer circuits used for most of the differential and  $V_{REF}$  I/O standards.

#### V<sub>CC</sub> IO

$V_{\text{CC\_IO}}$  is an internal supply for I/O banks. It supplies the digital portions and supporting logic SelectIO resources.

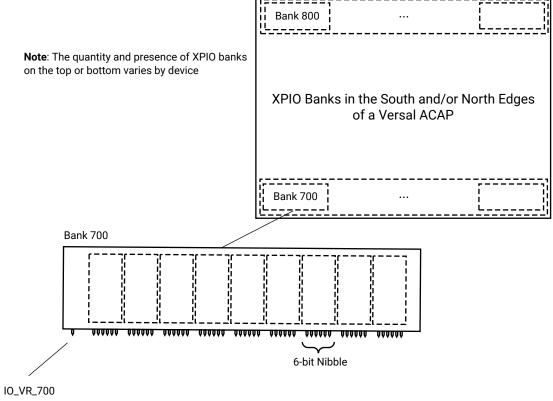

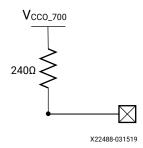

#### IO\_VR\_700 / IO\_VR\_800

In XP I/O bank 700 and bank 800 (not present in all devices), there is an additional bank pin that is used as a reference to calibrate internal on-die termination. The IO\_VR pin must be externally connected to a  $240\Omega$  resistor on the PCB and pulled up to the bank  $V_{CCO}$  voltage. See Calibrated Termination (Digitally Controlled Impedance). HD I/O banks do not support calibrated termination and thus no equivalent pin or reference resistor is required on HD I/O banks.

**IMPORTANT!** The IO\_VR\_700 and IO\_VR\_800 pins (not available on all devices) must have an external  $240\Omega$  resistor tied to VCCO\_700 and VCCO\_800 respectively. These pins are dedicated and can not be used as user I/O. All designs MUST populate these pins appropriately, regardless of the I/O standards used in a design.

#### **Power Supply Sequencing Requirements**

The power supply requirements, including power-on and power-off sequencing, are described in Versal ACAP data sheets.

# State of I/Os During and After Configuration

During configuration, I/O drivers are tristated in all banks. During configuration (until the applications settings take over), all XP I/O banks use the default IOSTANDARD = LVCMOS15, SLEW = FAST, and DRIVE = 12 mA setting. The corresponding setting in HD I/O banks is IOSTANDARD = LVCMOS25, SLEW = FAST, and DRIVE = 12 mA. The PUDC\_B input pin can be use to enable internal pull-ups during configuration. After configuration, the unused I/Os have tristated drivers, and the pads are weakly pulled-down.

**Note:** This manual applies only to PL-based HD and XP SelectIO resources. Multiplexed I/O are described in *Versal ACAP Technical Reference Manual* (AM011).

# I/O Banking Rules

In the Versal architecture, XP and HD IOBs use the bank  $V_{CCO}$  supply for drivers, on-die biasing, on-die termination, and the receive block. Because of the dependency on  $V_{CCO}$ , all outputs and many inputs must operate at a specific  $V_{CCO}$  level making it is a dominant factor in determining the IOSTANDARDS that can reside in the same bank.

#### Rules for Combining Standards Different Standards in the Same Bank

- V<sub>CCO</sub> levels must be compatible for all inputs and outputs in the same HD or XP I/O bank

- INTERNAL\_VREF levels must be compatible for all inputs in the same HD or XP I/O bank

**Note:** In Versal devices, all single-ended input and all output (single-ended and differential) IOSTANDARDS have a required  $V_{CCO}$  level. Only the differential inputs that do not use ODT, PULLTYPE, or DIFF\_TERM can reside in multiple  $V_{CCO}$  domains. Although a differential input may be compatible with multiple  $V_{cco}$  domains, it is important to note that data sheet input specifications are impacted by the  $V_{cco}$  level and compatibility should verified when selecting a  $V_{cco}$  level.

The supported standards and their associated  $V_{CCO}$  and INTERNAL\_VREF requirements are described in the XP and HD IOB supported sections.

#### **Related Information**

XP IOB Supported Standards HD IOB Supported Standards

# **Differences from Previous Generations**

Versal<sup>™</sup> ACAPs have several important feature enhancements as well as updates to existing features.

#### XP XPHY

The following table summarizes the key differences between the UltraScale™ architecture PHY and the Versal™ architecture XPHY.

*Table 1:* UltraScale Architecture PHY and Versal Architecture XPHY Key Differences

| Function                            | Versal Architecture XPHY | UltraScale Architecture PHY                                                       |  |  |  |  |

|-------------------------------------|--------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| NIBBLESLICEs per nibble             | 6                        | 6 or 7                                                                            |  |  |  |  |

| Nibbles per bank                    | 9 (54 pins)              | 8 (52 pins)                                                                       |  |  |  |  |

| Serialization                       | 8:1, 4:1, 2:1            | 8:1, 4:1                                                                          |  |  |  |  |

| Deserialization                     | 1:8, 1:4, 1:2            | 1:8, 1:4                                                                          |  |  |  |  |

| Wizard required to access interface | Yes                      | No                                                                                |  |  |  |  |

| Input and output delays             | 625 ps (512 taps)        | UltraScale devices: 1250 ps (512 taps)<br>UltraScale+ devices: 1100 ps (512 taps) |  |  |  |  |

Some of the other differences between the PHY architectures of UltraScale<sup>™</sup> and Versal devices include the following:

- Receive FIFO bypass support for low-latency applications

- No NIBBLESLICE 0 (formerly called BITSLICE 0) instantiation requirements

- The IDELAYCTRL, ISERDES, OSERDES, RXTX\_BITSLICE, RX\_BITSLICE, TX\_BITSLICE, BITSLICE\_CONTROL, and RIU\_OR UNISIM primitives are not supported

- The XP IOL features are independent of the XPHY

- Programmable logic control ports are shared between input and output delays through a delay select port

- Some XPIO banks (typically located on the corner of the device) have pins that have limited function and can only be used for DDR memory controller functionality. See the *Versal ACAP Packaging and Pinouts Architecture Manual* (AM013) for specific pin information.

- QBC and DBC functionality has been split into two parts: Strobes now enter on XCC pins, while inter-nibble and inter-byte clocking capabilities are determined by the nibble rather than the pin itself.

- The PHY can only be constructed by using the Advanced IO Wizard together with the Advanced I/O Planner (see Advanced I/O Wizard LogiCORE IP Product Guide (PG320)).

#### **XP IOL**

- The XP IOL block provides SDR and DDR logic

- IODELAY provides internal delay support of up to 3.6 ns on input (when cascaded)

- IODELAY provides internal delay support of up to 1.8 ns on output

- Unused XPHY I/O within the nibble are available to the XP IOL

- IODELAY must use the input ports to dynamically select the delay tap. DELAY\_VALUE is not supported.

#### **XP IOB**

- Banks located on the top and/or bottom periphery of the device

- Banks are groups of 54 IOBs. Each IOB is capable of both single-ended and differential signaling.

- V<sub>RFF</sub> is internally generated (only)

- DCI reference resistors are no longer required on a per bank basis (a maximum of two resistors per device)

- Output drive and termination are calibrated against the DCI reference resistor

- No support for 1.8V bank voltages. The supported bank voltages are 1.0V, 1.2V 1.35V, and 1.5V

- Output drive strength support of 4 mA, 8 mA, and 12 mA

- LVDS supported in 1.5V banks

#### **HD IOL**

- Internal input delay support of up to 3.6 ns when cascaded with the output delay or 1.8 ns when not cascaded

- Internal delay support of up to 1.8 ns on output

- Each bank has a digital PLL (DPLL)

- Static clock insertion delay compensation block through DLL (ZHOLD)

#### **HD IOB**

- Supported bank voltages of 1.8V, 2.5V, and 3.3V

- Output drive strength support of 4 mA, 8 mA, and 12 mA

- 22 pins per bank

- No class II support for SSTL standards

# XPHY Architecture

XPHY is the high-performance I/O interface on the Versal™ ACAP XPIOs. There are nine XPHY nibbles in an XPIO bank, with each XPHY nibble containing six XPHY NIBBLESLICEs that transmit and/or receive data from six individual I/O pins, for a total of 54 pins per bank. Each XPHY NIBBLESLICE is composed of a serializer, deserializer, I/O delays, and a receiver FIFO. The Versal device XPHY is equipped with voltage and temperature compensation (VTC) and a mechanism for automatic delay adjustment for optimal data eye centering through the built-in self-calibration (BISC) feature in each XPHY nibble. I/O delays can also be controlled through the programmable logic. Control of the XPHY features is available through the register interface unit (RIU) in each nibble.

XPHY is used to support the following applications:

- DDR4 and LPDDR4 integrated memory controllers supported through the IP catalog in the Vivado® tools

- DDR4, QDR IV, and RLDRAM3 memory controllers supported through the IP catalog in the Vivado tools

- MIPI D-PHY v1.2

- Gigabit Ethernet 1000Base-X and SGMII

- Toggle NAND flash

- High-speed source-synchronous and asynchronous I/O interfaces supported through the Advanced IO Wizard in the IP catalog of the Vivado tools

- IOB feed-through to programmable logic

# **XPHY Nibble**

XPHY is the high-performance I/O interface for an XPIO bank. Every XPIO bank has nine XPHY nibbles. Each XPHY nibble is defined as six XPHY NIBBLESLICEs and its associated features. XPHY NIBBLESLICEs contain input and output logic, composed of a serializer, deserializer, I/O delays, and a receiver FIFO. XPHY NIBBLESLICEs can operate as a transmitter or receiver. An XPHY nibble also performs the following functions/features:

• Built-in self-calibration (BISC) aids in alignment and uses voltage and temperature compensation (VTC) to adjust delay lines

- Generates clocks for the receiver and transmitter functions in the XPHY NIBBLESLICEs

- Gives access to the register interface unit (RIU) that provides access to all features of an XPHY nibble

- Tristate control

- TX to RX loopback

- Serial mode, which supports receiver interfaces where the clock and data phase relationship is unknown (any interface that is not source-synchronous)

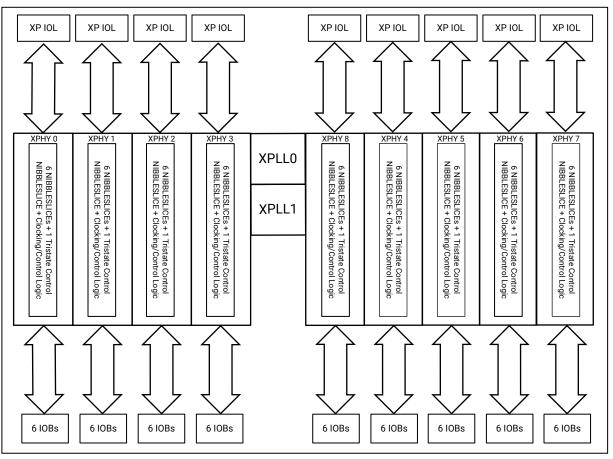

The layout of XPHY nibbles in an XPIO bank is represented in the following figure.

Figure 1: Relationship of XPHY Nibble, XP IOL, and IOB within an XPIO Bank

X21591-042319

The following figure is a detailed view of the previous figure, representing the relationship between a single XPHY nibble, XP IOL, and IOB within an XPIO bank.

XP IOL XP IOL XP IOL XP IOL XP IOL XP IOL TX Tristate Control NIBBLESLICE XPHY NIBBLESLICE 5 XPHY NIBBLESLICE 4 XPHY NIBBLESLICE 3 XPHY NIBBLESLICE 0 XPHY NIBBLESLICE 2 XPHY NIBBLESLICE IOB IOB IOB IOB IOB IOB X21592-042319

Figure 2: Relationship Between a Single XPHY Nibble, XP IOL, and IOB

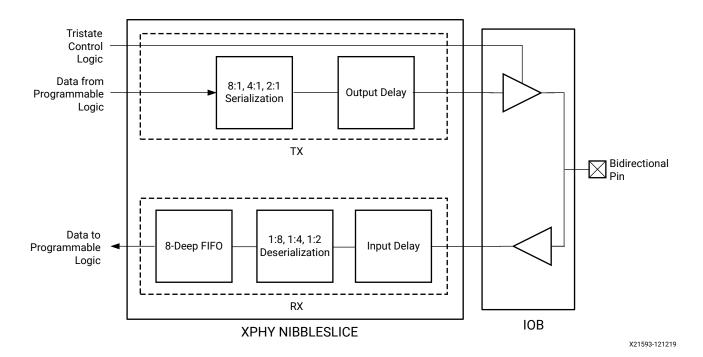

The following figure shows an XPHY NIBBLESLICE.

Figure 3: XPHY NIBBLESLICE with TX and RX Datapaths

# **TX Datapath**

The TX datapath is composed of the following:

- **Serializer:** The serializer supports 8:1, 4:1, and 2:1 serialization. This is set by the TX\_DATA\_WIDTH attribute.

- Output Delay: Output delays can delay outgoing serialized data up to 512 taps (0–511 taps), with a minimum of 625 ps of available delay.

Refer to the Controlling Tristate Control section for latencies with and without the TX datapath using tristate control.

#### **Related Information**

Controlling Delays

Controlling Tristate Control

# **RX Datapath**

The RX datapath is composed of:

- Input delay: Input delays can delay incoming serialized data up to 512 taps (0–511 taps), with a minimum of 625 ps of available delay. Input delays can be increased to 1024 taps (0–1023 taps) for a minimum of 1250 ps of available delay by cascading the output delay of an XPHY NIBBLESLICE to the end of its input delay. For more information on cascading, see the CASCADE\_<0–5> attribute.

- **Deserializer:** The deserializer supports 1:8, 1:4, and 1:2 deserialization. This is determined by the RX DATA WIDTH attribute.

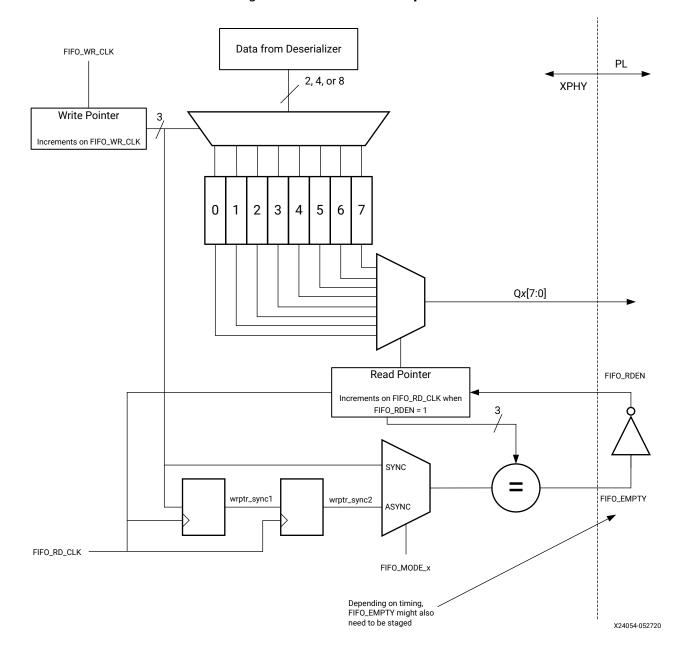

- **FIFO**: The receiver of an XPHY NIBBLESLICE has an 8-deep FIFO. The parallel data written to the FIFO is synchronized to the programmable logic clock domain of choice before passing to the programmable logic.

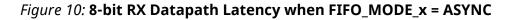

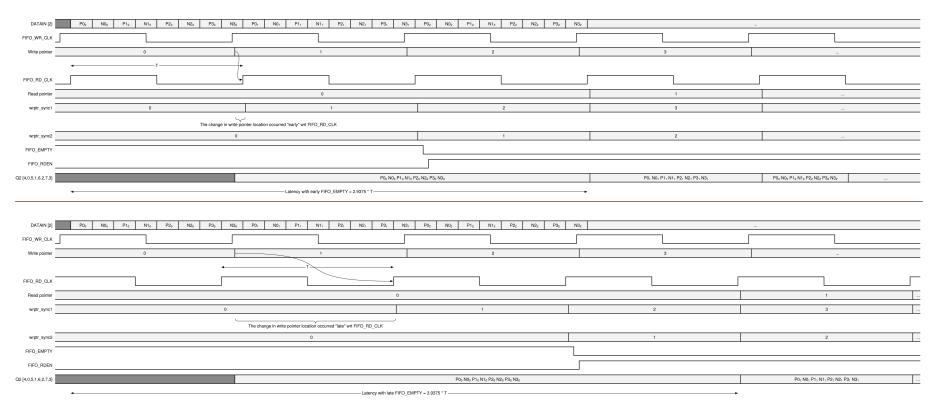

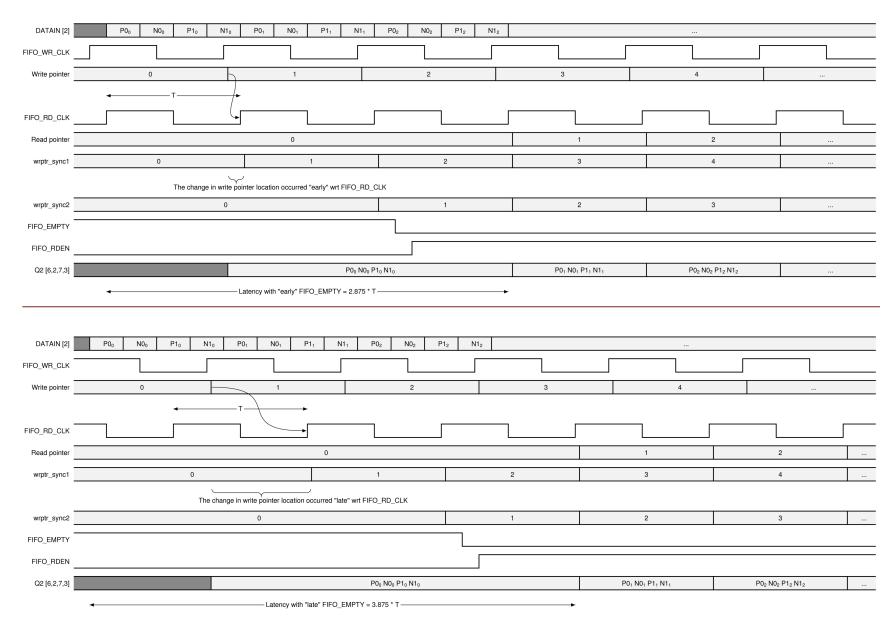

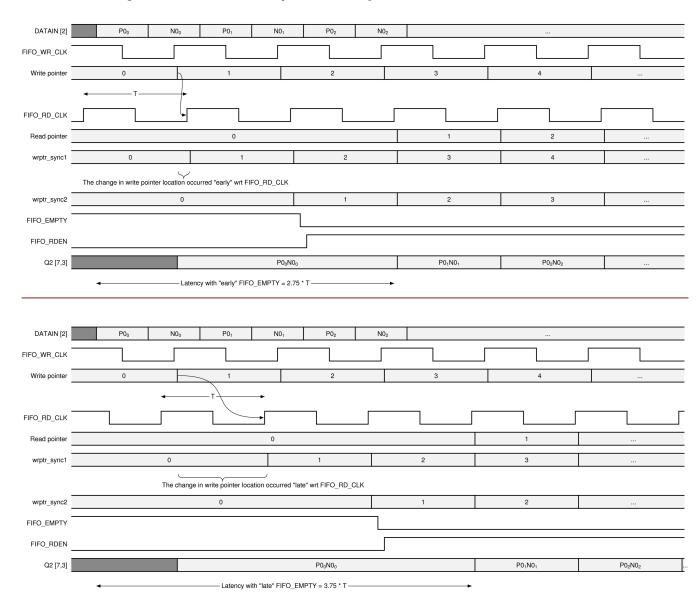

RX datapath latency changes depending on the data width (RX\_DATA\_WIDTH) and FIFO\_MODE\_x attribute. Refer to Controlling FIFO Modes for RX datapath latencies.

**IMPORTANT!** Because each NIBBLESLICE routes to a specific pin, receiving a differential signal (regardless of whether clock or data) consumes the pins and RX datapaths of both NIBBLESLICEs.

**IMPORTANT!** If receiving a strobe and RX\_GATING = ENABLE, bitslip is not needed. For all other cases, bitslip is needed for word alignment.

#### **Related Information**

**FIFO**

## **Bidirectional Datapath**

The TX and RX datapaths within each XPHY NIBBLESLICE can be used together to form a bidirectional datapath. As shown in Figure 3, each TX datapath drives both to the pad and the RX datapath. As such, care must be taken when using the bidirectional datapath so as to tristate the buffer or gate the datapaths without data loss.

The XPHY offers transmit gating, receive gating, and tristating as mechanisms to control the bidirectional datapath. See the table below for a summary of how to enable these controls through the XPHY attributes.

Table 2: Enabling Bidirectional Datapath Control

| Control Mechanism | Related Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gating            | <ul> <li>RX datapath gating:: The RX_GATING attribute enables gating of the RX datapath based on the PHY_RDEN port. While RX_GATING enables gating, the CONTINUOUS_DQS attribute lets users choose between PHY_RDEN operating based in the PLL_CLK or the strobe clock domain.</li> <li>TX datapath gating:: The TX_GATING attribute enables gating of the TX datapath based on the PHY_WREN port (which is serialized but not inverted when used for gating) and PLL_CLK ports. NIBBESLICE[1] cannot be gated.</li> </ul> |

| Tristating        | Tristating:: TBYTE_CTL_# determines whether tristating is controlled by the T (combinatorial) port or an inverted and serialized PHY_WREN port (which is in the PLL_CLK domain).                                                                                                                                                                                                                                                                                                                                           |

T\_OUT[5:0] is the tristate control output from the XPHY. Each bit of T\_OUT is associated with a NIBBLESLICE, and TBYTE\_CTL\_# allows each NIBBLESLICE to select its corresponding T\_OUT bit to be controlled by either T or PHY\_WREN. In other words for a NIBBLESLICE[x], T\_OUT[x] reflects the tristate control input selected by TBYTE\_CTL\_x. If TBYTE\_CTL\_x = T, T\_OUT[x] (associated with NIBBLESLICE[x]) is controlled via the T[x] input. Because this is a combinatorial route, T\_OUT[x] is not aligned to the data. If TBYTE\_CTL\_x = PHY\_WREN, T\_OUT[x] (associated with NIBBLESLICE[x]) is controlled through the PHY\_WREN input. This input is inverted, serialized, and output synchronously (through T\_OUT[x]) with the TX data when used for tristating. For more information, see Controlling Tristate Control.

**IMPORTANT!** When using 2:1 serialization, each NIBBLESLICE tristate buffer can only be controlled through the combinatorial T input (TBYTE\_CTL\_<0-5> = T). Tristate control through the PHY\_WREN input (TBYTE\_CTL\_ $x = PHY_WREN$ ) is only possible for 8:1 and 4:1 serialization.

PHY RDEN is set up and used to control RX datapath gating is as follows:

- PHY\_RDEN controls accepting or rejecting the strobe entering on NIBBLESLICE[0] or from

inter-byte clocking (inter-nibble clocking does not support gating through PHY\_RDEN),

depending upon the settings of CONTINUOUS\_DQS, RX\_GATING, and RX\_DATA\_WIDTH.

Always ensure the strobe has stabilized and BISC has completed before asserting PHY\_RDEN.

Refer to Controlling Built-in Self-Calibration for when BISC is considered completed.

- When RX\_DATA\_WIDTH = don't care, RX\_GATING = ENABLE, and CONTINUOUS\_DQS = TRUE, then the four bits of PHY\_RDEN are OR'd together and that output is used to control the gate. If the result of the OR operation is 1, the strobe is accepted. If it is 0, then the strobe is rejected. PHY\_RDEN is synchronized to the strobe for this attribute combination. When CONTINUOUS\_DQS = TRUE, send 3 strobe cycles before sending data.

- When RX\_DATA\_WIDTH = 4 or 8, RX\_GATING = ENABLE, and CONTINUOUS\_DQS =

FALSE, set the following bits of PHY\_RDEN to 1 to accept the strobe or 0 to reject the strobe.

PHY\_RDEN is synchronized to PLL\_CLK for this attribute combination. Each bit of PHY\_RDEN controls two UI worth of data:

- If RX\_DATA\_WIDTH = 8: [3:0]

- o If RX\_DATA\_WIDTH = 4: [2][0]

- If RX\_DATA\_WIDTH = 2: not supported

- When RX\_GATING = DISABLE the gate is always open, regardless of the value of RX\_DATA\_WIDTH, CONTINUOUS\_DQS, or PHY\_RDEN. In this scenario (RX\_GATING = DISABLE), the strobe starts the deserialization in the RX datapath. Because of this, the strobe must be stable to ensure XPHY alignment.

- When SERIAL\_MODE = TRUE, tie all four bits High

PHY\_WREN is set up and used to control TX datapath gating as follows:

- When TX\_GATING = ENABLE, PHY\_WREN gates the TX datapath of NIBBLESLICE[0], NIBBLESLICE[2], NIBBLESLICE[3], NIBBLESLICE[4], and NIBBLESLICE[5]. NIBBLESLICE[1] cannot be gated. Set the following bits of PHY\_WREN to 0 to gate transmit data or 1 to not gate transmit data:

- If TX\_DATA\_WIDTH = 8: [3:0]

- If TX\_DATA\_WIDTH = 4: [2][0]

- If TX\_DATA\_WIDTH = 2: not supported

- Note that PHY\_WREN can be used to control both TX datapath gating (if TX\_GATING = ENABLE) and tristating (if TBYTE\_CTL\_# = PHY\_WREN). However, only when PHY\_WREN is used for tristating is it inverted and serialized prior to its use. When used for gating, PHY\_WREN is serialized but is not inverted. Thus, when used for gating, PHY\_WREN should be set to 1 to open the gate and 0 to close the gate. When used for tristating, PHY\_WREN should be set to 0, which is then inverted to 1 to tristate the buffer. It follows that setting PHY\_WREN to 1 for tristating results in the buffer not being tristated. See Controlling Tristate Controlfor more information on tristating.

Other important points to keep in mind:

- When turning the bus around, toggle the BS\_RESET\_CTRL.clr\_gate bit then toggle the BS\_RESET\_CTRL.bs\_reset bit. Toggling BS\_RESET\_CTRL.clr\_gate clears the strobe path gating logic, helping to ensure proper alignment when combined with the NIBBLESLICE reset performed through the toggling of BS\_RESET\_CTRL.bs\_reset. See Register Interface Unit for more information on BS\_RESET\_CTRL. After the write to bs\_reset is completed, data can be transmitted immediately. For receivers, however, the first FIFO\_EMPTY deassertion should be used to know when receiving valid data.

- Before performing a bs\_reset, set PHY\_WREN to 0 regardless of the TX\_GATING setting.

- Setting CONTINUOUS\_DQS = TRUE requires that three strobe cycles be received prior to receiving data to prevent data loss.

- If the TX-only interface data and clock, as well as bidirectional interface data, exist in the same nibble then TBYTE\_CTL\_# must be set to T for all pins in either interface, regardless of if they are part of the TX-only interface or bidirectional interface, and TX\_GATING must be set to DISABLE

- If the TX-only interface clock is placed in NIBBLESLICE[1], TX\_GATING can be set to ENABLE because NIBBLESLICE[1] cannot be gated. In this scenario, TBYTE\_CTL\_# should be set to PHY\_WREN for the bidirectional pins in the nibble, and TBYTE\_CTL\_# should be set to T for the TX-only pins in the nibble. If the TX-only interface clock is not placed on NIBBLESLICE[1], TX\_GATING must be set to DISABLE, and TBYTE\_CTL\_# must be set to T for all pins in the interfaces, regardless of whether they are TX-only or bidirectional.

- When TX\_DATA\_WIDTH = 2 or RX\_DATA\_WIDTH = 2, bidirectional support is limited to:

- TX\_GATING must be set to DISABLE.

- RX\_GATING can be set to ENABLE, but only when CONTINUOUS\_DQS is also set to TRUE.

- Tristating is only supported through the T port (TBYTE\_CTL\_# = T).

To perform a clr\_gate and bs\_reset sequence to turn the bus around, do the following:

- Assert BS\_RESET\_CTRL.clr\_gate through the RIU.

- 2. Deassert BS\_RESET\_CTRL.clr\_gate through the RIU. The strobe path gating logic is now clear.

- 3. If PHY\_WREN has not already been set to 0, it must be set to 0 before continuing with this step. Assert BS\_RESET\_CTRL.bs\_reset, which resets NIBBLESLICEs not masked by BS\_RST\_MASK.bs\_reset\_mask. While bs\_reset is asserted, the TX IOBs of NIBBLESLICEs not masked by BS\_RST\_MASK.bs\_reset\_mask are set to the value of their associated TX\_INIT\_# attribute. Keep BS\_RESET\_CTRL.bs\_reset asserted for a minimum number of clock cycles based on the TX\_DATA\_WIDTH and RX\_DATA\_WIDTH attributes:

- For data width of 8: 1 CTRL\_CLK cycle + 72 PLL\_CLK cycles

- For data width of 4: 1 CTRL\_CLK cycle + 40 PLL\_CLK cycles

- For data width of 2: 1 CTRL CLK cycle + 24 PLL CLK cycles

- 4. Deassert BS\_RESET\_CTRL.bs\_reset. After the write to bs\_reset is completed, data can be transmitted immediately. For receivers, however, the first FIFO\_EMPTY deassertion should be used to know when receiving valid data.

**IMPORTANT!** If receiving a strobe and RX\_GATING = ENABLE, bitslip is not needed. For all other cases, bitslip is needed for word alignment.

#### **Related Information**

**Controlling Tristate Control**

# Clocking

Each XPIO bank has two XPLLs. Each XPLL has four user-controlled clock outputs (XPLL.CLKOUT<0-3>) to the programmable logic (PL) and a dedicated, high-speed clock connection (XPLL.CLKOUTPHY) to all XPHY nibbles in an XPIO bank. For more information on XPLLs, see the *Versal ACAP Clocking Resources Architecture Manual* (AM003). The following tables summarize XPHY clocking ports and attributes. For more complete descriptions, see Ports and Attributes.

Table 3: XPHY Clocks

| Clock                | I/O                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL_CLK              | Input                     | Clocks the XPHY interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CTRL_CLK             | Input                     | RIU/delay line/BISC clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FIFO_RD_CLK          | Input                     | The FIFO read clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLK_FROM_OTHER_XPHY  | Input                     | Inter-byte clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NCLK_NIBBLE_IN       | Input                     | N-clk input for inter-nibble clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PCLK_NIBBLE_IN       | Input                     | P-clk input for inter-nibble clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FIFO_WR_CLK          | Output                    | The FIFO write clock. Generated internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLK_TO_LOWER         | Output                    | Inter-byte clock output to certain numerically lower nibbles (with one exception to a numerically higher nibble).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLK_TO_UPPER         | Output                    | Inter-byte clock output to certain numerically higher nibbles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NCLK_NIBBLE_OUT      | Output                    | N-clk output for inter-nibble clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PCLK_NIBBLE_OUT      | Output                    | P-clk output for inter-nibble clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Strobe/Capture clock | Input (RX)<br>Output (TX) | Strobes/capture clocks can be received through the IOB to NIBBLESLICE[0] or through internibble/inter-byte clocking. Within the XPHY the strobe is separated into a p-clk and n-clk, which then can be used for inter-nibble clocking and data capture.  For source-synchronous receive interfaces (implying SERIAL_MODE = FALSE), the strobe/capture clock is received with the data with a known phase relationship. For other receive interfaces (implying SERIAL_MODE = TRUE), the capture clock is generated within the XPHY from PLL_CLK. Internibble and inter-byte clocking aren't supported when SERIAL_MODE = TRUE |

**Table 4: Clocking Connections**

| Clock                               | I/O                                                                         | Connection (TX)                                                                                                 | Connection (RX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PLL_CLK                             | Input                                                                       | XPLL.CLKOUTPHY                                                                                                  | XPLL.CLKOUTPHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| CTRL_CLK                            | Input                                                                       | Does not need to come from a specific clock source                                                              | Does not need to come from a specific clock source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| FIFO_RD_CLK                         | Input                                                                       | -                                                                                                               | Depends on FIFO_MODE_x. Refer to Controlling FIFO Modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| CLK_FROM_OTHER_XPHY                 | Input                                                                       | -                                                                                                               | If receiving an inter-byte clock, connect to the applicable CLK_TO_LOWER or CLK_TO_UPPER of the source nibble sending the interbyte clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| PCLK_NIBBLE_IN,<br>NCLK_NIBBLE_IN   | Input                                                                       | -                                                                                                               | If receiving inter-nibble clocks, connect PCLK_NIBBLE_OUT of the source nibble to PCLK_NIBBLE_IN of the destination nibble. Do the same for NCLK_NIBBLE_OUT and NCLK_NIBBLE_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| FIFO_WR_CLK                         | Output                                                                      | -                                                                                                               | Generated internally from the strobe or in the case of SERIAL_MODE = TRUE, from PLL_CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| CLK_TO_LOWER,<br>CLK_TO_UPPER       | Output                                                                      | -                                                                                                               | If sending an inter-byte clock, connect the applicable CLK_TO_LOWER or CLK_TO_UPPER of the source nibble to CLK_FROM_OTHER_XPHY of the destination nibble receiving the inter-byte clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| PCLK_NIBBLE_OUT,<br>NCLK_NIBBLE_OUT | Output                                                                      | -                                                                                                               | If sending inter-nibble clocks, connect PCLK_NIBBLE_OUT of the source nibble to PCLK_NIBBLE_IN of the destination nibble. Do the same for NCLK_NIBBLE_OUT and NCLK_NIBBLE_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Strobe/Capture clock                | Output or input, depending on which perspective- RX (input) or TX (output). | Send through one of the D<0-5> inputs, after which it will be output to the IOB by the corresponding O0[x] bit. | For source-synchronous interfaces, a strobe/capture clock must be received by NIBBLESLICE[0] (DATAIN[0]), inter-nibble clocking (see Table 3 for the ports), or interbyte clocking (see Table 3 for the ports). If a strobe/capture clock is received on NIBBLESLICE[0], regardless of whether it is single-ended or differential, DELAY_VALUE_0 (and only DELAY_VALUE_0) must be set to 0. If a source-synchronous interface spans multiple nibbles, inter-nibble and/or inter-byte clocking can be used to forward the strobe.  If SERIAL_MODE = TRUE, the capture clock is generated from the PLL_CLK input for each nibble and interbyte clocking are not supported when SERIAL_MODE = TRUE. |  |  |  |  |  |

**Table 5: XPHY Clocking Attributes**

| Attribute                         | Description                                                                                                                                                                           |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTINUOUS_DQS                    | Along with RX_GATING, determines if and how the strobe is gated.                                                                                                                      |

| DQS_SRC                           | Determines where the strobe is being received from (NIBBLESLICE[0], inter-nibble clocking, inter-byte clocking, or PLL_CLK for serial mode).                                          |

| EN_CLK_TO_LOWER                   | Enables outputting the strobe to certain numerically lower nibbles (inter-byte clocking).                                                                                             |

| EN_CLK_TO_UPPER                   | Enables outputting the strobe to certain numerically higher nibbles (inter-byte clocking).                                                                                            |

| EN_OTHER_NCLK                     | Enables sourcing the n-side of the strobe from inter-nibble clocking.                                                                                                                 |

| EN_OTHER_PCLK                     | Enables sourcing the p-side of the strobe from inter-nibble clocking.                                                                                                                 |

| INV_RXCLK                         | Inverts the incoming strobe to NIBBLESLICE[0].                                                                                                                                        |

| REFCLK_FREQUENCY                  | Set to the frequency of PLL_CLK.                                                                                                                                                      |

| RX_CLK_PHASE_P,<br>RX_CLK_PHASE_N | Controls strobe (p-clk and n-clk in this case) centering for source-synchronous interfaces.                                                                                           |

| RX_GATING                         | Along with CONTINUOUS_DQS, determines if and how the strobe is gated.                                                                                                                 |

| TX_GATING                         | Uses PHY_WREN to gate the transmit data and/or outgoing strobe/capture clock. NIBBLESLICE[1] cannot be affected by TX_GATING.                                                         |

| TX_OUTPUT_PHASE_90_<0-5>          | Used to center the strobe/capture clock to data on the transmitter side. Applied to the NIBBLESLICE(s) sending the strobe/capture clock, causing it to be center-aligned to the data. |

**IMPORTANT!** The phase detector in the XPLL should be used for all PL-XPHY TX interfaces. If the interface spans multiple banks, only the phase detector in the XPLL providing the clock to the PL should be used. Refer to Versal ACAP Clocking Resources Architecture Manual (AM003) for more information.

While transmit interface clocking is sourced from XPLLs, receiver clocking for source-synchronous interfaces can take advantage of inter-nibble and inter-byte clocking for forwarding the strobe. If an interface spans more than one nibble, then inter-nibble and/or inter-byte clocking can be used to route the strobe to other nibbles:

- Inter-nibble clocking is supported within nibble-pairs, as shown in the following figure. Nibble-pairs are XPHY nibbles (0,1), (2,3), (4,5), and (6,7)

- Inter-byte clocking is supported between specific XPHY nibbles within an XPIO bank, as shown in the table below. While inter-nibble clocking can only occur between two nibbles, inter-byte clocking can forward a strobe further by using each nibble receiving the inter-byte clock to also forward it. Nibbles receiving a clock through inter-byte clocking can generate an inter-nibble clock, though nibbles receiving an inter-nibble clock cannot use it to generate an inter-byte clock. CLK\_FROM\_OTHER\_XPHY of the source nibble starting the inter-byte clocking should be set to 1 ' b1.

- XPHY nibble 8 is not part of a nibble-pair and thus is not capable of inter-nibble clocking, but

can receive an inter-byte clock from XPHY nibble 6. Use CLK\_TO\_LOWER when performing

inter-byte clocking from XPHY nibble 6 to XPHY nibble 8. This is the exception to the

CLK\_TO\_LOWER/CLK\_TO\_UPPER naming scheme.

- When SERIAL\_MODE = TRUE, inter-nibble/byte clocking is not supported. Instead, each nibble generates its own capture clock from the PLL\_CLK input.

- Inter-nibble and inter-byte clocking can only occur between nibbles in the same bank and cannot be connected to the programmable logic (PL).

- Inter-byte clocking is received/sent before the coarse and quarter delays. Thus, an inter-byte clock passes through both delay blocks in the destination nibble, and neither of them in the source nibble.

- Inter-nibble clocking is received/sent after the coarse delay, but before the quarter delay. Thus, an inter-nibble clock passes through the coarse delay in the source nibble, and the quarter delay in the destination nibble.

- NIBBLESLICEs are aligned to each other (assuming BISC is being used), but word alignment is not guaranteed. Using inter-byte clocking can further negatively affect word alignment.

XPLL placement in the following figure is representative, the XPLL locations varies (with respect to nibbles).

Inter-nibble clocking MUX FIFO\_WR\_CLK -IFO\_WR\_CLK FIFO\_WR\_CLK -IFO\_WR\_CLK "IFO\_WR\_CLK XPHY 3 XPHY 8 XPHY 5 XPHY 0 XPHY 1 XPHY 2 XPHY 4 XPHY 6 XPHY 7 **XPLL XPLL** xcc/gc Inter-byte clocking MUX ONLY GCs can route to PLLs

Figure 4: Inter-nibble and Inter-byte Clocking Within an XPIO Bank

X21607-102319

The figure above has been translated into a table, as follows.

Table 6: Inter-byte and Inter-nibble Clocking in an XPIO Bank

| XPHY Nibble | Can Route To (Through<br>Inter-nibble Clocking) | Can Route To (Through<br>Inter-byte Clocking) | Can Route To (Through<br>Inter-byte, Inter-<br>nibble, or a<br>Combination of the<br>Two) |  |  |  |

|-------------|-------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|

| 0           | 1                                               | •                                             | 1                                                                                         |  |  |  |

| 1           | 0                                               | -                                             | 0                                                                                         |  |  |  |

| 2           | 3                                               | 0, 4                                          | 0, 1, 3, 4, 5, 6, 7, 8                                                                    |  |  |  |

Table 6: Inter-byte and Inter-nibble Clocking in an XPIO Bank (cont'd)

| XPHY Nibble | Can Route To (Through<br>Inter-nibble Clocking) | Can Route To (Through<br>Inter-byte, Inter-<br>nibble, or a<br>Combination of the<br>Two) |                        |  |  |

|-------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------|--|--|

| 3           | 2                                               | 1, 5                                                                                      | 0, 1, 2, 4, 5, 6, 7    |  |  |

| 4           | 5                                               | 2, 6                                                                                      | 0, 1, 2, 3, 5, 6, 7, 8 |  |  |

| 5           | 4                                               | 3, 7                                                                                      | 0, 1, 2, 3, 4, 6, 7    |  |  |

| 6           | 7                                               | 8                                                                                         | 7, 8                   |  |  |

| 7           | 6                                               | -                                                                                         | 6                      |  |  |

| 8           | -                                               | -                                                                                         | -                      |  |  |

As shown in the clocking figures, within a bank there are two types of clock inputs that serve two different purposes:

- Global Clock (GC): Clock input with dedicated clock routing designed to have low skew, low

duty cycle distortion, and improved jitter resistance. As such, it is recommended for external

clocks to enter through GC pins. For interfaces that use XPHY, the GC pins are typically used

as the clock source for the XPLLs, which in turn clock the XPHY. GCs can reach all XPLLs in an

XPIO bank as well as XPLLs in the adjacent banks.

- XCC: Strobe input for XPHY receive interfaces

- Both GC and XCC: These pins can act as GCs and/or XCCs

**Note:** If a GC, XCC, or GC/XCC input is not used to receive a clock or strobe, it can be used as a regular I/O pin.

Refer to Versal ACAP Clocking Resources Architecture Manual (AM003) for a more detailed explanation of GC and XCC pins.

The following figure shows the XCC and GC pins that can accept a clock and the NIBBLESLICEs with which they are associated. Clocks entering on GC or XCC inputs (as opposed to data entering on those pins), regardless of whether single-ended or differential, must enter NIBBLESLICE[0]. If the clock is differential, the complementary side of the clock can be sent to NIBBLESLICE[1], though it is not routed to the GC or XCC circuitry and instead goes through the normal RX datapath. Recall that because each NIBBLESLICE routes to a specific pin, receiving a differential signal (regardless of whether clock or data) consumes the pins and RX datapaths of both NIBBLESLICEs. When NIBBLESLICE[0] receives a clock, it is routed through the GC and/or XCC circuitry (depending on its usage and the capabilities of the pin) and the normal RX datapath.

Figure 5: Relationship of XCC and GC Pins to XPHY NIBBLESLICES

|                                                           | Nibble      | 0                         |     | 1    |     | 2             |     | 3 X  |           |     | 8      | 4   |        | 4   |  | 4 5 |  | 6   |  | 7 |  |

|-----------------------------------------------------------|-------------|---------------------------|-----|------|-----|---------------|-----|------|-----------|-----|--------|-----|--------|-----|--|-----|--|-----|--|---|--|

| \[\begin{array}{c} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ | IIBBLESLICE | 012345 012345 012345 0123 |     | 2345 |     | 012345 012345 |     | 2345 | 45 012345 |     | 012345 |     | 012345 |     |  |     |  |     |  |   |  |

|                                                           |             | XCC                       | XCC |      | XCC |               | XCC |      |           | XCC |        | xcc |        | XCC |  | XCC |  | xcc |  |   |  |

|                                                           |             |                           |     |      | GC  |               | GC  |      |           | GC  |        | GC  |        |     |  |     |  |     |  |   |  |

X21609-071520

Because there are two XPLLs per bank, one bank can support two data rates. Source-synchronous (implying SERIAL\_MODE = FALSE) and SERIAL\_MODE = TRUE interfaces can exist in the same bank, but each nibble in its respective interface must be configured as only source-synchronous or only SERIAL\_MODE = TRUE.

### **XPHY Features**

## **Delays**

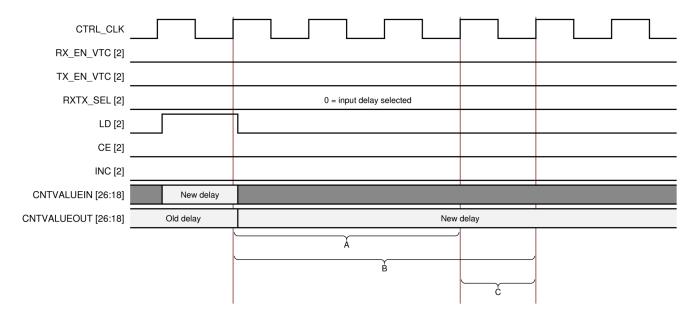

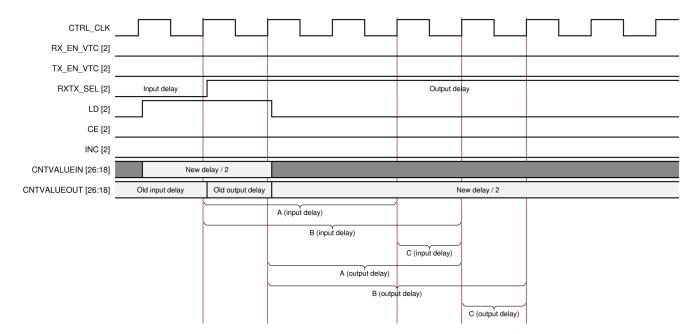

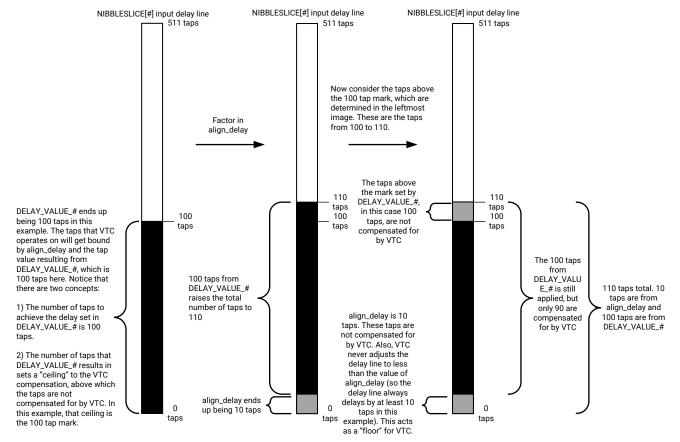

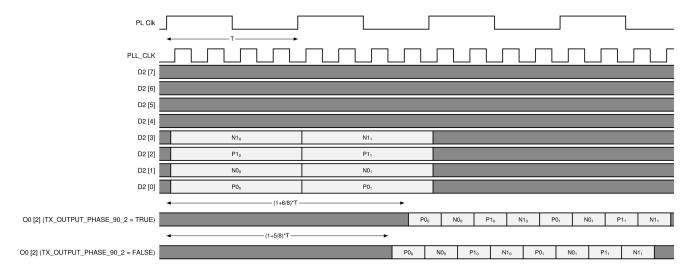

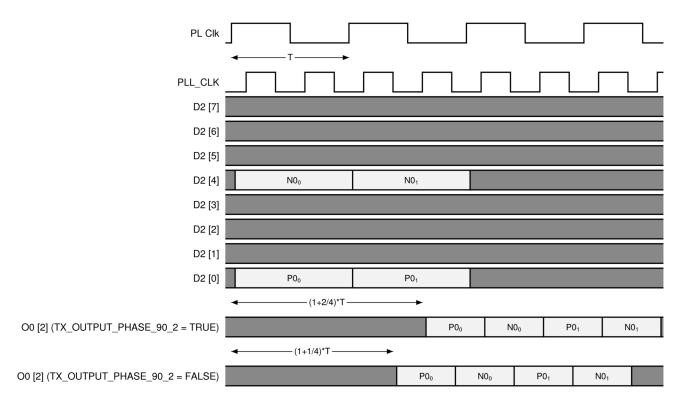

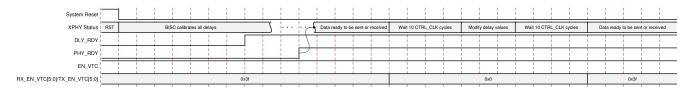

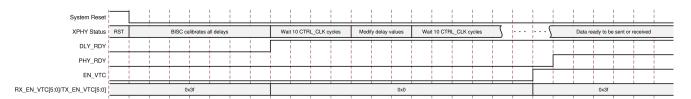

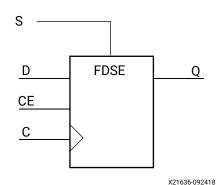

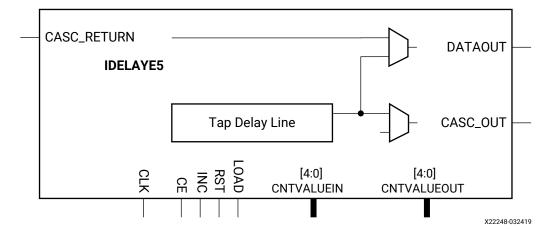

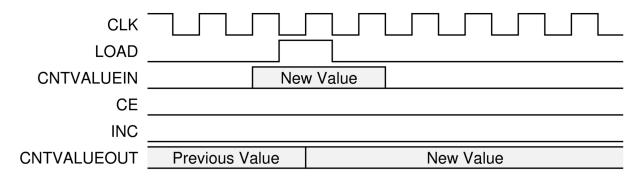

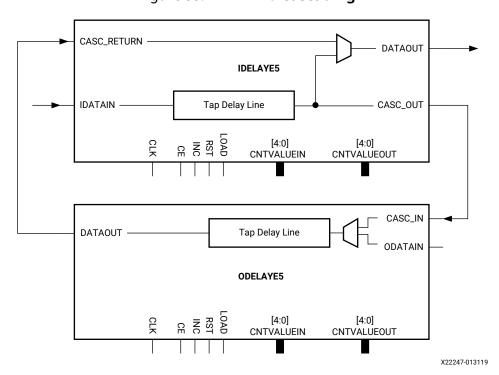

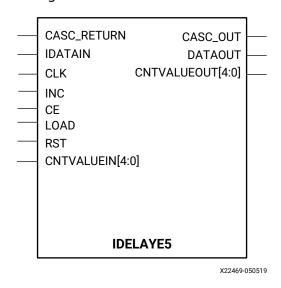

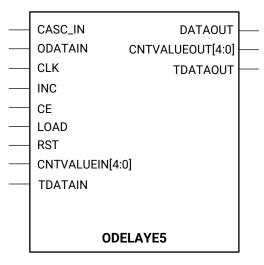

Four types of delays exist within an XPHY. However, only input and output delays can be changed through the programmable logic (PL), using CE, INC, LD, CNTVALUEIN, and RXTX\_SEL to do so.

**Note:** A tap is the smallest amount of delay that a delay line can produce. For information on tap specifications, see *Versal AI Core Series Data Sheet: DC and AC Switching Characteristics* (DS957).