# Vitis Model Composer Tutorial

UG1498 (v2021.1) July 16, 2021

## **Revision History**

The following table shows the revision history for this document.

| Section                             | Revision Summary                                   |

|-------------------------------------|----------------------------------------------------|

| 07/16/2021 Version 2021.1           |                                                    |

| Document Title and Revision Summary | Title changed to ''Vitis Model Composer Tutorial'' |

| General updates                     | Updated for release 2021.1                         |

## Locating the Tutorial Design Files

There are separate project files and sources for each of the labs in this tutorial. Download the reference design files for this tutorial from the Xilinx website, then extract the zip file contents into any write-accessible location on your hard drive or network location.

#### **RECOMMENDED:**

You will modify the tutorial design data while working through this tutorial. You should use a new copy of the directory extracted from ug1498-mode1-composer-sys-gen-tutorial. zip each time you start this tutorial.

### **Table of Contents**

| Revision History                                              |     |

|---------------------------------------------------------------|-----|

| Locating the Tutorial Design Files                            | 3   |

| Chapter 1: HDL Library                                        | 5   |

| Lab 1: Introduction to Model Composer HDL Library             | 5   |

| Lab 2: Importing Code into Model Composer HDL Design          | 40  |

| Lab 3: Timing and Resource Analysis                           | 57  |

| Lab 4: Working with Multi-Rate Systems                        | 67  |

| Lab 5: Using AXI Interfaces and IP Integrator                 | 81  |

| Lab 6: Using a Model Composer HDL Design with a Zynq-7000 SoC | 91  |

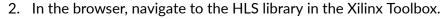

| Chapter 2: HLS Library                                        | 102 |

| Lab 1: Introduction to Model Composer HLS Library             |     |

| Lab 2: Importing Code into Model Composer                     | 112 |

| Lab 3: Debugging Imported C/C++-Code Using GDB Debugger       | 121 |

| Lab 4: Automatic Code Generation                              | 129 |

| Chapter 3: AI Engine Library                                  | 142 |

| Model Composer for AI Engine Lab Overview                     |     |

| Lab 1: Importing AI Engine Kernels                            | 143 |

| Lab 2: Importing AI Engine Graphs                             | 152 |

| Appendix A: Additional Resources and Legal Notices            | 158 |

| Xilinx Resources                                              |     |

| Documentation Navigator and Design Hubs                       | 158 |

| References                                                    |     |

| Please Read: Important Legal Notices                          | 159 |

### **HDL** Library

## Lab 1: Introduction to Model Composer HDL Library

In this lab, you will learn how to use Model Composer HDL library to specify a design in Simulink® and synthesize the design into an FPGA. This tutorial uses a standard FIR filter and demonstrates how Model Composer provides you the design options that allow you to control the fidelity of the final FPGA hardware.

#### **Objectives**

After completing this lab, you will be able to:

- Capture your design using the Model Composer HDL Blocksets.

- Capture your designs in either complex or discrete Blocksets.

- Synthesize your designs in an FPGA using the Vivado® Design Environment.

#### **Procedure**

This lab has four primary parts:

- **Step 1:** Review an existing Simulink design using the Xilinx® FIR Compiler block, and review the final gate level results in Vivado.

- **Step 2:** Use over-sampling to create a more efficient design.

- **Step 3:** Design the same filter using discrete blockset parts.

- Step 4: Understand how to work with Data Types such as Floating-point and Fixed-point.

#### Step 1: Creating a Design in an FPGA

In this step, you learn the basic operation of Model Composer and how to synthesize a Simulink design into an FPGA.

- 1. Invoke Vitis Model Composer.

- On Windows systems, select Windows → Xilinx Design Tools → Vitis Model Composer 202x.x.

- On Linux systems, type model\_composer at the command prompt.

- 2. Navigate to the Lab1 folder: \HDL\_Library\Lab1.

You can view the directory contents in the MATLAB® Current Folder browser, or type 1s at the command line prompt.

- 3. Open the Lab1\_1 design as follows:

- a. At the MATLAB command prompt, type open Lab1\_1.slx OR

- b. Double-click Lab1\_1.slx in the Current Folder browser.

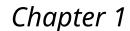

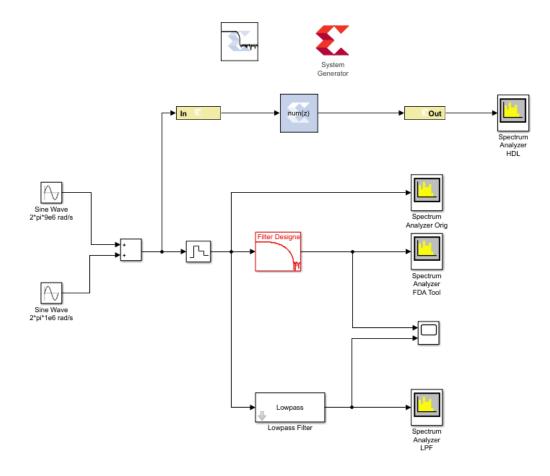

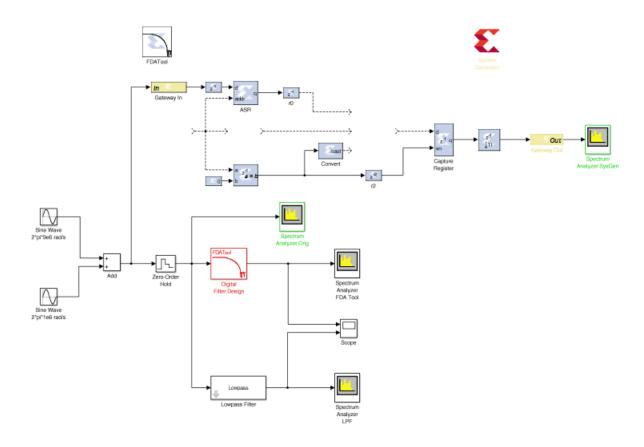

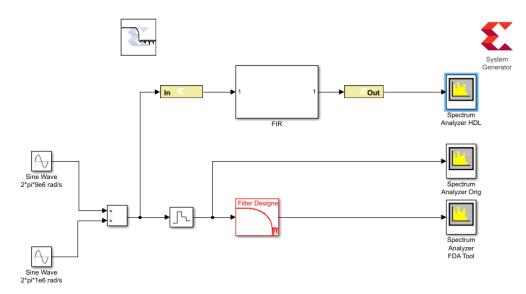

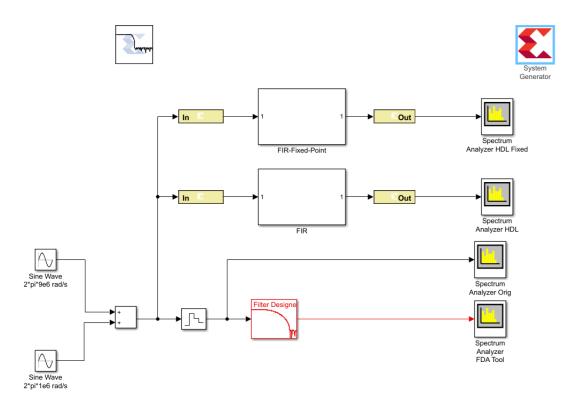

The Lab1\_1 design opens, showing two sine wave sources being added together and passed separately through two low-pass filters. This design highlights that a low-pass filter can be implemented using the Simulink FDATool or Lowpass Filter blocks.

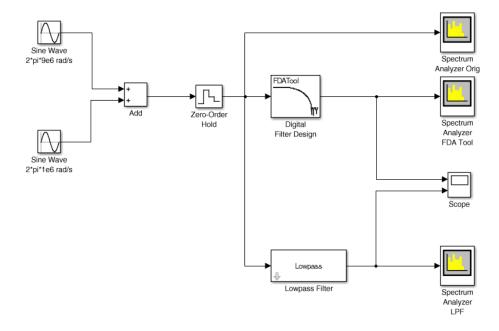

4. From your Simulink project worksheet, select **Simulation** → **Run** or click the **Run** simulation button.

When simulation completes you can see the spectrum for the initial summed waveforms, showing a 1 MHz and 9 MHz component, and the results of both filters showing the attenuation of the 9 MHz signals.

You will now create a version of this same filter using HDL blocks for implementation in an FPGA.

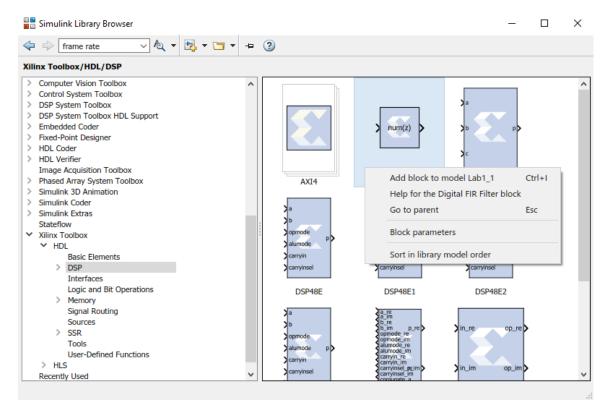

5. Click the **Library Browser** button in the Simulink toolbar to open the Simulink Library Browser.

When using Model Composer, the Simulink library includes specific blocks for implementing designs in an FPGA. You can find a complete description of the HDL library blocks provided by Model Composer in the *Vitis Model Composer Tutorial* (UG1498).

- 6. Expand the Xilinx Toolbox → HDL menu, select DSP, then select Digital FIR Filter.

- 7. Right-click the **Digital FIR Filter** block and select **Add block to model Lab1\_1**.

You can define the filter coefficients for the Digital FIR Filter block by accessing the block attributes-double-click the **Digital FIR Filter** block to view these-or, as in this case, they can be defined using the FDATool.

From Xilinx Toolbox → HDL → Tools, select FDATool and add it to the Lab1\_1 design.

An FPGA design requires three important aspects to be defined:

- The input ports

- The output ports

- The FPGA technology

The next three steps show how each of these attributes is added to your Simulink design.

**IMPORTANT!** If you fail to correctly add these components to your design, it cannot be implemented in an FPGA. Subsequent labs will review in detail how these blocks are configured; however, they must be present in all Model Composer HDL designs.

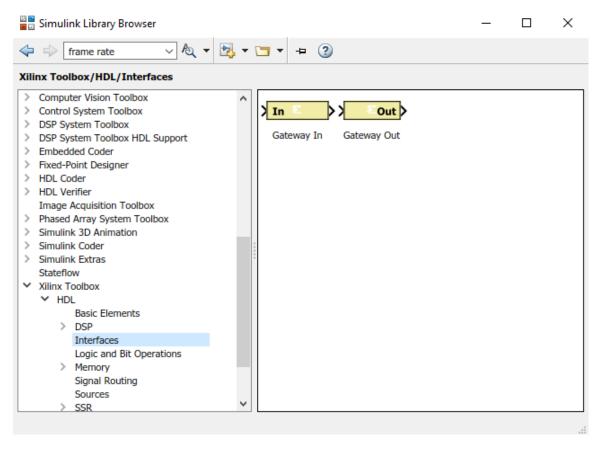

9. In the Interfaces menu, select **Gateway In**, and add it to the design.

- 10. Similarly, from the same menu, add a Gateway Out block to the design.

- 11. From the Tools menu, under the HDL menu, add the System Generator token used to define the FPGA technology.

- 12. Finally, make a copy of one of the existing Spectrum Analyzer blocks, and rename the instance to Spectrum Analyzer HDL by clicking the instance name label and editing the text.

- 13. Connect the blocks as shown in the following figure. Use the left-mouse key to make connections between ports and nets.

The next part of the design process is to configure the HDL blocks.

#### Configure the HDL Blocks

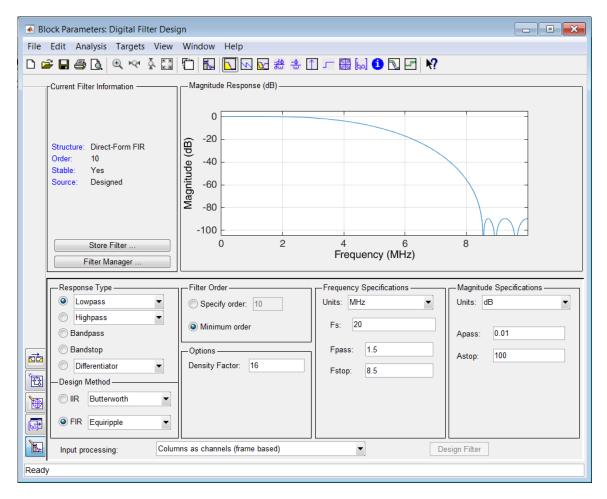

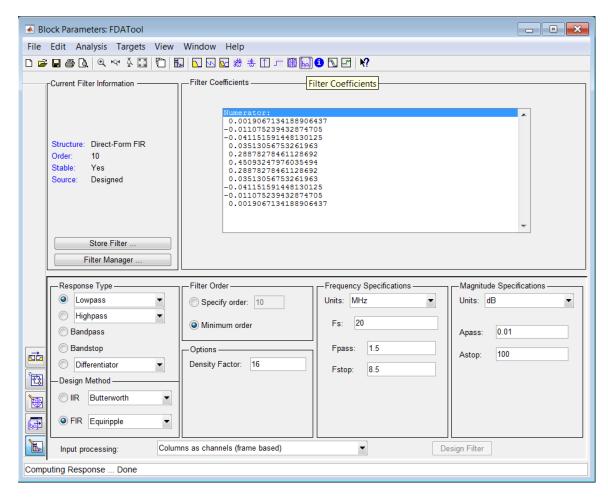

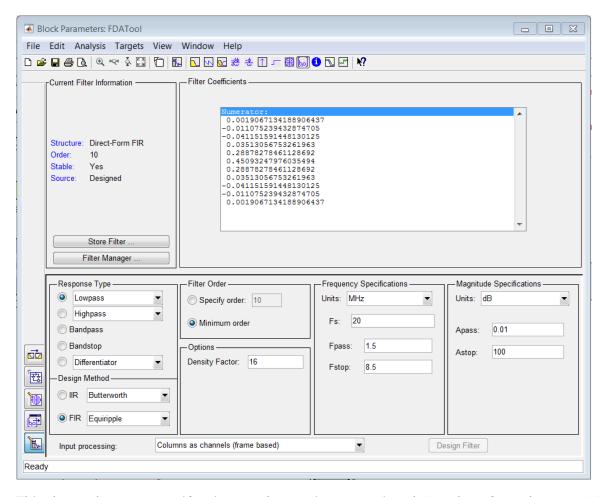

The first task is to define the coefficients of the new filter. For this task you will use the Xilinx block version of FDATool. If you open the existing FDATool block, you can review the existing Frequency and Magnitude specifications.

1. Double-click the **Digital Filter Design** instance to open the Properties Editor.

This allows you to review the properties of the existing filter.

- 2. Close the Properties Editor for the Digital Filter Design instance.

- 3. Double-click the **FDATool** instance to open the Properties Editor.

- 4. Change the filter specifications to match the following values:

- Frequency Specifications

- 。 Units = MHz

- 。Fs = 20

- Fpass = 1.5

- Fstop = 8.5

- Magnitude Specifications

- . Units = dB

- . Apass = 0.01

- . Astop = 100

- 5. Click the **Design Filter** button at the bottom and close the Properties Editor.

Now, associate the filter parameters of the FDATool instance with the Digital FIR Filter instance.

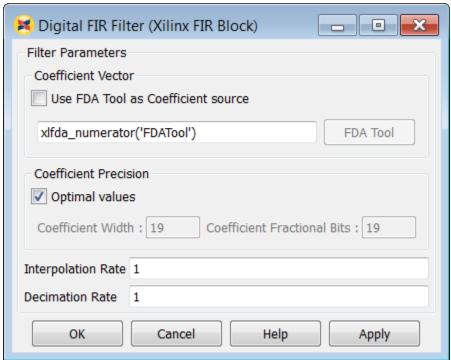

- 6. Double-click the **Digital FIR Filter** instance to open the Properties Editor.

- 7. In the Filter Parameters section, replace the existing coefficients (Coefficient Vector) with xlfda\_numerator('FDATool') to use the coefficients defined by the FDATool instance.

8. Click **OK** to exit the Digital FIR Filter Properties Editor.

In an FPGA, the design operates at a specific clock rate and using a specific number of bits to represent the data values.

The transition between the continuous time used in the standard Simulink environment and the discrete time of the FPGA hardware environment is determined by defining the sample rate of the Gateway In blocks. This determines how often the continuous input waveform is sampled. This sample rate is automatically propagated to other blocks in the design by Model Composer. In a similar manner, the number of bits used to represent the data is defined in the Gateway In block and also propagated through the system.

Although not used in this tutorial, some HDL blocks enable rate changes and bit-width changes, up or down, as part of this automatic propagation. More details on these blocks are found in the *Vitis Model Composer User Guide* (UG1483).

Both of these attributes (rate and bit width) determine the degree of accuracy with which the continuous time signal is represented. Both of these attributes also have an impact on the size, performance, and hence cost of the final hardware.

Model Composer allows you to use the Simulink environment to define, simulate, and review the impact of these attributes.

9. Double-click the **Gateway In** block to open the Properties Editor.

Because the highest frequency sine wave in the design is 9 MHz, sampling theory dictates the sampling frequency of the input port must be at least 18 MHz. For this design, you will use 20 MHz.

- 10. At the bottom of the Properties Editor, set the Sample Period to 1/20e6.

- 11. For now, leave the bit width as the default fixed-point 2's complement 16-bits with 14-bits representing the data below the binary point. This allows us to express a range of -2.0 to 1.999, which exceeds the range required for the summation of the sine waves (both of amplitude 1).

12. Click **OK** to close the Gateway In Properties Editor.

This now allows us to use accurate sample rate and bit-widths to accurately verify the hardware.

13. Double-click the **System Generator** token to open the Properties Editor.

Because the input port is sampled at 20 MHz to adequately represent the data, you must define the clock rate of the FPGA and the Simulink sample period to be at least 20 MHz.

- 14. Select the Clocking tab.

- a. Specify an FPGA clock period of 50 ns (1/20 MHz).

- b. Specify a Simulink system period of 1/20e6 seconds.

- c. From the Perform analysis menu, select **Post Synthesis** and from the Analyzer type menu select **Resource** as shown in the following figure. This option gives the resource utilization details after completion.

- 15. Click **OK** to exit the System Generator token.

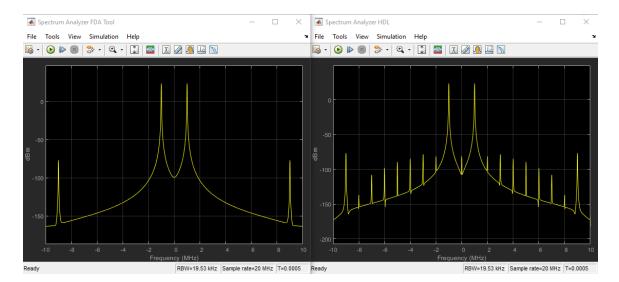

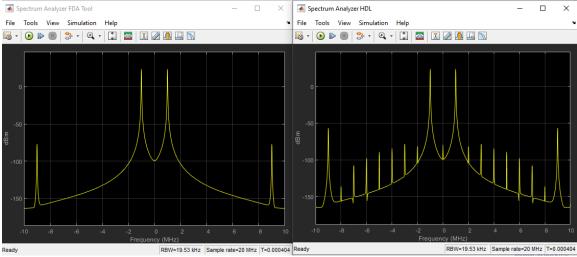

- 16. Click the Run simulation button to simulate the design and view the results, as shown in the following figure.

Because the new design is cycle and bit accurate, simulation might take longer to complete than before.

The results are shown above, on the right hand side (in the Spectrum Analyzer HDL window), and differ slightly from the original design (shown on the left in the Spectrum Analyzer FDA Tool window). This is due to the quantization and sampling effect inherent when a continuous time system is described in discrete time hardware.

The final step is to implement this design in hardware. This process will synthesize everything contained between the Gateway In and Gateway Out blocks into a hardware description. This description of the design is output in the Verilog or VHDL Hardware Description Language (HDL). This process is controlled by the System Generator token.

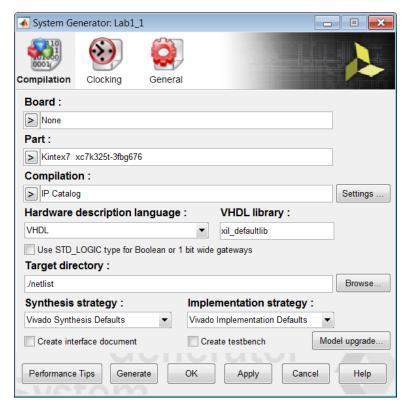

- 17. Double-click the **System Generator** token to open the Properties Editor.

- 18. Select the **Compilation** tab to specify details on the device and design flow.

- 19. From the Compilation menu, select the IP catalog compilation target to ensure the output is in IP catalog format. The Part menu selects the FPGA device. For now, use the default device. Also, use the default Hardware description language, VHDL.

#### 20. Click **Generate** to compile the design into hardware.

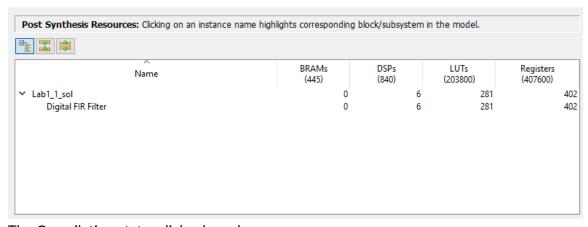

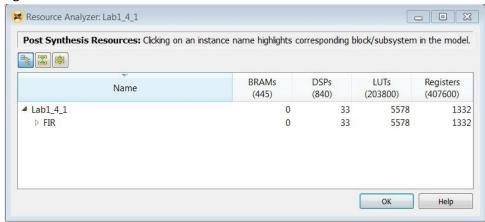

The compilation process transforms the design captured in Simulink blocks into an industry standard Register Transfer Level (RTL) design description. The RTL design can be synthesized into a hardware design. A Resource Analyzer window appears when the hardware design description has been generated.

The Compilation status dialog box also appears.

- 21. Click **OK** to dismiss the Compilation status dialog box.

- 22. Click **OK** to dismiss the Resource Analyzer window.

- 23. Click **OK** to dismiss the System Generator token.

The final step in the design process is to create the hardware and review the results.

#### Review the Results

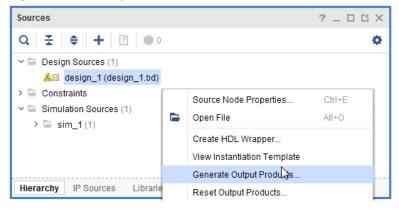

The output from design compilation process is written to the netlist directory. This directory contains three subdirectories:

- sysgen: This contains the RTL design description written in the industry standard VHDL format. This is provided for users experienced in hardware design who wish to view the detailed results.

- ip: This directory contains the design IP, captured in Xilinx IP catalog format, which is used to transfer the design into the Xilinx Vivado. Lab 5: Using AXI Interfaces and IP Integrator, presented later in this document, explains in detail how to transfer your design IP into the Vivado for implementation in an FPGA

- ip\_catalog: This directory contains an example Vivado project with the design IP already included. This project is provided only as a means of quick analysis.

The previous Resource Analyzer: Lab1\_1 figure shows the summary of resources used after the design is synthesized. You can also review the results in hardware by using the example Vivado project in the  $ip\_catalog$  directory.

**IMPORTANT!** The Vivado project provided in the  $ip\_catalog$  directory does not contain top-level I/O buffers. The results of synthesis provide a very good estimate of the final design results; however, the results from this project cannot be used to create the final FPGA.

When you have reviewed the results, exit the  $Lab1_1.slx$  Simulink worksheet.

#### Step 2: Creating an Optimized Design in an FPGA

In this step you will see how an FPGA can be used to create a more optimized version of the same design used in Step 1, by oversampling. You will also learn about using workspace variables.

1. At the command prompt, type open Lab1\_2.slx.

- From your Simulink project worksheet, select Simulation → Run or click the Run simulation button to confirm this is the same design used in Step 1: Creating a Design in an FPGA.

- 3. Double-click the System Generator token to open the Properties Editor.

As noted in Step 1, the design requires a minimum sample frequency of 18 MHz and it is currently set to 20 MHz (a 50 ns FPGA clock period).

The frequency at which an FPGA device can be clocked easily exceeds 20 MHz. Running the FPGA at a much higher clock frequency will allow Model Composer to use the same hardware resources to compute multiple intermediate results.

- 4. Double-click the **FDATool** instance to open the Properties Editor.

- 5. Click the **Filter Coefficients** button let view the filter coefficients.

This shows the filter uses 11 symmetrical coefficients. This requires a minimum of six multiplications. This is indeed what is shown at the end of the HDL Blocks section where the final hardware is using six DSP48 components, the FPGA resource used to perform a multiplication.

The current design samples the input at a rate of 20 MHz. If the input is sampled at 6 times the current frequency, it is possible to perform all calculations using a single multiplier.

- 6. Close the FDATool Properties Editor.

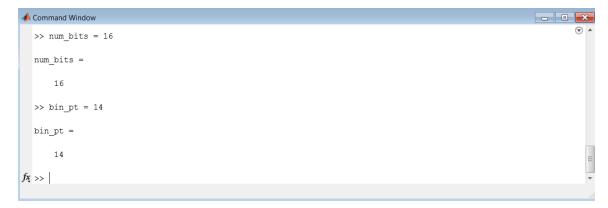

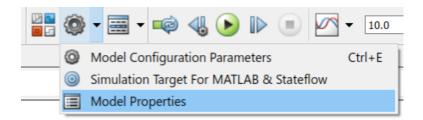

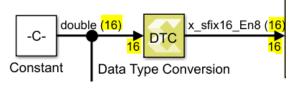

- 7. You will now replace some of the attributes of this design with workspace variables. First, you need to define some workspace variables.

- 8. In the MATLAB Command Window:

- a. Enter num\_bits = 16

- b. Enter bin\_pt = 14

- 9. In design Lab1\_2, double-click the **Gateway In** block to open the Properties Editor.

- 10. In the Fixed-Point Precision section, replace 16 with num\_bits and replace 14 with bin\_pt, as shown in the following figure.

11. Click **OK** to save and exit the Properties Editor.

In the System Generator token update the sampling frequency to 120 MHz (6  $^{*}$  20 MHz) in this way:

- 1. Specify an FPGA clock period of 8.33 ns (1/120 MHz).

- 2. Specify a Simulink system period of 1/120e6 seconds.

- 3. From the Perform analysis menu, select **Post Synthesis** and from Analyzer type menu, select **Resource** as shown in the following figure. This option gives the resource utilization details after completion.

**Note:** In order to see accurate results from Resource Analyzer Window it is recommended to specify a new target directory rather than use the current working directory.

12. Click **Generate** to compile the design into a hardware description.

In this case, the message appearing in the Diagnostic Viewer can be dismissed as you are purposely clocking the design above the sample rate to allow resource sharing and reduce resources. Close the Diagnostic Viewer window.

13. When generation completes, click **OK** to dismiss the Compilation status dialog box.

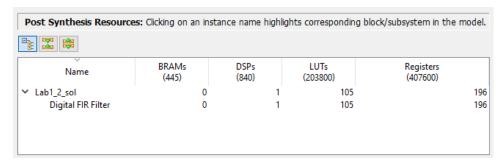

The Resource Analyzer window opens when the generation completes, giving a good estimate of the final design results after synthesis as shown in the following figure.

The hardware design now uses only a single DSP48 resource (a single multiplier) and compared to the results at the end of the Configure the HDL Blocks section, the resources used are significantly lower.

- 14. Click **OK** to dismiss the Resource Analyzer window.

- 15. Click **OK** to dismiss the System Generator token.

Exit the Lab1\_2.slx Simulink worksheet.

## Step 3: Creating a Design Using Discrete Components

In this step you will see how Model Composer can be used to build a design using discrete components to realize a very efficient hardware design.

1. At the command prompt, type open Lab1\_3.slx.

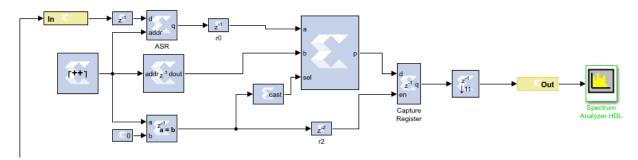

This opens the Simulink design shown in the following figure. This design is similar to the one in the previous two steps. However, this time the filter is designed with discrete components and is only partially complete. As part of this step, you will complete this design and learn how to add and configure discrete parts.

This discrete filter operates in this way:

- Samples arrive through port In and after a delay stored in a shift register (instance ASR).

- A ROM is required for the filter coefficients.

- A counter is required to select both the data and coefficient samples for calculation.

- A multiply accumulate unit is required to perform the calculations.

- The final down-sample unit selects an output every n<sup>th</sup> cycle.

Start by adding the discrete components to the design.

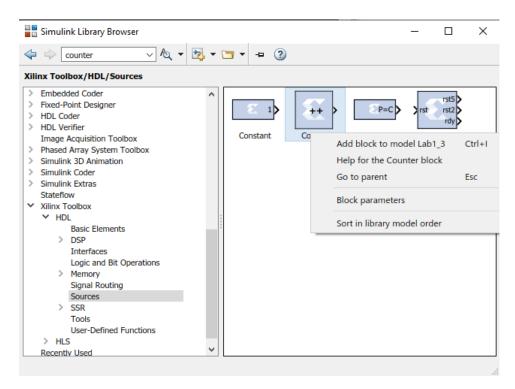

- 2. Click the Library Browser button in the Simulink toolbar to open the Simulink Library Browser.

- a. Expand the Xilinx Blockset menu.

- b. As shown in the following figure, select the **Sources** section in the HDL library, then right-click **Counter** to add this component to the design.

- c. Select the **Memory** section (shown at the bottom left in the figure above) and add a ROM to the design.

- d. Finally, select the **DSP** section and add a DSP Macro 1.0 to the design.

- 3. Connect the three new instances to the rest of the design as shown in the following figure:

You will now configure the instances to correctly filter the data.

4. Double-click the **FDATool** instance and select Filter Coefficients from the toolbar to review the filter specifications.

This shows the same specifications as the previous steps in Lab 1 and confirms there are 11 coefficients. You can also confirm, by double-clicking on the input Gateway In that the input sample rate is once again 20 MHz (Sample period = 1/20e6). With this information, you can now configure the discrete components.

- 5. Close the FDATool Properties Editor.

- 6. Double-click the **Counter** instance to open the Properties Editor.

- a. For the Counter type, select **Count limited** and enter this value for **Count to value**: length(xlfda\_numerator('FDATool'))-1

This will ensure the counter counts from 0 to 10 (11 coefficient and data addresses).

- b. For Output type, leave default value at Unsigned and in Number of Bits enter the value 4. Only 4 binary address bits are required to count to 11.

- c. For the Explicit period, enter the value 1/(11\*20e6) to ensure the sample period is 11 times the input data rate. The filter must perform 11 calculations for each input sample.

- d. Click **OK** to exit the Properties Editor.

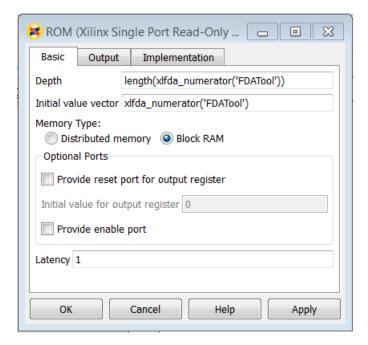

- 7. Double-click the **ROM** instance to open the Properties Editor.

- a. For the Depth, enter the value length(xlfda\_numerator('FDATool')). This will ensure the ROM has 11 elements.

- b. For the Initial value vector, enter xlfda\_numerator('FDATool'). The coefficient values will be provided by the FDATool instance.

- c. Click **OK** to exit the Properties Editor.

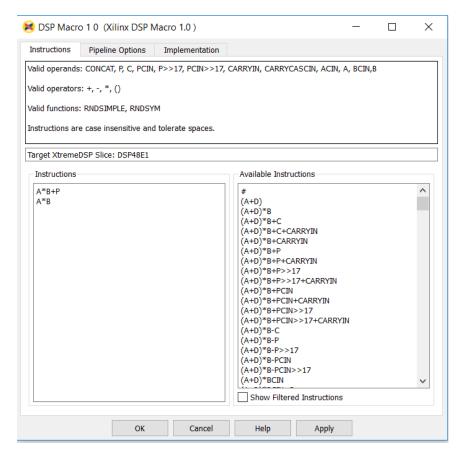

- 8. Double-click the **DSP Macro 1.0** instance to open the Properties Editor.

- a. In the Instructions tab, replace the existing Instructions with A\*B+P and then add A\*B. When the sel input is false the DSP will multiply and accumulate. When the sel input is true the DSP will simply multiply.

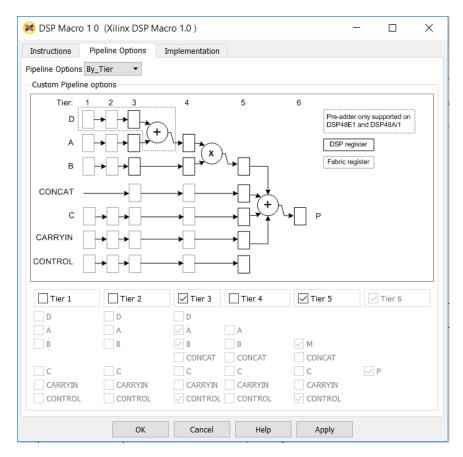

- b. In the Pipeline Options tab, use the Pipeline Options drop-down menu to select By\_Tier.

- c. Select **Tier 3** and **Tier 5**. This will ensure registers are used at the inputs to A and B and between the multiply and accumulate operations.

- d. Click **OK** to exit the Properties Editor.

- 9. Click **Save** to save the design.

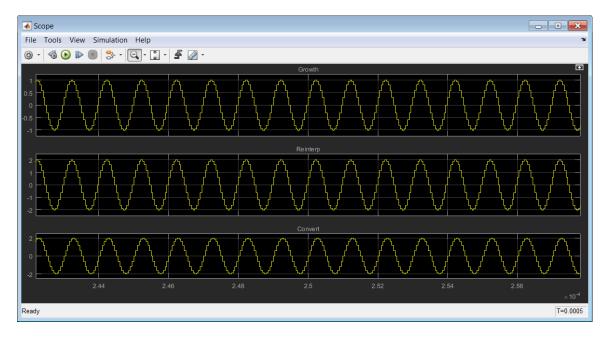

- 10. Click the Run simulation button to simulate the design and view the results, as shown in the following figure.

The final step is to compile the design into a hardware description and synthesize it.

11. Double-click the **System Generator** token to open the Properties Editor.

- 12. From the Compilation tab, make sure the Compilation target is IP catalog.

- 13. From the Clocking tab, under Perform analysis select **Post Synthesis** and for Analyzer type select **Resource**. This option gives the resource utilization details after completion.

**Note:** In order to see accurate results from Resource Analyzer Window it is recommended to specify a new target directory rather than use the current working directory.

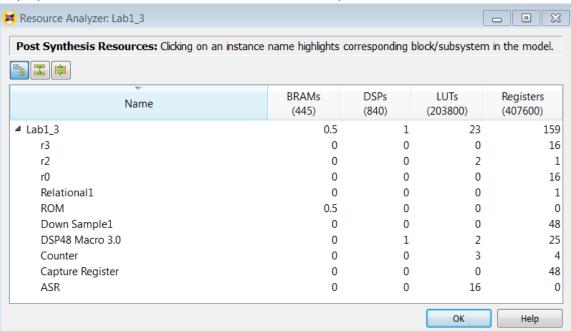

14. Click **Generate** to compile the design into a hardware description. After generation finishes, it displays the resource utilization in the Resource Analyzer window.

The design now uses fewer FPGA hardware resources than either of the versions designed with the Digital FIR Filter macro.

- 15. Click **OK** to dismiss the Resource Analyzer window.

- 16. Click **OK** to dismiss the Compilation status dialog box.

- 17. Click **OK** to dismiss the System Generator token.

- 18. Exit the Lab1\_3.slx worksheet.

#### **Step 4: Working with Data Types**

In this step, you will learn how hardware-efficient fixed-point types can be used to create a design which meets the required specification but is more efficient in resources, and understand how to use Xilinx HDL Blocksets to analyze these systems.

This step has two primary parts:

• In Part 1, you will review and synthesize a design using floating-point data types.

In Part 2, you will work with the same design, captured as a fixed-point implementation, and refine the data types to create a hardware-efficient design which meets the same requirements.

#### Part 1: Designing with Floating-Point Data Types

In this part you will review a design implemented with floating-point data types.

1. At the command prompt, type open Lab1\_4\_1.slx.

This opens the Simulink design shown in the following figure. This design is similar to the design used in Lab 1\_1, however this time the design is using float data types and the filter is implemented in sub-system FIR.

First, you will review the attributes of the design, then simulate the design to review the performance, and finally synthesize the design.

In the previous figure, both the input and output of instance FIR are of type double.

2. In the MATLAB Command Window enter:

```

MyCoeffs = xlfda_numerator('FDATool')

```

- 3. Double-click the instance **FIR** to open the sub-system.

- 4. Double-click the instance **Constant1** to open the Properties Editor.

This shows the Constant value is defined by MyCoeffs (1).

- 5. Close the Constant1 Properties editor.

- 6. Return to the top-level design using the toolbar button Up To Parent 1, or click the tab labeled Lab1\_4\_1.

The design is summing two sine waves, both of which are 9 MHz. The input gateway to the Model Composer must therefore sample at a rate of at least 18 MHz.

- 7. Double-click the **Gateway In1** instance to open the Properties Editor and confirm the input is sampling the data at a rate of 20 MHz (a Sample period of 1/20e6).

- 8. Close the Gateway In Properties editor.

- 9. Click the Run simulation button to simulate the design.

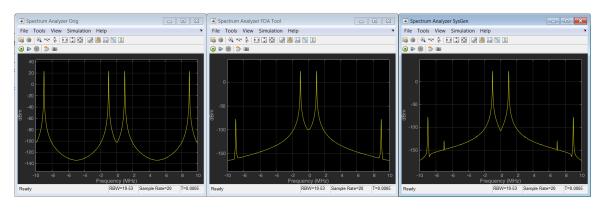

The results shown in the following figure show the Model Composer HDL blockset produces results which are very close to the ideal case, shown in the center. The results are not identical because the Model Composer design must sample the continuous input waveform into discrete time values.

The final step is to synthesize this design into hardware.

- 10. Double-click the **System Generator** token to open the Properties Editor.

- 11. On the Compilation tab, make sure the Compilation target is IP Catalog.

- 12. On the Clocking tab, under Perform analysis select **Post Synthesis** and from Analyzer type menu select **Resource**. This option gives the resource utilization details after completion.

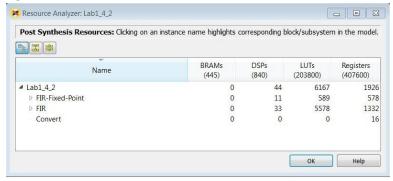

- 13. Click **Generate** to compile the design into a hardware description. After completion, it generates the resource utilization in Resource Analyzer window as shown in the following figure.

- 14. Click **OK** to dismiss the Compilation status dialog box.

- 15. Click **OK** to dismiss the System Generator token.

You implemented this same filter in Step 1 using fixed-point data types. When compared to the synthesis results from that implementation – the initial results from Step are shown in the following figure and you can see this current version of the design is using a large amount of registers (FF), LUTs, and DSP48 (DSP) resources (Xilinx dedicated multiplier/add units).

Maintaining the full accuracy of floating-point types is an ideal implementation but implementing full floating-point accuracy requires a significant amount of hardware.

For this particular design, the entire range of the floating-point types is not required. The design is using considerably more resources than what is required. In the next part, you will learn how to compare designs with different data types inside the Simulink environment.

- 16. Exit the Vivado Design Suite.

- 17. Exit the Lab1\_4\_1.slx Simulink worksheet.

#### Part 2: Designing with Fixed-Point Data Types

In this part you will re-implement the design from Part 1: Designing with Floating-Point Data Types using fixed-point data types, and compare this new design with the original design. This exercise will demonstrate the advantages and disadvantages of using fixed-point types and how Model Composer allows you to easily compare the designs, allowing you to make trade-offs between accuracy and resources within the Simulink environment before committing to an FPGA implementation.

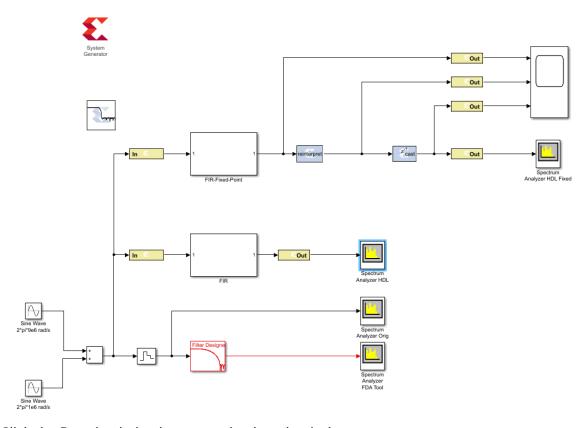

1. At the command prompt, type open Lab1\_4\_2.slx to open the design shown in the following figure.

2. In the MATLAB Command Window enter:

```

MyCoeffs = xlfda_numerator('FDATool')

```

- 3. Double-click the instance **Gateway In2** to confirm the data is being sampled as 16-bit fixed-point value.

- 4. Click **Cancel** to exit the Properties Editor.

5. Click the Run simulation button to simulate the design and confirm instance Spectrum Analyzer HDL Fixed shows the filtered output.

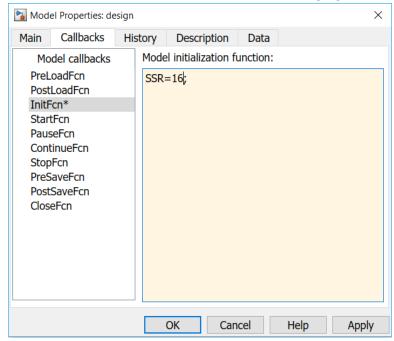

As you will see if you examine the output of instance FIR-Fixed-Point (shown in the previous figure) Model Composer has automatically propagated the input data type through the filter and determined the output must be 43-bit (with 28 binary bits) to maintain the resolution of the signal.

This is based on the bit-growth through the filter and the fact that the filter coefficients (constants in instance FIR-Fixed-Point) are 16-bit.

6. In the MATLAB Command Window, enter sum(abs(MyCoeffs)) to determine the absolute maximum gain using the current coefficients.

```

Command Window

>> MyCoeffs = xlfda_numerator('FDATool')

MyCoeffs =

Columns 1 through 7

0.0019 -0.0111 -0.0412 0.0351 0.2888 0.4509 0.2888

Columns 8 through 11

0.0351 -0.0412 -0.0111 0.0019

>> sum(abs(MyCoeffs))

ans =

1.2070

ft >> |

```

Taking into account the positive and negative values of the coefficients the maximum gain possible is 1.2070 and the output signal should only ever be slightly smaller in magnitude than the input signal, which is a 16-bit signal. There is no need to have 15 bits (43-28) of data above the binary point.

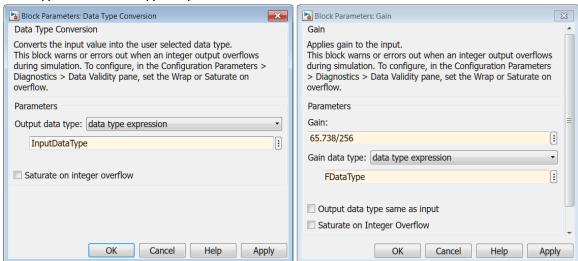

You will now use the Reinterpret and Convert blocks to manipulate the fixed-point data to be no greater than the width required for an accurate result and produce the most hardware efficient design.

- 7. Right-click with the mouse anywhere in the canvas and select Xilinx BlockAdd.

- 8. In the Add Block entry box, type Reinterpret.

- 9. Double-click the **Reinterpret** component to add it to the design.

- 10. Repeat the previous three steps for these components:

- a. Convert

- b. Scope

- 11. In the design, select the Gateway Out2 instance.

- a. Right-click and use Copy and Paste to create a new instance of the Gateway Out block.

- b. Paste twice again to create two more instances of the Gateway Out (for a total of three new instances).

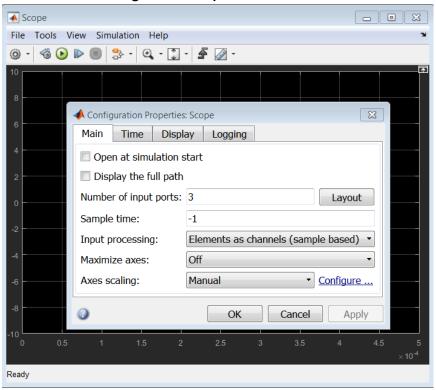

- 12. Double-click the **Scope** component.

- a. In the Scope properties dialog box, select File  $\rightarrow$  Number of Inputs  $\rightarrow$  3.

- b. Select View

Configuration Properties and confirm that the Number of input ports is 3.

- c. Click **OK** to close the Configuration Properties dialog box.

- d. Select **File**  $\rightarrow$  **Close** to close the Scope properties dialog box.

- 13. Connect the blocks as shown in the next figure.

- 14. Rename the signal names into the scope as shown in the following figure: Convert, Reinterpret and Growth.

To rename a signal, click the existing name label and edit the text, or if there is no text double-click the wire and type the name.

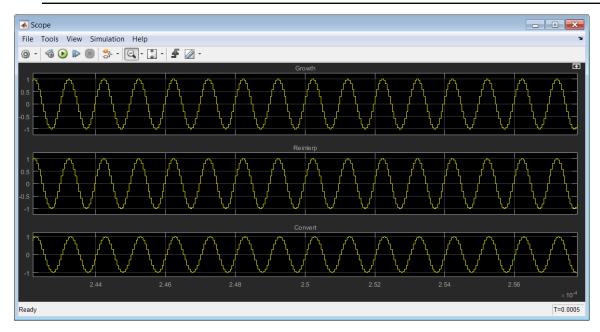

- 15. Click the Run simulation button to simulate the design.

- 16. Double-click the **Scope** to examine the signals.

**TIP:** You might need to zoom in and adjust the scale in **View**  $\rightarrow$  **Configuration Properties** to view the signals in detail.

The Reinterpret and Convert blocks have not been configured at this point and so all three signals are identical.

The HDL Reinterpret block forces its output to a new type without any regard for retaining the numerical value represented by the input. The block allows for unsigned data to be reinterpreted as signed data, or, conversely, for signed data to be reinterpreted as unsigned. It also allows for the reinterpretation of the data's scaling, through the repositioning of the binary point within the data.

In this exercise you will scale the data by a factor of 2 to model the presence of additional design processing which might occur in a larger system. The Reinterpret block can also be used to scale down.

- 17. Double-click the **Reinterpret** block to open the Properties Editor.

- 18. Select Force Binary Point.

- 19. Enter the value 27 in the input field Output Binary Point and click **OK**.

The HDL Convert block converts each input sample to a number of a desired arithmetic type. For example, a number can be converted to a signed (two's complement) or unsigned value. It also allows the signal quantization to be truncated or rounded and the signal overflow to be wrapped, saturated, or to be flagged as an error.

In this exercise, you will use the Convert block to reduce the size of the 43-bit word back to a 16-bit value. In this exercise the Reinterpret block has been used to model a more complex design and scaled the data by a factor of 2. You must therefore ensure the output has enough bits above the binary point to represent this increase.

- 20. Double-click the **Convert** block to open the Properties Editor.

- 21. In the Fixed-Point Precision section, enter 13 for the Binary Point and click OK.

- 22. Save the design.

- 23. Click the Run simulation button to simulate the design.

- 24. Double-click the **Scope** to examine the signals.

**TIP:** You might need to zoom in and adjust the scale in **View**  $\rightarrow$  **Configuration Properties** to view the signals in detail.

In the following figure you can see the output from the filter (Growth) has values between plus and minus 1. The output from the Reinterpret block moves the data values to between plus and minus 2.

In this detailed view of the waveform, the final output (Convert) shows no difference in fidelity, when compared to the reinterpret results, but uses only 16 bits.

The final step is to synthesize this design into hardware.

- 25. Double-click the System Generator token to open the Properties Editor.

- 26. On the Compilation tab, ensure the Compilation target is IP catalog.

- 27. On the Clocking tab, under Perform analysis select **Post Synthesis** and from Analyzer type menu select **Resource**. This option gives the resource utilization details after completion.

**Note:** In order to see accurate results from Resource Analyzer Window it is recommended to specify a new target directory rather than use the current working directory.

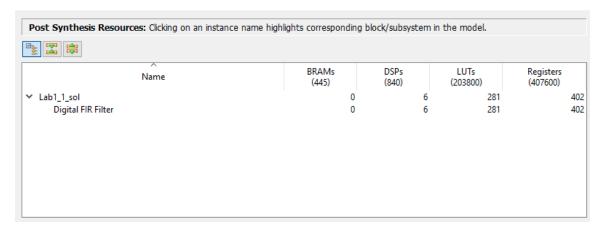

28. Click **Generate** to compile the design into a hardware description. After completion, it generates the resource utilization in Resource Analyzer window as shown in the following figure.

- 29. Click **OK** to dismiss the Compilation status dialog box.

- 30. Click **OK** to dismiss the System Generator token.

Notice, as compared to the results in Step 1, these results show approximately:

• 45% more Flip-Flops

- 20% more LUTs

- 30% more DSP48s

However, this design contains both the original floating-point filter and the new fixed-point version: the fixed-point version therefore uses approximately 75-50% fewer resources with the acceptable signal fidelity and design performance.

- 31. Exit Vivado.

- 32. Exit the Lab1\_4\_2.slx worksheet.

## **Summary**

In this lab, you learned how to use the Model Composer HDL blockset to create a design in the Simulink environment and synthesize the design in hardware which can be implemented on a Xilinx FPGA. You learned the benefits of quickly creating your design using a Xilinx Digital FIR Filter block and how the design could be improved with the use of over-sampling.

You also learned how floating-point types provide a high degree of accuracy but cost many more resources to implement in an FPGA and how the Model Composer HDL blockset can be used to both implement a design using more efficient fixed-point data types and compensate for any loss of accuracy caused by using fixed-point types.

The Reinterpret and Convert blocks are powerful tools which allow you to optimize your design without needing to perform detailed bit-level optimizations. You can simply use these blocks to convert between different data types and quickly analyze the results.

Finally, you learned how you can take total control of the hardware implementation by using discrete primitives.

**Note:** In this tutorial you learned how to add Model Composer HDL blocks to the design and then configure them. A useful productivity technique is to add and configure the System Generator token first. If the target device is set at the start, some complex IP blocks will be automatically configured for the device when they are added to the design.

The following solution directory contains the final Model Composer (\* . slx) files for this lab.

/HDL\_Library/Lab1/solution

# Lab 2: Importing Code into Model Composer HDL Design

## **Objectives**

After completing this lab, you will be able to:

- Create a Finite State Machine using the MCode block in Model Composer.

- Import an RTL HDL description into Model Composer.

- Configure the black box to ensure the design can be successfully simulated.

- Incorporate a design, synthesized from C, C++ or SystemC using Vitis HLS, as a block into your MATLAB design.

## **Step 1: Modeling Control with M-Code**

In this step you will be creating a simple Finite State Machine (FSM) using the MCode block to detect a sequence of binary values 1011. The FSM needs to be able to detect multiple transmissions as well, such as 10111011.

#### **Procedure**

In this step you will create the control logic for a Finite State Machine using M-code. You will then simulate the final design to confirm the correct operation.

- 1. Launch Model Composer and change the working directory to: \HDL\_Library\Lab2\M\_code

- 2. Open the file Lab2\_1.slx.

You see the following incomplete diagram.

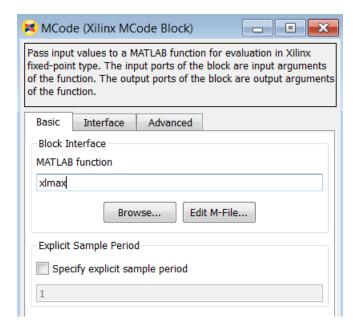

- 3. Add an MCode block from theXilinx Toolbox/HDL/User-Defined Functions library. Before wiring up the block, you need to edit the MATLAB® function to create the correct ports and function name.

- 4. Double-click the **MCode** block and click **Edit M-File**, as shown in the following figure.

The following figure shows the default M-code in the MATLAB text editor.

```

C:\Xilinx\Vivado\2021.1\scripts\sysgen\matlab\xlmax.m

Х

₽ ? •

EDITOR

PUBLISH

VIEW

1

\boxed{\text{function } z = x \text{lmax}(x, y)}

2 -

if x > y

3 -

z = x;

4 -

5 -

z = y;

6

end

7

UTF-8

Ln 1

Col 1

```

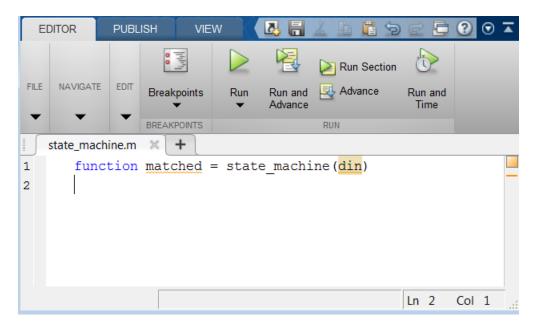

- 5. Edit the default MATLAB function to include the function name state\_machine and the input din and output matched.

- 6. You can now delete the sample M-code.

- 7. After you make the edits, use Save As to save the MATLAB file as state\_machine.m to the Lab2/M\_code folder.

- a. In the MCode Properties Editor, use the Browse button to ensure that the MCode block is referencing the local M-code file (state\_machine.m).

- 8. In the MCode Properties Editor, click **OK**.

You will see the MCode block assume the new ports and function name.

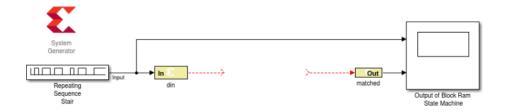

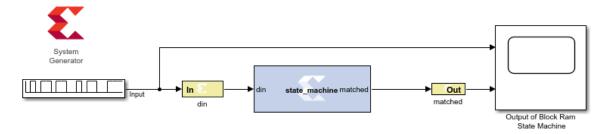

9. Now connect the MCode block to the diagram as shown in the following figure:

You are now ready to start coding the state machine. The bubble diagram for this state machine is shown in the following figure. This FSM has five states and is capable of detecting two sequences in succession.

10. Edit the M-code file,  $state_machine.m$ , and define the state variable using the Xilinx  $xl_state$  data type as shown in the following. This requires that you declare a variable as a persistent variable. The  $xl_state$  function requires two arguments: the initial condition and a fixed-point declaration.

Because you need to count up to 4, you need 3 bits.

```

persistent state, state = xl_state(0,{xlUnsigned, 3, 0});

```

11. Use a switch-case statement to define the FSM states shown. A small sample is provided, shown as follows, to get you started.

Note: You need an otherwise statement as your last case.

```

switch state

case 0

if din == 1

state = 1

else

state = 0

end

matched = 0;

```

12. Save the M-code file and run the simulation. The waveform should look like the following figure.

You should notice two detections of the sequence.

# **Step 2: Modeling Blocks with HDL**

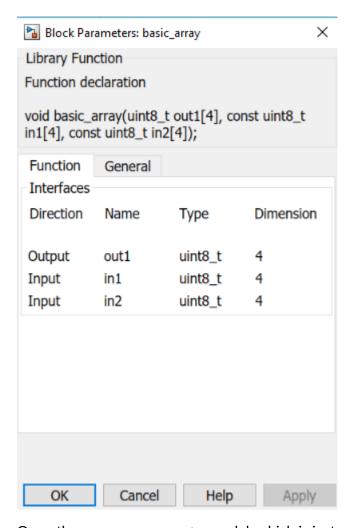

In this step, you will import an RTL design into Model Composer as a black box.

A black box allows the design to be imported into Model Composer even though the description is in Hardware Description Language (HDL) format.

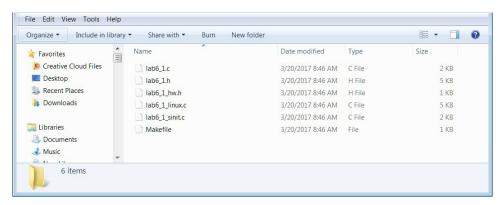

1. Invoke Vitis Model Composer and from the MATLAB console, change the directory to: \HDL\_Library\Lab2\HDL.

The following files are located in this directory:

- Lab2\_2.slx A Simulink model containing a black box example.

- transpose\_fir.vhd Top-level VHDL for a transpose form FIR filter. This file is the VHDL that is associated with the black box.

- mac.vhd Multiply and adder component used to build the transpose FIR filter.

- 2. Type open Lab2\_2.slx.

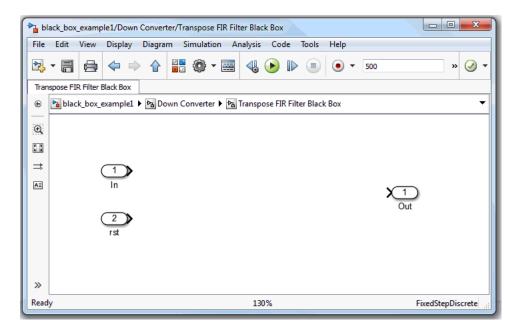

- 3. Open the subsystem named Down Converter.

- 4. Open the subsystem named Transpose FIR Filter Black Box.

At this point, the subsystem contains two input ports and one output port. You will add a black box to this subsystem:

5. Right-click the design canvas, select **Xilinx BlockAdd**, and add a Black Box block to this subsystem.

A browser window opens, listing the VHDL source files that can be associated with the black box.

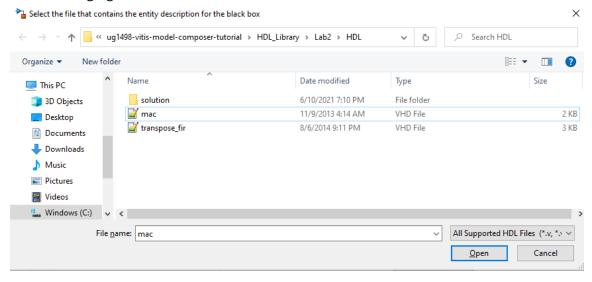

6. From this window, select the top-level VHDL file transpose\_fir.vhd. This is illustrated in the following figure.

The associated configuration M-code transpose\_fir\_config.m opens in an Editor for modifications.

- 7. Close the Editor.

- 8. Wire the ports of the black box to the corresponding subsystem ports and save the design.

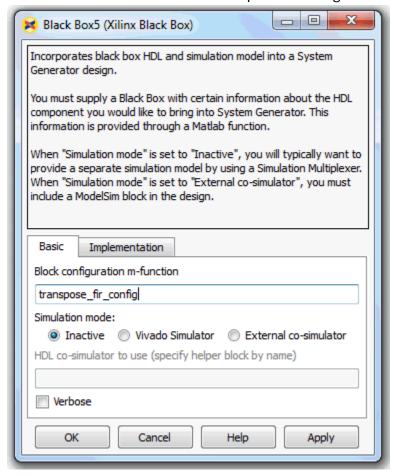

9. Double-click the Black Box block to open this dialog box:

The following are the fields in the dialog box:

- Block configuration m-function: This specifies the name of the configuration M-function for the black box. In this example, the field contains the name of the function that was generated by the Configuration Wizard. By default, the black box uses the function the wizard produces. You can however substitute one you create yourself.

- Simulation mode: There are three simulation modes:

- Inactive: In this mode the black box participates in the simulation by ignoring its inputs and producing zeros. This setting is typically used when a separate simulation model is available for the black box, and the model is wired in parallel with the black box using a simulation multiplexer.

- **Vivado Simulator:** In this mode simulation results for the black box are produced using co-simulation on the HDL associated with the black box.

- External co-simulator: In this mode it is necessary to add a Questa HDL co-simulation block to the design, and to specify the name of the Questa block in the HDL co-simulator to use field. In this mode, the black box is simulated using HDL co-simulation.

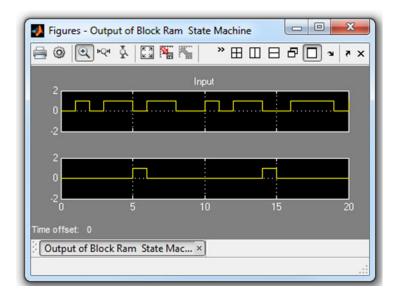

- 10. Set the Simulation mode to Inactive and click **OK** to close the dialog box.

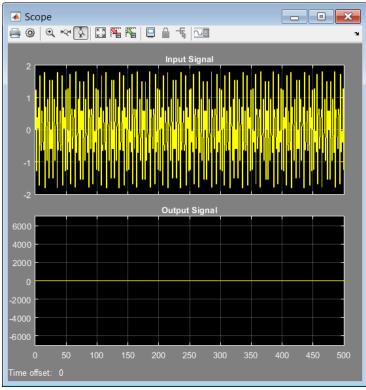

- 11. Move to the design top-level and run the simulation by clicking the Run simulation button

- then double-click the Scope block.

- 12. Notice the black box output shown in the Output Signal scope is zero. This is expected because the black box is configured to be Inactive during simulation.

- 13. From the Simulink Editor menu, select **Other Displays** → **Signals** & **Ports** → **Port Data Types** to display the port types for the black box.

- 14. Compile the model (Ctrl-D) to ensure the port data types are up to date.

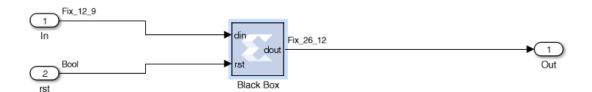

Notice that the black box port output type is  $UFix_26_0$ . This means it is unsigned, 26-bits wide, and has a binary point 0 positions to the left of the least significant bit.

15. Open the configuration M-function transpose\_fir\_config.m and change the output type from UFix\_26\_0 to Fix\_26\_12. The modified line (line 26) should read:

```

dout_port.setType('Fix_26_12');

```

Continue the following steps to edit the configuration M-function to associate an additional HDL file with the black box.

16. Locate line 65:

```

this_block.addFile('transpose_fir.vhd');

```

17. Immediately above this line, add the following:

```

this_block.addFile('mac.vhd');

```

- 18. Save the changes to the configuration M-function and close the file.

- 19. Click the design canvas and recompile the model (Ctrl-D).

Your Transpose FIR Filter Black Box subsystem should display as follows:

- 20. From the Black Box block parameter dialog box, change the Simulation mode field from **Inactive** to **Vivado Simulator** and then click **OK**.

- 21. Move to the top-level of the design and run the simulation.

- 22. Examine the scope output after the simulation has completed.

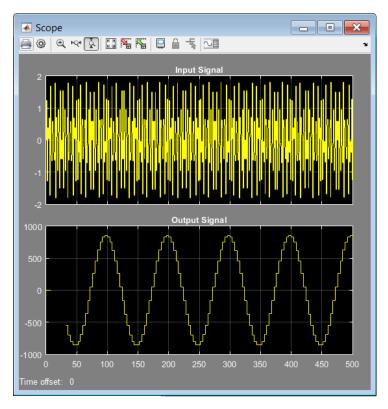

Notice the waveform is no longer zero. When the Simulation Mode was Inactive, the Output Signal scope displayed constant zero. Now, the Output Signal shows a sine wave as the results from the Vivado Simulation.

23. Right-click the Output Signal display and select **Configuration Properties**. In the Main tab, set **Axis Scaling** to the **Auto** setting.

You should see a display similar to that shown below.

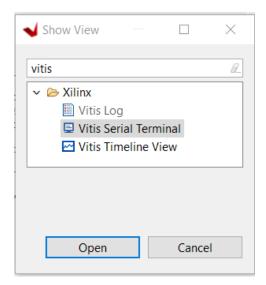

# **Step 3: Modeling Blocks with C/C++ Code**

The Vitis HLS tool has the ability to transform C/C++ design sources into RTL. The Model Composer HDL library contains a Vitis HLS block in the HDL/User-Defined Functions library which enables you to bring in C/C++ source files into a Model Composer model.

#### **Procedure**

In this step you will first synthesize a C file using Vitis HLS. You will operate within a Vivado DSP design project, using a design file from MATLAB along with an associated HDL wrapper and constraint file. In Part 2, you incorporate the output from Vitis HLS into MATLAB and use the rich simulation features of MATLAB to verify that the C algorithm correctly filters an image.

## Part 1: Creating a Vitis HLS Package

- 1. Invoke Vitis HLS: Click Windows → Xilinx Design Tools → Vitis HLS 2021.1.

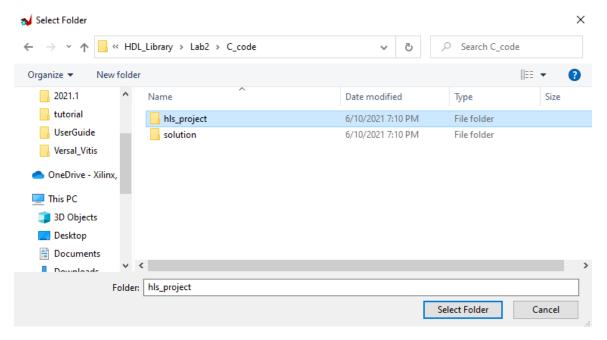

- 2. Select Open Project in the welcome screen and navigate to the Vitis HLS project directory \HDL\_Library\Lab2\C\_code\hls\_project as shown in the following figure.

- 3. Click Select Folder to open the project.

- 4. Expand the Source folder in the Explorer pane (left-hand side) and double-click the file MedianFilter.cpp to view the contents of the C++ file as shown in the following figure.

```

☑ MedianFilter.cpp ×

Explorer ×

"MedianFilter.h"

WINDOW_SIZE 3

unsigned char PixelType;

🕯 📂 hls_project

includes

🗟 MedianFilter.cpp

PIX_SWAP(a,b) { PixelType temp=(a);(a)=(b);(b)=temp; }

PIX_SORT(a,b) { if ((a)>(b)) PIX_SWAP((a),(b)); }

Test Bench

Range TestMedianFilter.cpp

a solution1

constraints

PIX_SORT(p[1], p[2]); PIX_SORT(p[4], p[5]); PIX_SORT(p[7], p[8]); PIX_SORT(p[0], p[1]); PIX_SORT(p[3], p[4]); PIX_SORT(p[6], p[7]); PIX_SORT(p[1], p[2]); PIX_SORT(p[4], p[5]); PIX_SORT(p[7], p[8]); PIX_SORT(p[1], p[8]); PIX_SORT(p[0], p[3]); PIX_SORT(p[5], p[8]); PIX_SORT(p[4], p[7]); PIX_SORT(p[3], p[6]); PIX_SORT(p[1], p[4]); PIX_SORT(p[2], p[5]); PIX_SORT(p[4], p[7]); PIX_SORT(p[4], p[2]); PIX_SORT(p[4], p[2]); return(p[4]);

directives.tcl

script.tcl

🔠 Git Repositories 🗴

A

Select one of the following to add a repository to this

view:

Add an existing local Git repository

Glone a Git repository

Treate a new local Git repository

igned int sum;

(i = 0;i<9; i++) {

sum+=buffer[i];

sum/=(WINDOW SIZE*WINDOW SIZE);

📃 Console 🗴 🥙 Errors 🎂 Warnings 🗽 Guidance 😓 Man Pages

itis HLS Console

```

This file implements a 2-Dimensional median filter on 3x3 window size.

5. Synthesize the source file by right-clicking on solution1 and selecting **C Synthesis** → **Active Solution** as shown in the following figure.

When the synthesis completes, Vitis HLS displays this message:

Finished C synthesis

Now you will package the source for use in Model Composer.

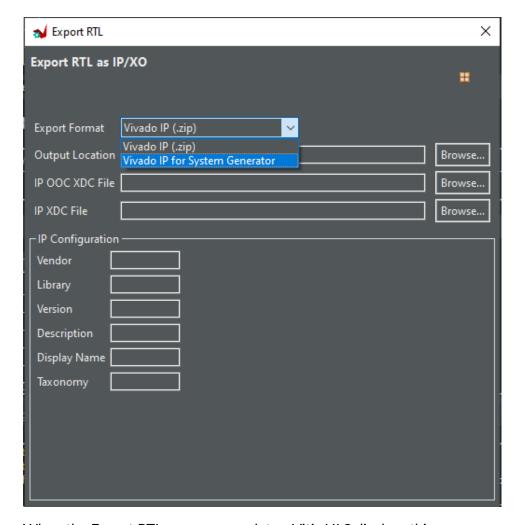

- 6. Right-click solution1 and select Export RTL.

- 7. Set Format Selection to **Vivado IP for System Generator** as shown in the following figure and click **OK**.

When the Export RTL process completes, Vitis HLS displays this message:

Finished export RTL

8. Exit Vitis HLS.

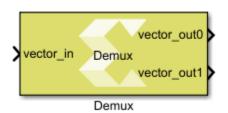

## Part 2: Including a Vitis HLS Package in a Model Composer Design

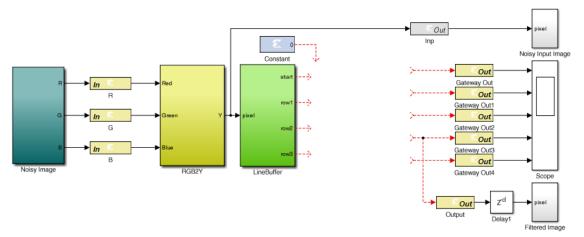

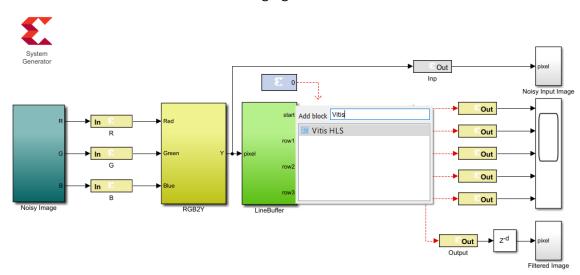

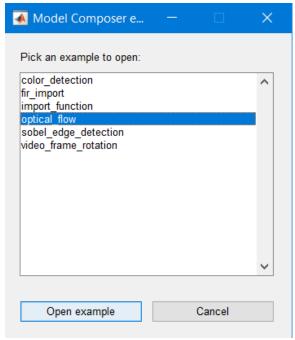

1. Launch Model Composer and open the  $Lab2_3.s1x$  file in the  $Lab2/C\_code$  folder. This should open the model as shown in the following figure.

### 2. Add a Vitis HLS block:

- a. Right-click anywhere on the canvas workspace.

- b. Select Xilinx BlockAdd.

- c. Type Vitis HLS in the Add block dialog box.

- d. Select **Vitis HLS** as shown in the following figure.

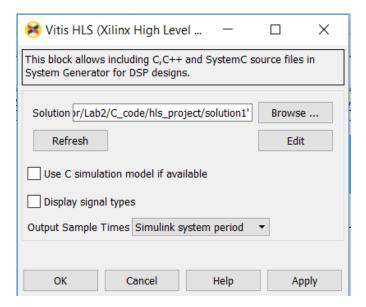

- 3. Double-click the Vitis HLS block to open the Properties Editor.

- 4. Use the Browse button to select the solution created by Vitis HLS in Step 1, at \HDL\_Library\Lab2\C\_code\hls\_project\solution1, as shown in the following figure.

- 5. Click **OK** to import the Vitis HLS IP.

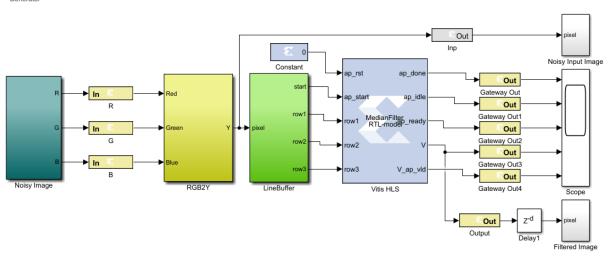

6. Connect the input and output ports of the block as shown in the following figure.

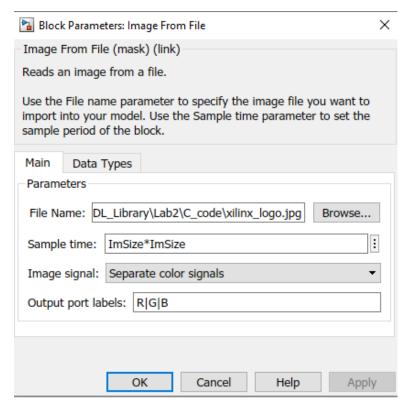

- 7. Navigate into the Noisy Image sub-system and double-click the **Image From File** block to open the Block Parameters dialog box.

- 8. Use the **Browse** button to ensure the file name correctly points to the file  $xilinx_logo.jpg$  as shown in the following figure.

- 9. Click **OK** to exit the Block Parameters dialog box.

- 10. Use the Up to Parent  $\frac{1}{2}$  toolbar button to return to the top level.

- 11. Save the design.

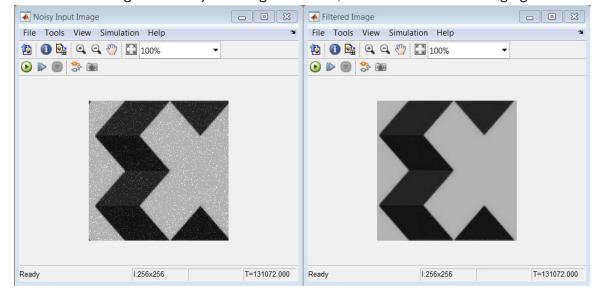

- 12. Simulate the design and verify the image is filtered, as shown in the following figures.

## **Summary**

In this lab you learned:

- How to create control logic using M-Code. The final design can be used to create an HDL netlist, in the same manner as designs created using the HDL Blocksets.

- How to model blocks in Model Composer using HDL by incorporating an existing VHDL RTL design and the importance of matching the data types of the Model Composer model with those of the RTL design and how the RTL design is simulated within Model Composer.

- How to take a filter written in C++, synthesize it with Vitis HLS and incorporate the design into MATLAB. This process allows you to use any C, C++ or SystemC design and create a custom block for use in your designs. This exercise showed you how to import the RTL design generated by Vitis HLS and use the design inside MATLAB.

Solutions to this lab can be found corresponding locations:

- \HDL\_Library\Lab2\C\_code\solution

- \HDL\_Library\Lab2\HDL\solution

- \HDL\_Library\Lab2\M\_code\solution

# Lab 3: Timing and Resource Analysis

In this lab, you learn how to verify the functionality of your designs by simulating in Simulink® to ensure that your Model Composer design is correct when you implement the design in your target Xilinx® device.

## **Objectives**

After completing this lab, you will be able to:

- Identify timing issues in the HDL files generated by Model Composer and discover the source of the timing violations in your design.

- Perform resource analysis and access the existing resource analysis results, along with recommendations to optimize.

#### **Procedure**

This lab has two primary parts:

- In Step 1 you will learn how to do timing analysis in Model Composer.

- In Step 2 you will learn how to perform resource analysis in Model Composer.

# Step 1: Timing Analysis in Model Composer

- 1. Invoke Vitis Model Composer.

- On Windows systems select Windows → Xilinx Design Tools → Vitis Model Composer 2021.1.

- On Linux systems, type model\_cpomposer at the command prompt.

- 2. Navigate to the Lab3 folder: \HDL\_Library\Lab3.

You can view the directory contents in the MATLAB® Current Folder browser, or type 1s at the command line prompt.

- 3. Open the Lab3 design using one of the following:

- At the MATLAB command prompt, type open Lab3.slx

- Double-click Lab3.slx in the Current Folder browser.

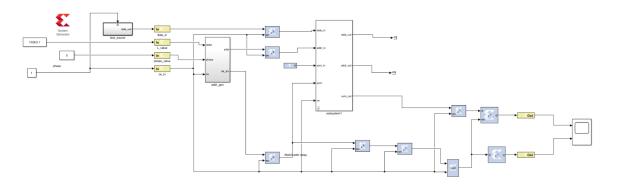

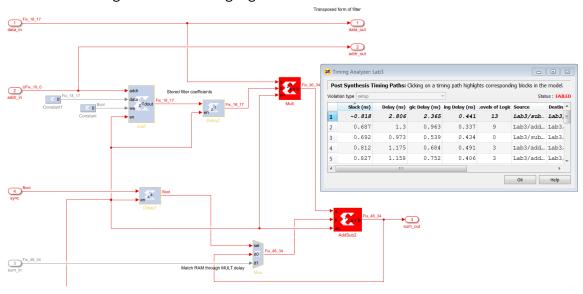

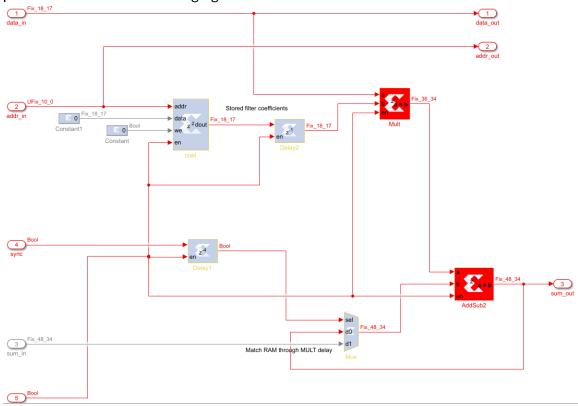

The Lab3 design opens, as shown in the following figure.

4. From your Simulink project worksheet, select **Simulation** → **Run** or click the **Run simulation** button to simulate the design.

**Note:** In order to see accurate results from Resource Analyzer Window it is recommended to specify a new target directory rather than use the current working directory.

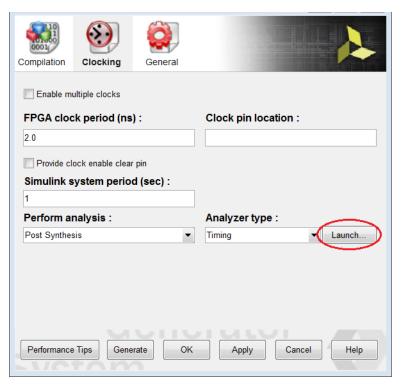

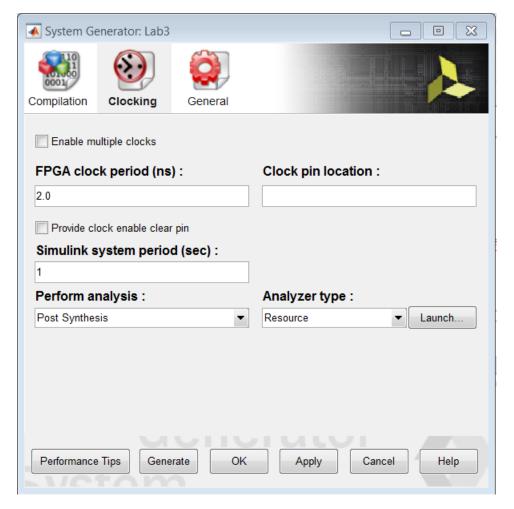

- 5. Double-click the **System Generator** token to open the Properties Editor.

- 6. Select the Clocking tab.

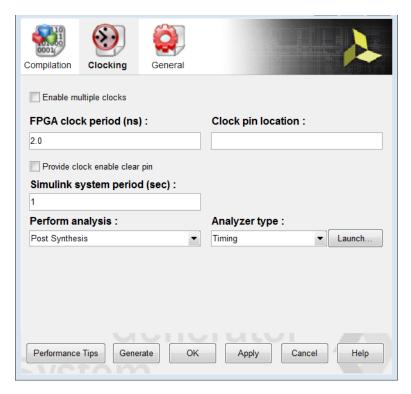

- 7. From the Perform analysis menu, select **Post Synthesis** and from Analyzer type menu select **Timing** as shown in the following figure.

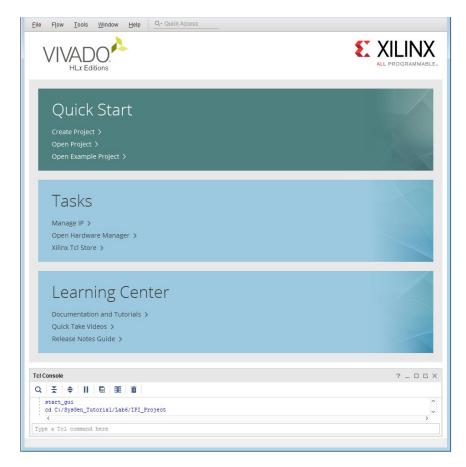

8. In the System Generator token dialog box, click Generate.

When you generate, the following occurs:

- a. Model Composer generates the required files for the selected compilation target. For timing analysis Model Composer invokes Vivado in the background for the design project, and passes design timing constraints to Vivado.

- b. Depending on your selection for Perform Analysis (Post Synthesis or Post Implementation), the design runs in Vivado through synthesis or through implementation.

- c. After the Vivado tools run is completed, timing paths information is collected and saved in a specific file format from the Vivado timing database.

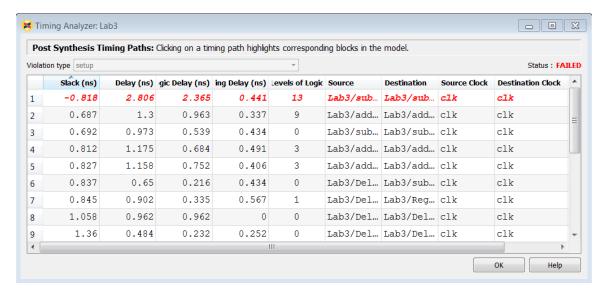

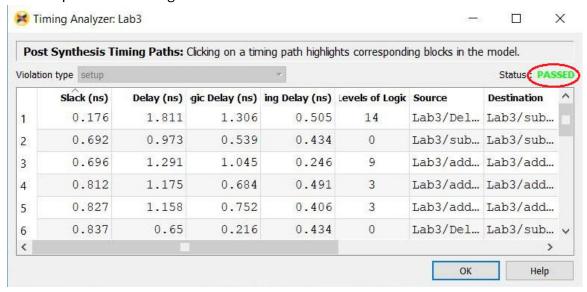

- d. Model Composer processes the timing information and displays a Timing Analyzer table with timing paths information as shown in the following figure.

- 9. In the timing analyzer table:

- Paths with lowest slack values display, with the worst Slack at the top and increasing slack below

- Paths with timing violations have a negative slack and display in red.

- 10. Cross probe from the Timing Analyzer table to the Simulink model by clicking any path in the Timing Analyzer table, which highlights the corresponding Model Composer HDL blocks in the model. This allows you to troubleshoot timing violations by analyzing the path on which they occur.

- 11. When you cross probe, you see the corresponding path as shown in the following figure.

- 12. Blocks with timing violations are highlighted in red.

13. Double-click the second path in the Timing Analyzer table and cross-probe, the corresponding highlighted path in green which indicates no timing violation.

If you close the Timing Analyzer sometime later you might want to relaunch the Timing Analyzer table using the existing timing analyzer results for the model. A Launch button is provided under the Clocking tab of the System Generator token dialog box. This will only work if you already ran timing analysis on the Simulink model.

**Note:** If you relaunch the Timing Analyzer window, make sure that the Analyzer type field is set to Timing. The table that opens will display the results stored Target directory specified in the System Generator token dialog box, regardless of the option selected for Perform analysis (Post Synthesis or Post Implementation).

## **Troubleshooting Timing Violations**

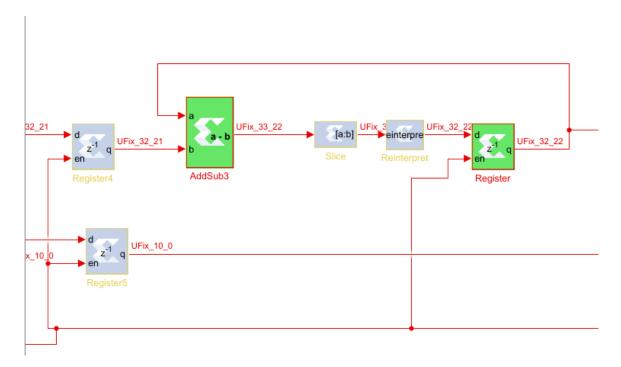

Inserting some registers in the combinational path might give better timing results and might help overcome timing violations if any. This can be done by changing latency of the combinational blocks as explained in the following.

1. Double-click the violated path from the Timing Analyzer window which opens the violated path as shown in the following figure.

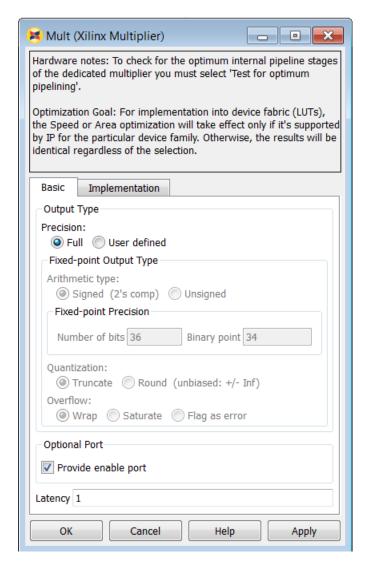

2. Double-click the **Mult** block to open the Multiplier block parameters window as shown in the following figure.

- 3. Under Basic tab, change the latency from 1 to 2 and click OK.

- 4. Double-click the **System Generator** token, and ensure that the Analyzer Type is Timing and click **Generate**.

5. After the generation completes, it opens the timing Analyzer table as shown in the following figure. Observe the status pass at the top-right corner. It indicates there are no timing violated paths in the design.

#### Note:

- 1. For quicker timing analysis iterations, post-synthesis analysis is preferred over post-implementation analysis.

- 2. Changing the latency of the block might increase the number of resources which can be seen using Step 2: Resource Analysis in Model Composer.

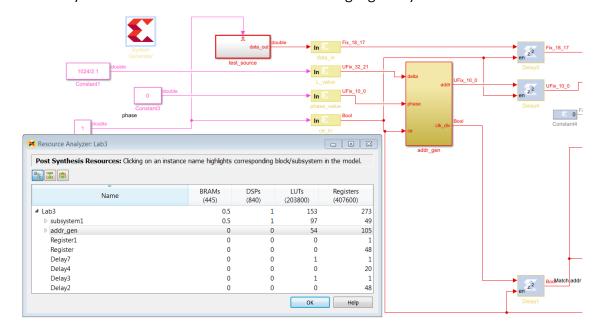

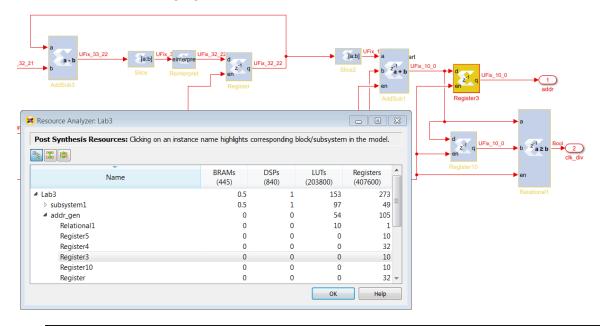

## Step 2: Resource Analysis in Model Composer

In this step we use same design, Lab3.slx, used for Step 1 but we are going to perform Resource Analysis.

**TIP:** Resource Analysis can be performed whenever you generate any of the following compilation targets:

- IP catalog

- Hardware Co-Simulation

- Synthesized Checkpoint

- HDL Netlist

- 1. Double-click the **System Generator** token in the Simulink model. Ensure that the part is specified and Compilation is set to any one of the compilation targets listed above.

- **Note:** In order to see accurate results from Resource Analyzer Window it is recommended to specify a new target directory rather than use the current working directory.

- 2. In the Clocking tab, set the Perform Analysis field to **Post Synthesis** and Analyzer type field to **Resource**.

3. In the System Generator token dialog box, click Generate.

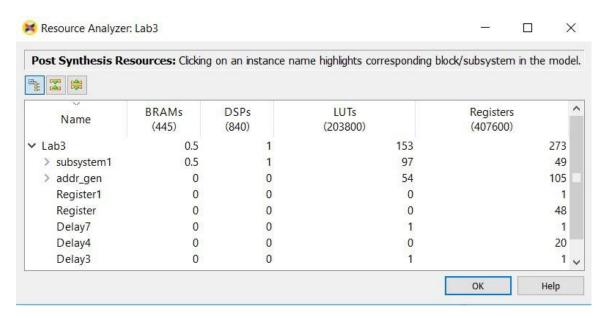

Model Comoser processes the resource utilization data and displays a Resource Analyzer window with resource utilization information.

Each column heading (for example, BRAMs, DSPs, or LUTs) in the window shows the total number of each type of resources available in the Xilinx device for which you are targeting your design. The rest of the window displays a hierarchical listing of each subsystem and block in the design, with the count of these resource types.

4. You can cross probe from the Resource Analyzer window to the Simulink model by clicking a block or subsystem name in the Resource Analyzer window, which highlights the corresponding Model Composer HDL block or subsystem in the model.

Cross probing is useful to identify blocks and subsystems that are implemented using a particular type of resource.

6. If the block or subsystem you have selected in the window is within an upper-level subsystem, then the parent subsystem is highlighted in red in addition to the underlying block as shown in the following figure.

**IMPORTANT!** If the Resource Analyzer window or the Timing Analyzer window opens and no information is displayed in the window (table cells are empty), double-click the System Generator token and set the Target directory to a new directory, that is, a directory that has not been used before. Then run the analysis again.

## Summary

In this lab you learned how to use timing and resource analysis inside Model Composer which, in turn, invokes Vivado synthesis to collect the information for the analysis. You also learned how to identify timing violated paths and to troubleshoot them for simple designs.

# Lab 4: Working with Multi-Rate Systems

In this lab exercise, you will learn how to efficiently implement designs with multiple data rates using multiple clock domains.

## Objectives

After completing this lab, you will be able to:

Understand the benefits of using multiple clock domains to implement multi-rate designs.

- Understand how to isolate hierarchies using FIFOs to create safe channels for transferring asynchronous data.

- How to implement hierarchies with different clocks.

#### **Procedure**

This lab has three primary parts:

- In Step 1, you will learn how to create hierarchies between the clock domains.

- In Step 2, you will learn how to add FIFOs between the hierarchies.

- In Step 3, you will learn how to add separate clock domains for each hierarchy.

# **Step 1: Creating Clock Domain Hierarchies**

In this step you will review a design in which different parts of the design operate at different data rates and partition the design into subsystems to be implemented in different clock domains.

- 1. Invoke Model Composer:

- On Windows systems select Windows → Xilinx Design Tools → Vitis Model Composer 2021.1.

- On Linux systems, type model\_composer at the command prompt.

- 2. Navigate to the Lab4 folder: \HDL\_Library\Lab4.

- 3. At the command prompt, type open Lab4\_1.slx.

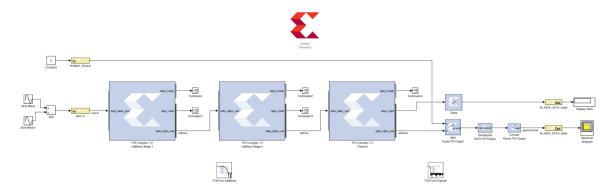

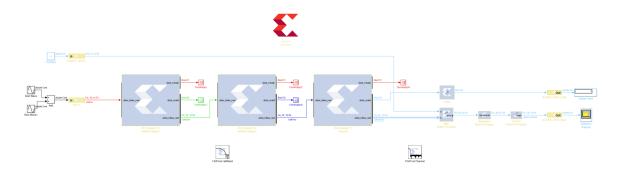

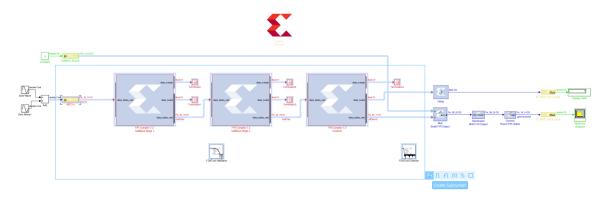

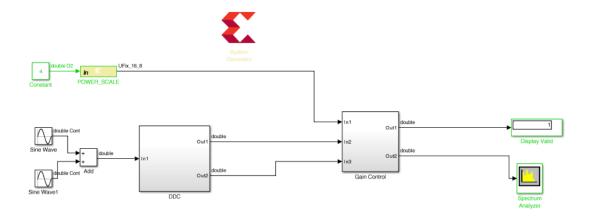

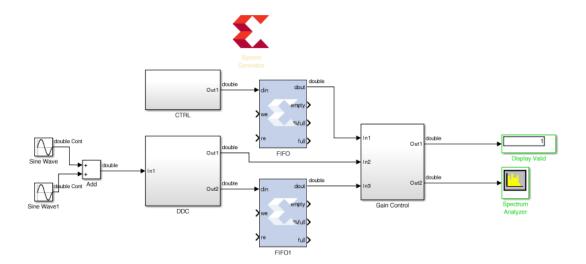

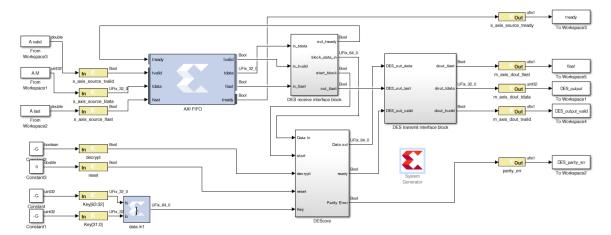

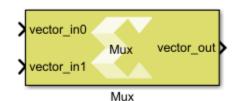

This opens the Simulink design shown in the following figure. This design is composed of three basic parts:

- The channel filter digitally converts the incoming signal (491.52 MSPS) to near baseband (61.44 MSPS) using a classic multi-rate filter: the use of two half-band filters followed by a decimation of 2 stage filter, which requires significantly fewer coefficients than a single large filter.

- The output section gain-controls the output for subsequent blocks which will use the data.

- The gain is controlled from the POWER\_SCALE input.

4. Click the Run simulation button to simulate the design.

In the following figure Sample Time Display is enabled with colors (right-click in the canvas, Sample Time Display  $\rightarrow$  Colors), and shows clearly that the design is running at multiple data rates.

5. The Model Composer environment automatically propagates the different data rates through the design.

When a multi-rate design such as this is implemented in hardware, the most optimal implementation is to use a clock at the same frequency as the data; however, the clock is abstracted away in this environment. The following methodology demonstrates how to create this ideal implementation in the most efficient manner.

- 6. To efficiently implement a multi-rate (or multi-clock) design using Model Composer you should capture each part running at the same data rate (or clock frequency) in its own hierarchy with its own System Generator token. The separate hierarchies should then be linked with FIFOs.

- 7. The current design has two obvious, and one less obvious, clock domains:

- The gain control input POWER\_SCALE could be configurable from a CPU and therefore can run at the same clock frequency as the CPU.

- The actual gain-control logic on the output stage should run at the same frequency as the output data from the FIR. This will allow it to more efficiently connect to subsequent blocks in the system.

• The less obvious region is the filter-chain. Remember from Lab 1 that complex IP provided with Model Composer, such as the FIR Compiler, automatically takes advantage of oversampling to provide the most efficient hardware. For example, rather than use 40 multipliers running at 100 MHz, the FIR Compiler will use only eight multipliers if clocked at 500 MHz (= 40\*100/500). The entire filter chain can therefore be grouped into a single clock domain. The first FIR Compiler instance will execute at the maximum clock rate and subsequent instances will automatically take advantage of over-sampling.

You will start by grouping these regions into different hierarchies.

- 8. Select all the blocks in the filter chain all those to be in the same clock domain, including the FDATool instances as shown in the following figure.

- 9. Select **Create Subsystem**, also as shown in the following figure, to create a new subsystem.

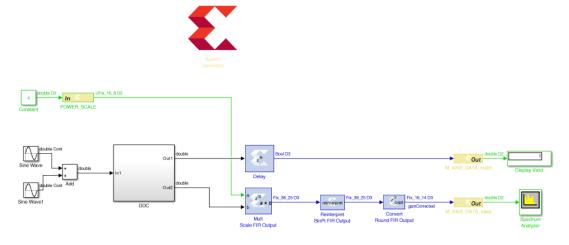

10. Select the instance name subsystem and change this to DDC to obtain the design shown.

11. Select the components in the output path and create a subsystem named Gain Control.

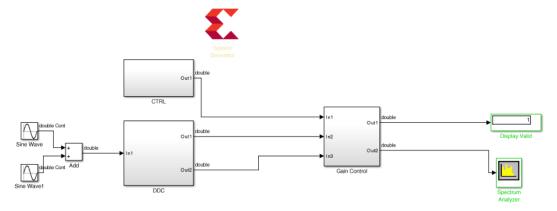

12. Finally, select the Gateway In instance **POWER\_SCALE** and **Constant** to create a new subsystem called CTRL. The final grouped design is shown in the following figure.

When this design is complete, the logic within each subsystem will execute at different clock frequencies. The clock domains might not be synchronous with each other. There is presently nothing to prevent incorrect data being sampled between one subsystem and another subsystem.

In the next step you will create asynchronous channels between the different domains to ensure data will asynchronously and safely cross between the different clock domains when the design is implemented in hardware.

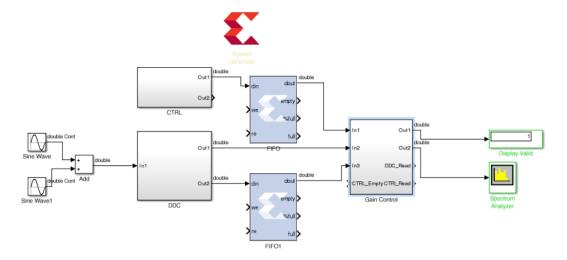

## **Step 2: Creating Asynchronous Channels**

In this step you will implement asynchronous channels between subsystems using FIFOs. The data in FIFOs operates on a First-In-First-Out (FIFO) basis, and control signals ensure data is only read when valid data is present and data is only written when there is space available. If the FIFO is empty or full the control signals will stall the system. In this design the inputs will always be capable of writing and there is no requirement to consider the case for the FIFO being full.

There are two data paths in the design where FIFOs are required:

- Data from CTRL to Gain Control.

- Data from DDC to Gain Control.

- 1. Right-click anywhere in the canvas and select Xilinx BlockAdd.

- 2. Type FIFO in the Add Block dialog box.

- 3. Select FIFO from the menu to add a FIFO to the design.

- 4. Connect the data path through instance FIFO. Delete any existing connections to complete this task.

- a. Connect CTRL/Out1 to FIFO/din.

- b. Connect FIFO/dout to Gain Control/In1.

- 5. Make a copy of the FIFO instance (using Ctrl-C and Ctrl-V to copy and paste).

- 6. Connect the data path through instance FIFO1. Delete any existing connections to complete this task.

- a. Connect DDC/Out2 to FIFO1/din.

- b. Connect FIFO1/dout to Gain Control/In3.

You have now connected the data between the different domains and have the design shown in the following figure.

You will now connect up the control logic signals to ensure the data is safely passed between domains.

- From the CTRL block a write enable is required. This is not currently present and needs to be created.

- From the DDC block a write enable is required. The data\_tvalid from the final FIR stage can be used for this.

- The Gain Control must generate a read enable for both FIFOs. You will use the empty signal from the FIFOs and invert it; if there is data available, this block will read it.

- 7. Double-click the **CTRL** block to open the subsystem.

- 8. Right-click in the canvas and use **Xilinx BlockAdd** to add these blocks:

- a. Delay (Xilinx)

- b. Relational

- 9. Select instance Out1 and make a copy (use Ctrl-C and Ctrl-V to cut and paste).

- 10. Double-click the **Relational** block to open the Properties Editor.

- 11. Use the Comparison drop-down menu to select a!=b and click OK.

- 12. Connect the blocks as shown in the following figure.

This will create an output strobe on Out2 which will be active for one cycle when the input changes, and be used as the write-enable from CTRL to the Gain Control (the FIFO block at the top level).

- 13. Click the **Up to Parent** toolbar button  $\widehat{\mathbf{T}}$  to return to the top level.

- 14. Double-click the instance Gain Control to open the subsystem.

- 15. Right-click in the canvas and use Xilinx BlockAdd to add these blocks:

- a. Inverter

- b. Inverter (for a total of two inverters)

- c. Delay (Xilinx)

- 16. Select the instance Out1 and make a copy Out3 (use Ctrl-C and Ctrl-V to cut and paste).

- Rename Out3 to DDC\_Read

- 17. Select instance Out1 and make a copy Out3 (use Ctrl-C and Ctrl-V to cut and paste).

- Rename Out3 to CTRL\_Read

- 18. Select instance In1 and make a copy In4 (use Ctrl-C and Ctrl-V to cut and paste).

- Rename In4 to CTRL\_Empty

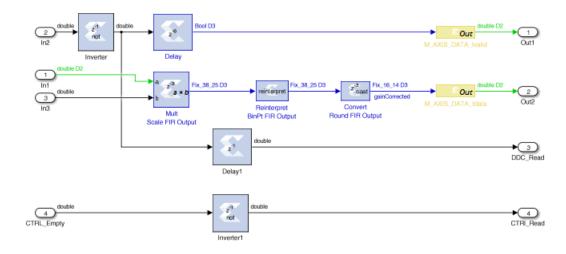

- 19. Connect the blocks as shown in the following figure.

- The FIFO empty signal from the top-level Gain Control FIFO (FIFO) block is simply an inverter block used to create a read-enable for the top-level DDC FIFO (FIFO1). If the FIFO is not empty, the data will be read.

- Similarly, the FIFO empty signal from the top-level DDC FIFO (FIFO1) is inverted to create a FIFO read-enable.

- This same signal will be used as the new data\_tvalid (which was In2). However, because the FIFO has a latency of 1, this signal must be delayed to ensure this control signal is correctly aligned with the data (which is now delayed by 1 through the FIFO).

- 20. Use the **Up to Parent** toolbar button  $\stackrel{\frown}{\mathbf{1}}$  to return to the top level.

This shows the control signals are now present at the top level.

You will now complete the final connections.

- 21. Connect the control path through instance FIFO. Delete any existing connections to complete this task.

- a. Connect CTRL/Out 2 to FIFO/we.

- b. Connect FIFO/empty to Gain Control/CTRL\_Empty.

- c. Connect Gain Control/CTRL\_Read to FIFO/re.

- 22. Connect the control path through instance FIFO1. Delete any existing connections to complete this task.

- a. Connect DDC/Out1 to FIFO1/we.

- b. Connect FIFO1/empty to Gain Control/In2.

- c. Connect Gain Control/DDC\_Read to FIFO1/re.

23. Click the Run simulation button to simulate the design and confirm the correct operation – you will see the same results as Step 1 action 4.

In the next step, you will learn how to specify different clock domains are associated with each hierarchy.

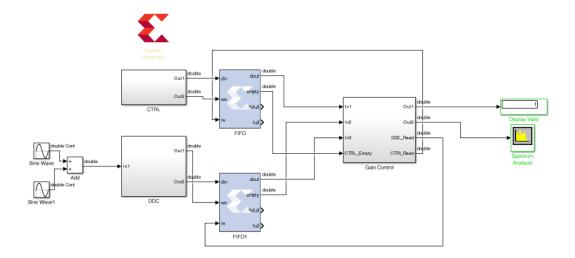

### **Step 3: Specifying Clock Domains**

In this step you will specify a different clock domain for each subsystem.

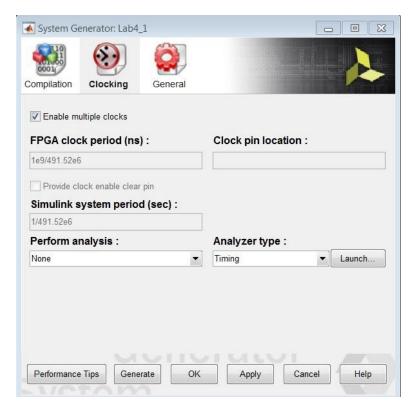

- 1. Double-click the System Generator token to open the Properties Editor.

- 2. Select the Clocking tab.

- 3. Click Enable multiple clocks.

**Note:** The FPGA clock period and the Simulink system period are now greyed out. This option informs Model Composer that clock rate will be specified separately for each hierarchy. It is therefore important the top level contains only subsystems and FIFOs; no other logic should be present at the top level in a multi-rate design.

4. Click **OK** to close the Properties Editor.

You will now specify a new clock rate for the CTRL block. The CTRL block will be driven from a CPU which executes at 100 MHz.

- 5. Select the **System Generator** token.

- 6. Press the Ctrl+C key or right-click to copy the token.

You will specify a new clock rate for the CTRL block. This block will be clocked at 100 MHz and accessed using an AXI4-Lite interface.

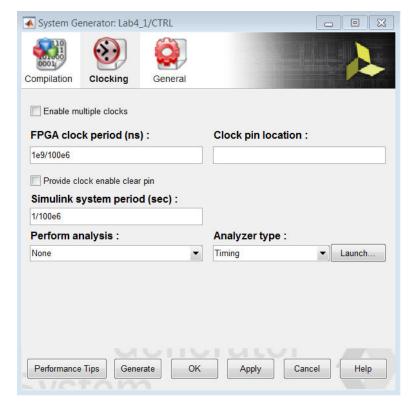

- 7. Double-click the **CTRL** block to navigate into the subsystem.

- 8. Press the Ctrl+V key or right-click to paste a System Generator token into CTRL.

- 9. Double-click the **System Generator** token to open the Properties Editor.

- 10. Select the Clocking tab.

- 11. Deselect Enable multiple clocks (this was inherited when the token was copied).

- 12. Change the FPGA clock period to 1e9/100e6.

- 13. Change the Simulink system period to 1/100e6.

- 14. Click **OK** to close the Properties Editor.

- 15. Double-click the Gateway In instance **POWER\_SCALE** to open the Properties Editor.

- 16. Change the Sample period to 1/100e6 to match the new frequency of this block.

In the Implementation tab, note that the Interface is set to AXI4-Lite. This will ensure this port is implemented as a register in an AXI4-Lite interface.

- 17. Click **OK** to close the Properties Editor.

- 18. Select and copy the System Generator token.

- 19. Click the **Up to Parent** toolbar button to return to the top level.

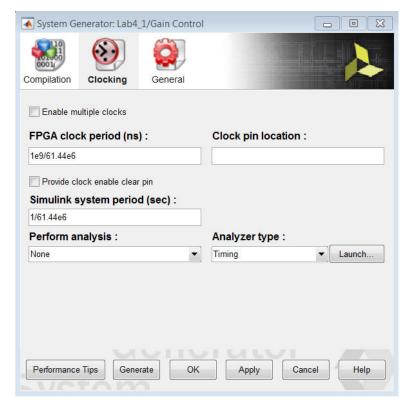

You will now specify a new clock rate for the Gain Control block. The Gain Control block will be clocked at the same rate as the output from the DDC, 61.44 MHz.

- 20. Double-click the **Gain Control** block to navigate into the subsystem.

- 21. Press the Ctrl+V key or right-click to paste a System Generator token into Gain Control.

- 22. Double-click the **System Generator** token to open the Properties Editor.

- 23. Select the Clocking tab.

- 24. Change the FPGA clock period to 1e9/61.44e6.

- 25. Change the Simulink system period to 1/61.44e6.

26. Click **OK** to close the Properties Editor.

Note that the output signals are prefixed with  $M_AXI_DATA_$ . This will ensure that each port will be implemented as an AXI4 interface, because the suffix for both signals is a valid AXI4 signal name (tvalid and tdata).

27. Click the **Up to Parent** toolbar button to return to the top level.

The DDC block uses the same clock frequency as the original design, 491 MHz, because this is the rate of the incoming data.

- 28. In the top-level design, select and copy the System Generator token.

- 29. Double-click the **DDC** block to navigate into the subsystem.

- 30. Press the Ctrl+V key or right-click to paste a System Generator token into the DDC.

- 31. Double-click the **System Generator** token to open the Properties Editor.

- 32. Select the Clocking tab.

- Deselect Enable multiple clocks. The FPGA clock period and Simulink system period are now set to represent 491 MHz.

- 34. Click **OK** to close the Properties Editor.

- 35. Use the **Up to Parent** toolbar button to return to the top level.

- 36. Save the design.

- 37. Click the Run simulation button to simulate the design and confirm the same results as earlier.

The design will now be implemented with three clock domains.

- 38. Double-click the top-level **System Generator** token to open the Properties Editor.

- 39. Click **Generate** to compile the design into a hardware description.

- 40. Click **Yes** to dismiss the simulation warning.

- 41. When generation completes, click **OK** to dismiss the Compilation status dialog box.

- 42. Click **OK** to dismiss the System Generator token.

- 43. Open the file \HDL\_Library\Lab4\IPP\_QT\_MCD\_0001\DDC\_HB\_hier\ip\hdl \lab4\_1.vhd to confirm the design is using three clocks, as shown in the following.

```

entity lab4_1 is

port (

ctrl_clk : in std_logic;

ddc_clk : in std_logic;

gain_control_clk : in std_logic;

```

### **Summary**

In this lab, you learned how to create separate hierarchies for portions of the design which are to be implemented with different clock rates. You also learned how to isolate those hierarchies using FIFOs to ensure safe asynchronous transfer of the data and how to specify the clock rates for each hierarchy.

The following solution directory contains the final Model Composer (\* . slx) files for this lab. The solution directory does not contain the IP output from Model Composer or the files and directories generated by Vivado.

/HDL\_Library/Lab4/solution

- The results from Step 1 are provided in file Lab4\_1\_sol.slx

- The results from Step 2 are provided in file Lab4\_2\_sol.slx

- The final results from Step 3 are provided in file Lab4\_3\_sol.slx

## Lab 5: Using AXI Interfaces and IP Integrator

In this lab, you will learn how AXI interfaces are implemented using Model Composer. You will save the design in IP catalog format and use the resulting IP in the Vivado<sup>®</sup> IP integrator environment. Then you will see how IP integrator enhances your productively by supplying connection assistance when you use AXI interfaces.

### **Objectives**

After completing this lab, you will be able to:

- Implement AXI interfaces in your designs.

- Add your design as IP in the Vivado IP catalog.

- Connect your design in IP integrator.

#### **Procedure**

This lab has four primary parts:

- In Step 1, you will review how AXI interfaces are implemented using Model Composer.

- In Step 2, you will create a Vivado project for your Model Composer IP.

- In Step 3, you will create a design in IP integrator using the Model Composer IP.

- In Step 4, you will implement the design and generate an FPGA bitstream (the file used to program the FPGA).

### **Step 1: Review the AXI Interfaces**

In this step you review how AXI interfaces are defined and created.

- 1. Invoke Vitis Model Composer and use the Current Folder browser to change the directory to \HDL\_Library\Lab5.

- 2. Type open Lab5\_1.slx in the Command Window.

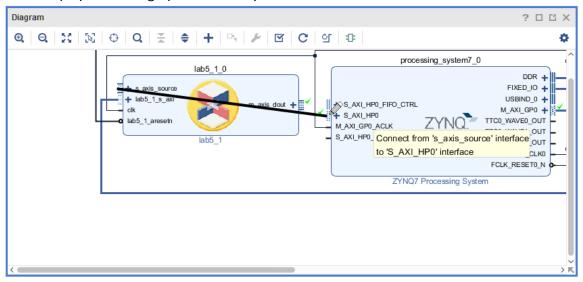

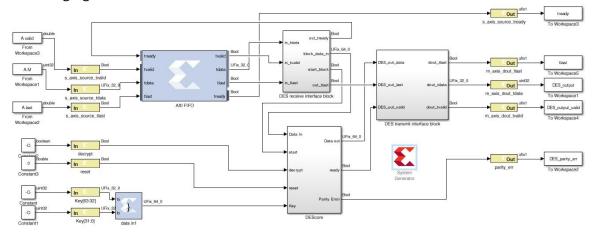

This opens the design shown in the following figure.

This design uses a number of AXI interfaces. You will review these shortly.

- Using AXI interfaces allows a design exported to the Vivado IP catalog to be efficiently integrated into a larger system using IP integrator.

- It is not a requirement for designs exported to the IP catalog to use AXI interfaces.

This design uses the following AXI interfaces:

- An AXI4-Stream interface is used for ports <code>s\_axis\_source\_\*</code>. All Gateway In and Out signals are prefixed with the same name (<code>s\_axis\_source\_</code>), ensuring they are grouped into the same interface. The suffixes for all ports are valid AXI4-Stream interface signal names (<code>tready</code>, <code>tvalid</code>, <code>tlast</code> and <code>tdata</code>).

- An AXI4-Stream interface is used for ports m\_axis\_dout\_\*.

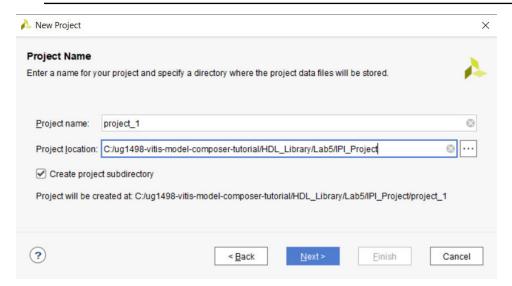

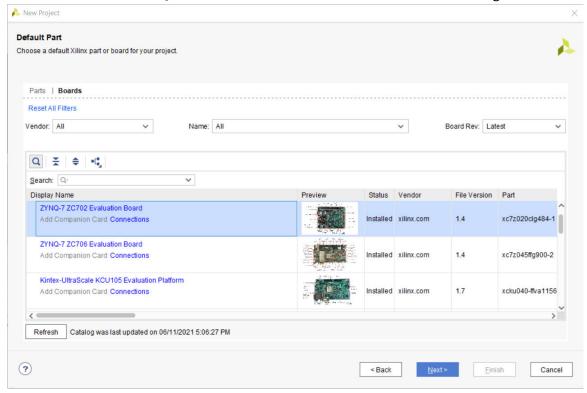

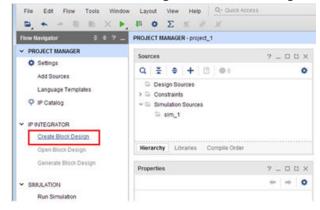

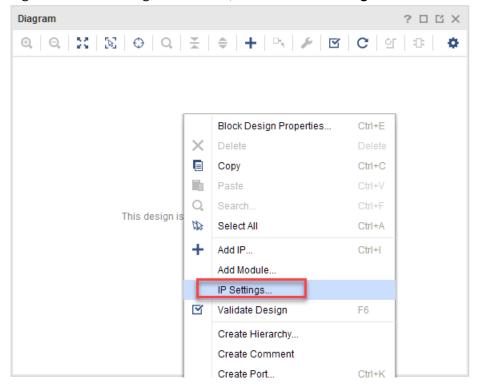

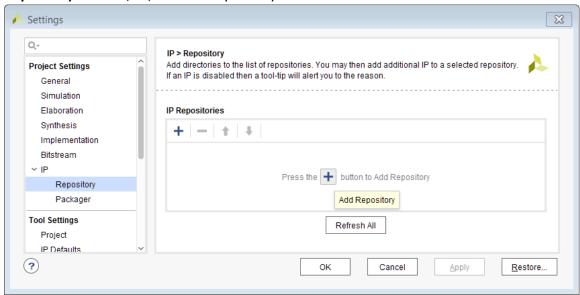

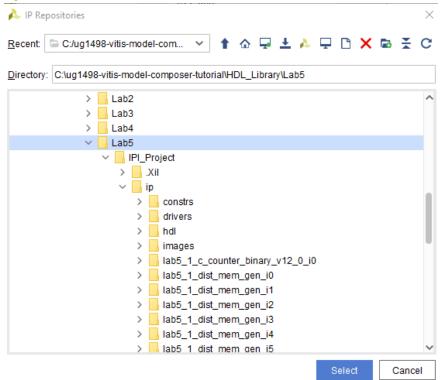

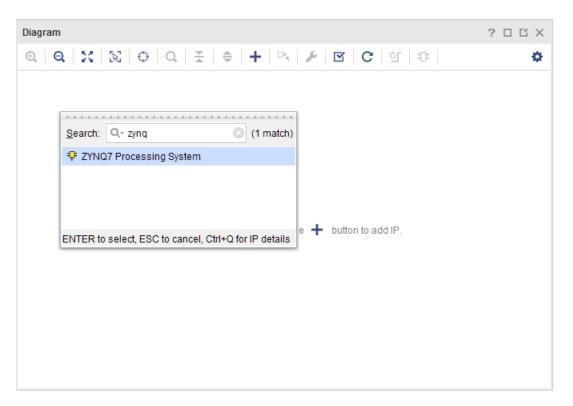

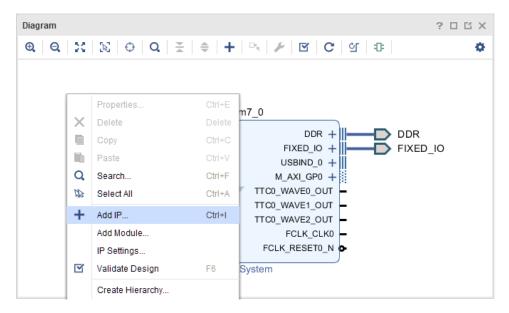

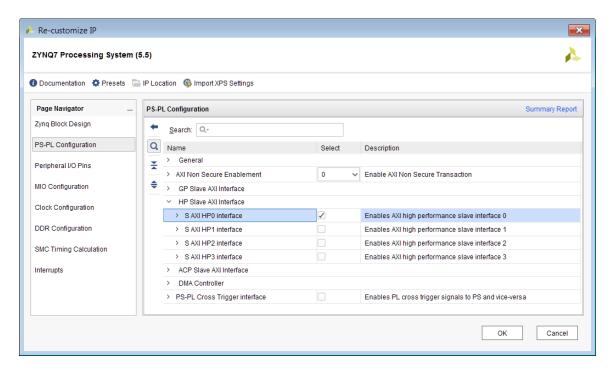

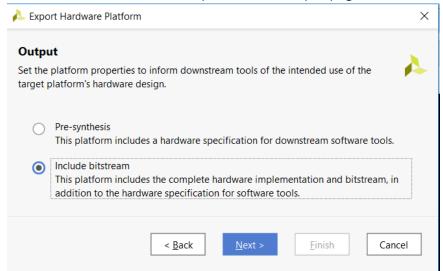

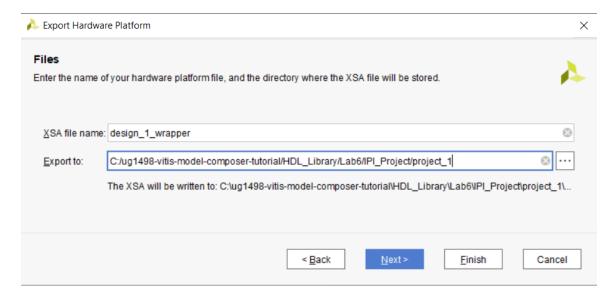

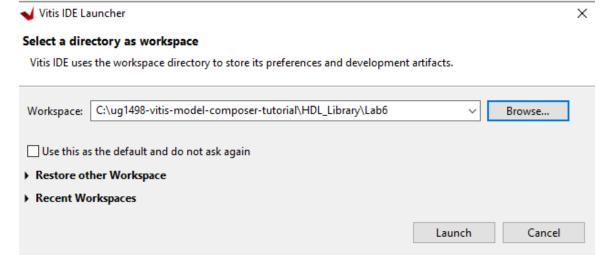

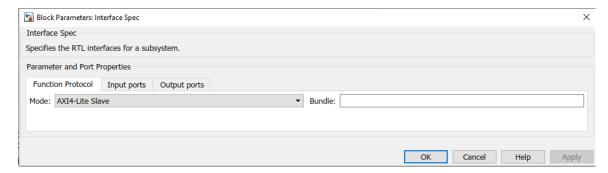

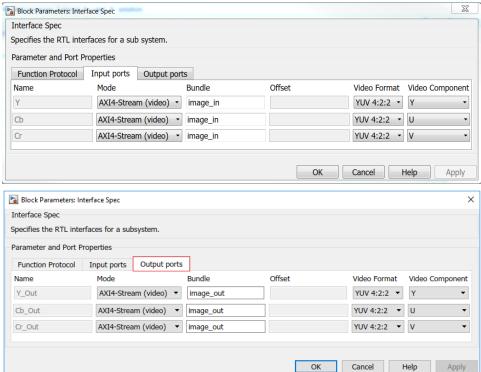

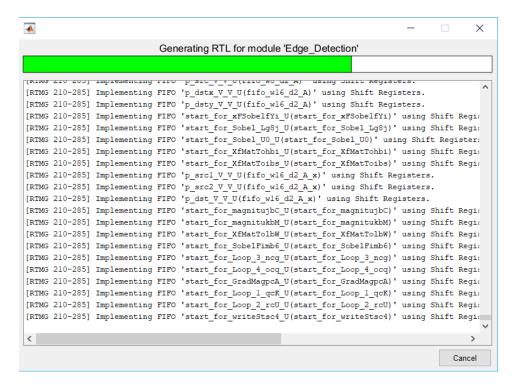

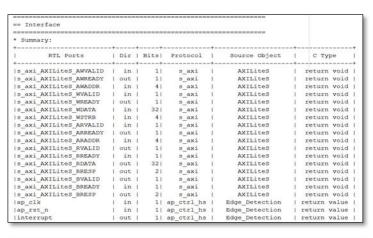

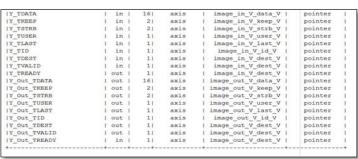

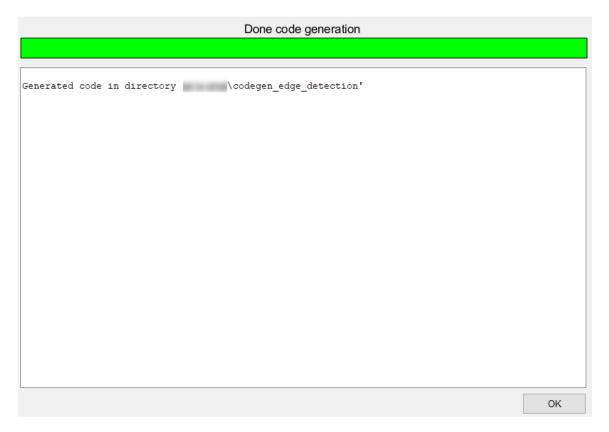

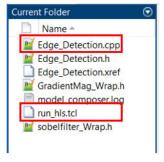

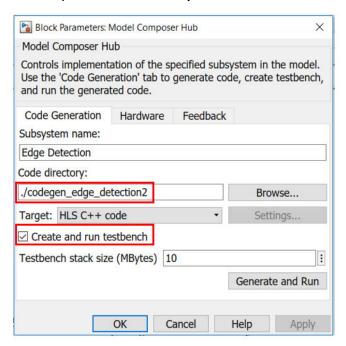

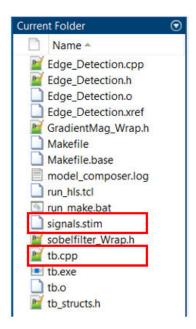

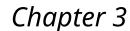

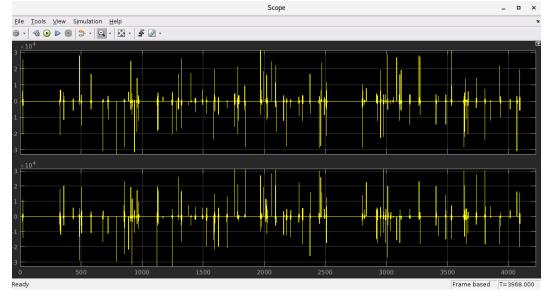

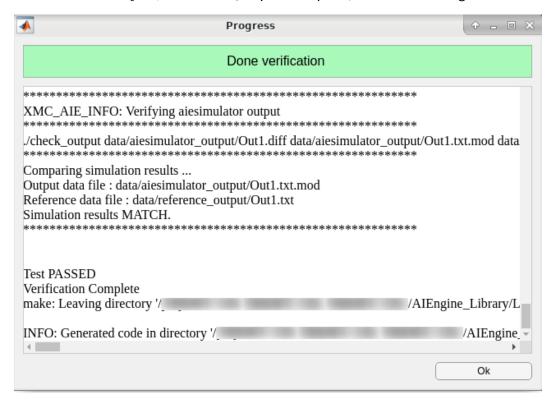

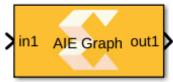

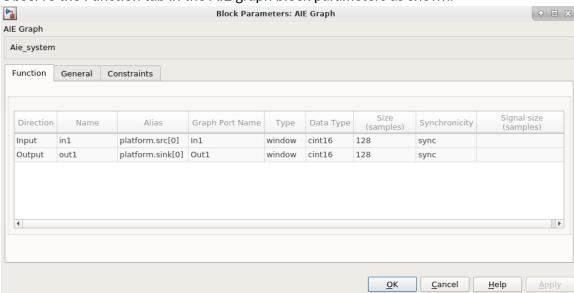

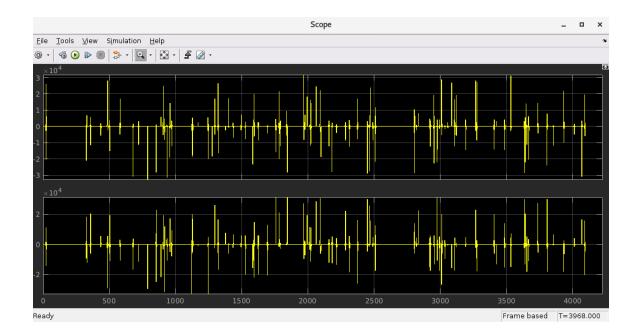

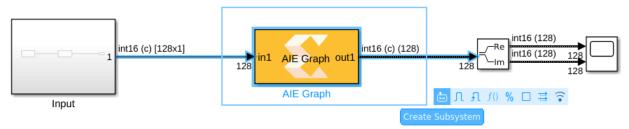

- An AXI4-Lite interface is used for the remaining ports. You can confirm this using the following steps: