# MicroBlaze Processor Reference Guide

UG984 (v2021.2) October 27, 2021

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing non-inclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this link for more information.

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 10/27/2021 | 2021.2  | Updated for Vivado 2021.2 release                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|            |         | Added Artix UltraScale+ device                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 06/16/2021 | 2021.1  | <ul> <li>Jpdated for Vivado 2021.1 release</li> <li>Corrected MSRCLR and MSRSET in MicroBlaze Instruction Set Summary.</li> <li>Corrected TNAPUTD and TNCAPUTD in MicroBlaze Instruction Set Summary.</li> <li>Provided additional information on AXI and ACE interface parameters.</li> <li>Added missing description of Dbg_Disable signal.</li> </ul>                                   |  |  |  |  |

| 11/18/2020 | 2020.2  | <ul> <li>Updated for Vivado 2020.2 release</li> <li>Corrected parity bits in a data cache line.</li> <li>Added Versal to supported families.</li> <li>Clarified atomic stream instruction behavior.</li> <li>Provided performance and resource utilization for Versal.</li> </ul>                                                                                                          |  |  |  |  |

| 06/03/2020 | 2020.1  | <ul> <li>Updated for Vivado 2020.1 release</li> <li>Added ELF format description.</li> <li>Describe Memory Protection feature in more detail.</li> <li>Clarified Peripheral Data AXI write behavior.</li> <li>Define FINT and DLONG instruction rounding behavior.</li> </ul>                                                                                                              |  |  |  |  |

| 10/30/2019 | 2019.2  | <ul> <li>Updated for Vivado 2019.2 release:</li> <li>Updated description of 64-bit immediate instructions with added opcodes.</li> <li>Clarified reset behavior.</li> <li>Replaced SDK with Vitis.</li> <li>Added Block-RAM count to resource utilization tables.</li> </ul>                                                                                                               |  |  |  |  |

| 24/04/2019 | 2019.1  | <ul> <li>Updated for Vivado 2019.1 release:</li> <li>Added information about cache reset behavior.</li> <li>Included calling convention for variable argument functions.</li> <li>Corrected WDC pseudo code.</li> <li>Provided link to MicroBlaze pages on the Xilinx Wiki.</li> </ul>                                                                                                     |  |  |  |  |

| 11/14/2018 | 2018.3  | <ul><li>Updated for Vivado 2018.3 release:</li><li>Added description of MicroBlaze 64-bit implementation, new in version 11.0.</li></ul>                                                                                                                                                                                                                                                   |  |  |  |  |

| 04/04/2018 | 2018.1  | <ul> <li>Updated for Vivado 2018.1 release:</li> <li>Included information about instruction pipeline hazards and forwarding.</li> <li>Clarified that software break does not set the BIP bit in MSR.</li> <li>Explained memory scrubbing behavior.</li> <li>Added more detailed description of sleep and pause usage.</li> <li>Clarified use of parallel debug clock and reset.</li> </ul> |  |  |  |  |

| 10/04/2017 | 2017.3  | <ul> <li>Updated for Vivado 2017.3 release:</li> <li>Added automotive UltraScale+ Zynq and Spartan-7 devices.</li> <li>Updated description of debug trace, to add event trace, new in version 10.0.</li> <li>Added 4PB extended address size.</li> <li>Clarified description of cache trace signals.</li> </ul>                                                                            |  |  |  |  |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 04/05/2017 | 2017.1  | <ul> <li>Updated for Vivado 2017.1 release:</li> <li>Added description of MMU Physical Address Extension (PAE), new in version 10.0.</li> <li>Extended privileged instruction list, and updated instruction descriptions.</li> <li>Updated information on debug program trace.</li> <li>Added reference to the Triple Modular Redundancy (TMR) subsystem.</li> <li>Corrected description of BSIFI instruction.</li> <li>Updated MFSE instruction description with PAE information.</li> <li>Added MTSE instruction used with PAE, new in version 10.0.</li> <li>Updated WDC instruction for external cache invalidate and flush.</li> </ul>                                                                                                                                                               |  |  |  |  |

| 10/05/2016 | 2016.3  | <ul> <li>Updated for Vivado 2016.3 release:</li> <li>Added description of frequency optimized 8-stage pipeline, new in version 10.0.</li> <li>Describe bit field instructions, new in version 10.0.</li> <li>Include information on parallel debug interface, new in version 10.0.</li> <li>Added version 10.0 to MicroBlaze release version code in PVR.</li> <li>Included Spartan-7 target architecture in PVR.</li> <li>Updated description of MSR reset value.</li> <li>Updated Xilinx</li> </ul>                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 04/06/2016 | 2016.1  | <ul> <li>Updated for Vivado 2016.1 release:</li> <li>Included description of address extension, new in version 9.6.</li> <li>Included description of pipeline pause functionality, new in version 9.6</li> <li>Included description of non-secure AXI access support, new in version 9.6.</li> <li>Included description of hibernate and suspend instructions, new in version 9.6.</li> <li>Added version 9.6 to MicroBlaze release version code in PVR.</li> <li>Corrected references to Table 2-47 and Table 2-48.</li> <li>Replaced references to the deprecated Xilinx Microprocessor Debugger (XMD) with Xilinx System Debugger (XSDB).</li> <li>Removed C code function attributes svc_handler and svc_table_handler.</li> </ul>                                                                    |  |  |  |  |

| 04/15/2015 | 2015.1  | <ul> <li>Updated for Vivado 2015.1 release:</li> <li>Included description of 16 word cache line length, new in version 9.5.</li> <li>Added version 9.5 to MicroBlaze release version code in PVR.</li> <li>Corrected description of supported endianness and parameter C_ENDIANNESS.</li> <li>Corrected description of outstanding reads for instruction and data cache.</li> <li>Updated FPGA configuration memory protection document reference [Ref 5].</li> <li>Corrected Bus Index Range definitions for Lockstep Comparison in Table 3-14.</li> <li>Clarified registers altered for IDIV instruction.</li> <li>Corrected PVR assembler mnemonics for MFS instruction.</li> <li>Updated performance and resource utilization for 2015.1.</li> <li>Added references to training resources.</li> </ul> |  |  |  |  |

| 10/01/2014 | 2014.3  | <ul> <li>Updated for Vivado 2014.3 release:</li> <li>Corrected semantic description for PCMPEQ and PCMPNE in Table 2.1.</li> <li>Added version 9.4 to MicroBlaze release version code in PVR.</li> <li>Included description of external program trace, new in version 9.4</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/02/2014 | 2014.1  | <ul> <li>Updated for Vivado 2014.1 release:</li> <li>Added v9.3 to MicroBlaze release version code in PVR.</li> <li>Clarified availability and behavior of stack protection registers.</li> <li>Corrected description of LMB instruction and data bus exception.</li> <li>Included description of extended debug features, new in version 9.3: performance monitoring, program trace and non-intrusive profiling.</li> <li>Included definition of Reset Mode signals, new in version 9.3.</li> <li>Clarified how the AXI4-Stream TLAST signal is handled.</li> <li>Added UltraScale and updated performance and resource utilization for 2014.1.</li> </ul> |

| 12/18/2013 | 2013.4  | Updated for Vivado 2013.4 release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10/02/2013 | 2013.3  | Updated for Vivado 2013.3 release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 06/19/2013 | 2013.2  | Updated for Vivado 2013.2 release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 03/20/2013 | 2013.1  | Initial Xilinx release. This User Guide is derived from UG081.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **Table of Contents**

| Chapter 1: Introduction                            |     |

|----------------------------------------------------|-----|

| Guide Contents                                     | 7   |

| Chapter 2: MicroBlaze Architecture                 |     |

| Introduction                                       | 8   |

| Overview                                           | 8   |

| Data Types and Endianness                          | 12  |

| Instructions                                       | 14  |

| Registers                                          | 29  |

| Pipeline Architecture                              | 56  |

| Memory Architecture                                | 62  |

| Privileged Instructions                            | 63  |

| Virtual-Memory Management                          | 65  |

| Reset, Interrupts, Exceptions, and Break           | 80  |

| Instruction Cache                                  |     |

| Data Cache                                         |     |

| Floating-Point Unit (FPU)                          |     |

| Stream Link Interfaces                             |     |

| Debug and Trace                                    |     |

| Fault Tolerance                                    | 129 |

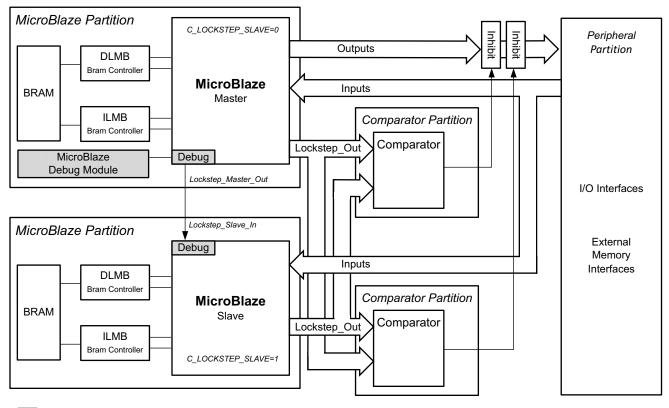

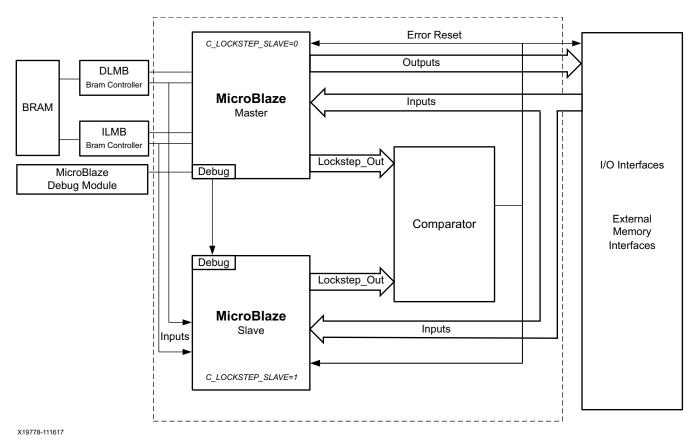

| Lockstep Operation                                 | 137 |

| Coherency                                          |     |

| Data and Instruction Address Extension             |     |

| Chapter 3: MicroBlaze Signal Interface Description |     |

|                                                    | 145 |

| Introduction                                 | 145 |

|----------------------------------------------|-----|

| Overview                                     | 145 |

| MicroBlaze I/O Overview                      | 146 |

| AXI4 and ACE Interface Description           | 159 |

| Local Memory Bus (LMB) Interface Description | 165 |

| Lockstep Interface Description               | 174 |

| Debug Interface Description                  | 179 |

| Trace Interface Description                  | 181 |

# **E** XILINX<sub>®</sub>

|  | MicroBlaze Core Configurability |  | 184 |

|--|---------------------------------|--|-----|

|--|---------------------------------|--|-----|

#### **Chapter 4: MicroBlaze Application Binary Interface**

| Introduction                            | 196 |

|-----------------------------------------|-----|

| Data Types                              | 196 |

| Register Usage Conventions              | 197 |

| Stack Convention                        | 199 |

| Memory Model                            | 201 |

| Interrupt, Break and Exception Handling | 202 |

| Reset Handling                          | 204 |

| ELF Format                              | 205 |

#### **Chapter 5: MicroBlaze Instruction Set Architecture**

| Introduction                   | 209 |

|--------------------------------|-----|

| Notation                       | 209 |

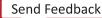

| Formats                        | 211 |

| MicroBlaze 32-bit Instructions | 211 |

| MicroBlaze 64-bit Instructions | 320 |

#### Appendix A: Performance and Resource Utilization

| Performance                                                        | 383 |

|--------------------------------------------------------------------|-----|

| Resource Utilization                                               | 384 |

| IP Characterization and f <sub>MAX</sub> Margin System Methodology | 393 |

#### **Appendix B: Additional Resources and Legal Notices**

| Xilinx Resources                        | 394 |

|-----------------------------------------|-----|

| Solution Centers                        | 394 |

| Documentation Navigator and Design Hubs | 394 |

| References                              | 395 |

| Training Resources                      | 396 |

| Please Read: Important Legal Notices    | 396 |

Chapter 1

# Introduction

The MicroBlaze<sup>™</sup> Processor Reference Guide provides information about the 32-bit and 64bit soft processor, MicroBlaze, which is included in Vivado. The document is intended as a guide to the MicroBlaze hardware architecture.

# **Guide Contents**

This guide contains the following chapters:

- Chapter 2, MicroBlaze Architecture contains an overview of MicroBlaze features as well as information on Big-Endian and Little-Endian bit-reversed format, 32-bit or 64-bit general purpose registers, cache software support, and AXI4-Stream interfaces.

- Chapter 3, MicroBlaze Signal Interface Description describes the types of signal interfaces that can be used to connect MicroBlaze.

- Chapter 4, MicroBlaze Application Binary Interface describes the Application Binary Interface important for developing software in assembly language for the processor.

- Chapter 5, MicroBlaze Instruction Set Architecture provides notation, formats, and instructions for the Instruction Set Architecture (ISA) of MicroBlaze.

- Appendix A, Performance and Resource Utilization contains maximum frequencies and resource utilization numbers for different configurations and devices.

- Appendix B, Additional Resources and Legal Notices provides links to documentation and additional resources.

# Chapter 2

# MicroBlaze Architecture

### Introduction

This chapter contains an overview of MicroBlaze<sup>™</sup> features and detailed information on MicroBlaze architecture including Big-Endian or Little-Endian bit-reversed format, 32-bit or 64-bit general purpose registers, virtual-memory management, cache software support, and AXI4-Stream interfaces.

### **Overview**

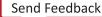

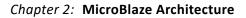

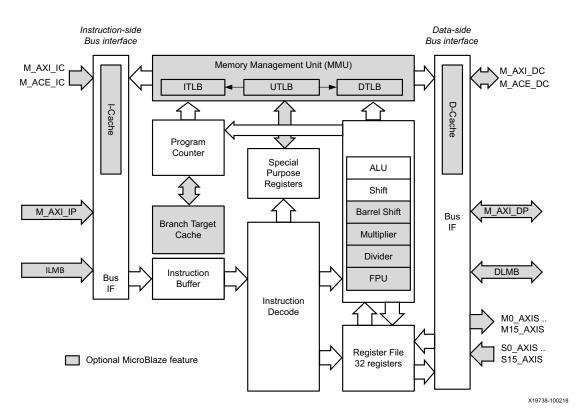

The MicroBlaze embedded processor soft core is a reduced instruction set computer (RISC) optimized for implementation in Xilinx® Field Programmable Gate Arrays (FPGAs). The following figure shows a functional block diagram of the MicroBlaze core.

Figure 2-1: MicroBlaze Core Block Diagram

### Features

The MicroBlaze soft core processor is highly configurable, allowing you to select a specific set of features required by your design.

The fixed feature set of the processor includes:

- Thirty-two 32-bit or 64-bit general purpose registers

- 32-bit instruction word with three operands and two addressing modes

- Default 32-bit address bus, extensible to 64 bits

- Single issue pipeline

In addition to these fixed features, the MicroBlaze processor is parameterized to allow selective enabling of additional functionality. Older (deprecated) versions of MicroBlaze support a subset of the optional features described in this manual. Only the latest (preferred) version of MicroBlaze (v11.0) supports all options.

**RECOMMENDED:** Xilinx recommends that all new designs use the latest **preferred** version of the MicroBlaze processor.

The following table provides an overview of the configurable features by MicroBlaze versions.

| Table 2-1: | <b>Configurable Feature</b> | Overview by | MicroBlaze Version |

|------------|-----------------------------|-------------|--------------------|

|            | configuration cutare        | Ofcificit N |                    |

| Feature                                              | MicroBlaze versions |            |            |            |            |           |

|------------------------------------------------------|---------------------|------------|------------|------------|------------|-----------|

| reature                                              | v9.3                | v9.4       | v9.5       | v9.6       | v10.0      | v11.0     |

| Version Status                                       | deprecated          | deprecated | deprecated | deprecated | deprecated | preferred |

| Processor pipeline depth                             | 3/5                 | 3/5        | 3/5        | 3/5        | 3/5/8      | 3/5/8     |

| Local Memory Bus (LMB) data side interface           | option              | option     | option     | option     | option     | option    |

| Local Memory Bus (LMB)<br>instruction side interface | option              | option     | option     | option     | option     | option    |

| Hardware barrel shifter                              | option              | option     | option     | option     | option     | option    |

| Hardware divider                                     | option              | option     | option     | option     | option     | option    |

| Hardware debug logic                                 | option              | option     | option     | option     | option     | option    |

| Stream link interfaces                               | 0-16 AXI            | 0-16 AXI   | 0-16 AXI   | 0-16 AXI   | 0-16 AXI   | 0-16 AXI  |

| Machine status set and clear instructions            | option              | option     | option     | option     | option     | option    |

| Cache line word length                               | 4, 8                | 4, 8       | 4, 8, 16   | 4, 8, 16   | 4, 8, 16   | 4, 8, 16  |

| Hardware exception support                           | option              | option     | option     | option     | option     | option    |

| Pattern compare instructions                         | option              | option     | option     | option     | option     | option    |

| Floating-point unit (FPU)                            | option              | option     | option     | option     | option     | option    |

| Table 2-1: Configurable Feature Overview by MicroBlaze Version (Cont |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

| Faatura                                                | MicroBlaze versions |        |        |        |        |        |  |

|--------------------------------------------------------|---------------------|--------|--------|--------|--------|--------|--|

| Feature                                                | v9.3                | v9.4   | v9.5   | v9.6   | v10.0  | v11.0  |  |

| Disable hardware multiplier <sup>1</sup>               | option              | option | option | option | option | option |  |

| Hardware debug readable ESR and EAR                    | Yes                 | Yes    | Yes    | Yes    | Yes    | Yes    |  |

| Processor Version Register (PVR)                       | option              | option | option | option | option | option |  |

| Area or speed optimized                                | option              | option | option | option | option | option |  |

| Hardware multiplier 64-bit result                      | option              | option | option | option | option | option |  |

| LUT cache memory                                       | option              | option | option | option | option | option |  |

| Floating-point conversion and square root instructions | option              | option | option | option | option | option |  |

| Memory Management Unit (MMU)                           | option              | option | option | option | option | option |  |

| Extended stream instructions                           | option              | option | option | option | option | option |  |

| Use Cache Interface for All I-Cache<br>Memory Accesses | option              | option | option | option | option | option |  |

| Use Cache Interface for All D-Cache<br>Memory Accesses | option              | option | option | option | option | option |  |

| Use Write-back Caching Policy for<br>D-Cache           | option              | option | option | option | option | option |  |

| Branch Target Cache (BTC)                              | option              | option | option | option | option | option |  |

| Streams for I-Cache                                    | option              | option | option | option | option | option |  |

| Victim handling for I-Cache                            | option              | option | option | option | option | option |  |

| Victim handling for D-Cache                            | option              | option | option | option | option | option |  |

| AXI4 (M_AXI_DP) data side interface                    | option              | option | option | option | option | option |  |

| AXI4 (M_AXI_IP) instruction side interface             | option              | option | option | option | option | option |  |

| AXI4 (M_AXI_DC) protocol for D-<br>Cache               | option              | option | option | option | option | option |  |

| AXI4 (M_AXI_IC) protocol for I-<br>Cache               | option              | option | option | option | option | option |  |

| AXI4 protocol for stream accesses                      | option              | option | option | option | option | option |  |

| Fault tolerant features                                | option              | option | option | option | option | option |  |

| Force distributed RAM for cache tags                   | option              | option | option | option | option | option |  |

| Configurable cache data widths                         | option              | option | option | option | option | option |  |

| Count Leading Zeros instruction                        | option              | option | option | option | option | option |  |

| Memory Barrier instruction                             | Yes                 | Yes    | Yes    | Yes    | Yes    | Yes    |  |

| Stack overflow and underflow<br>detection              | option              | option | option | option | option | option |  |

| Allow stream instructions in user mode                 | option              | option | option | option | option | option |  |

| Table 2-1: Configurable Feature Overview by MicroBlaze Version (Cont'd) | Table 2-1: | Configurable Feature Overvi | ew by MicroBlaze | Version (Cont'd) |

|-------------------------------------------------------------------------|------------|-----------------------------|------------------|------------------|

|-------------------------------------------------------------------------|------------|-----------------------------|------------------|------------------|

| Faatura                                                                               | MicroBlaze versions |        |        |        |        |        |  |

|---------------------------------------------------------------------------------------|---------------------|--------|--------|--------|--------|--------|--|

| Feature                                                                               | v9.3                | v9.4   | v9.5   | v9.6   | v10.0  | v11.0  |  |

| Lockstep support                                                                      | option              | option | option | option | option | option |  |

| Configurable use of FPGA primitives                                                   | option              | option | option | option | option | option |  |

| Low-latency interrupt mode                                                            | option              | option | option | option | option | option |  |

| Swap instructions                                                                     | option              | option | option | option | option | option |  |

| Sleep mode and sleep instruction                                                      | Yes                 | Yes    | Yes    | Yes    | Yes    | Yes    |  |

| Relocatable base vectors                                                              | option              | option | option | option | option | option |  |

| ACE (M_ACE_DC) protocol for D-<br>Cache                                               | option              | option | option | option | option | option |  |

| ACE (M_ACE_IC) protocol for I-<br>Cache                                               | option              | option | option | option | option | option |  |

| Extended debug: performance<br>monitoring, program trace, non-<br>intrusive profiling | option              | option | option | option | option | option |  |

| Reset mode: enter sleep or debug<br>halt at reset                                     | option              | option | option | option | option | option |  |

| Extended debug: external program trace                                                |                     | option | option | option | option | option |  |

| Extended data addressing                                                              |                     |        |        | option | option | option |  |

| Pipeline pause functionality                                                          |                     |        |        | Yes    | Yes    | Yes    |  |

| Hibernate and suspend instructions                                                    |                     |        |        | Yes    | Yes    | Yes    |  |

| Non-secure mode                                                                       |                     |        |        | Yes    | Yes    | Yes    |  |

| Bit field instructions <sup>2</sup>                                                   |                     |        |        |        | option | option |  |

| Parallel debug interface                                                              |                     |        |        |        | option | option |  |

| MMU Physical Address Extension                                                        |                     |        |        |        | option | option |  |

| 64-bit mode                                                                           |                     |        |        |        |        | option |  |

1. Used for saving DSP48E primitives.

2. Bit field instructions are available when C\_USE\_BARREL = 1.

# **Data Types and Endianness**

The MicroBlaze processor uses Big-Endian or Little-Endian format to represent data, depending on the selected endianness. The parameter C\_ENDIANNESS is set to 1 (little-endian) by default.

The hardware supported data types for 32-bit MicroBlaze are word, half word, and byte. With 64-bit MicroBlaze the data types long and double are also available in hardware.

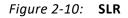

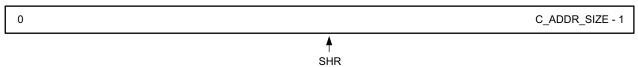

When using the reversed load and store instructions LHUR, LWR, LLR, SHR, SWR and SLR, the bytes in the data are reversed, as indicated by the byte-reversed order.

The following tables show the bit and byte organization for each type.

Table 2-2: Long Data Type (only 64-bit MicroBlaze)

| Big-Endian Byte Address           |

|-----------------------------------|

| Big-Endian Byte Significance      |

| Big-Endian Byte Order             |

| Big-Endian Byte-Reversed Order    |

| Little-Endian Byte Address        |

| Little-Endian Byte Significance   |

| Little-Endian Byte Order          |

| Little-Endian Byte-Reversed Order |

| Bit Label                         |

| Bit Significance                  |

|                                   |

| n      | n+1 | n+2 | n+3 | n+4 | n+5 | n+6 | n+7    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| MSByte |     |     |     |     |     |     | LSByte |

| n      | n+1 | n+2 | n+3 | n+4 | n+5 | n+6 | n+7    |

| n+7    | n+6 | n+5 | n+4 | n+3 | n+2 | n+1 | n      |

| n+7    | n+6 | n+5 | n+4 | n+3 | n+2 | n+1 | n      |

| MSByte |     |     |     |     |     |     | LSByte |

| n+7    | n+6 | n+5 | n+4 | n+3 | n+2 | n+1 | n      |

| n      | n+1 | n+2 | n+3 | n+4 | n+5 | n+6 | n+7    |

| 0      |     |     |     |     |     |     | 63     |

| MSBit  |     |     |     |     |     |     | LSBit  |

#### Table 2-3: Word Data Type

Big-Endian Byte Address Big-Endian Byte Significance Big-Endian Byte Order Big-Endian Byte-Reversed Order Little-Endian Byte Address Little-Endian Byte Significance Little-Endian Byte Order Little-Endian Byte-Reversed Order Bit Label Bit Significance

| n      | n+1 | n+2 | n+3    |

|--------|-----|-----|--------|

| MSByte |     |     | LSByte |

| n      | n+1 | n+2 | n+3    |

| n+3    | n+2 | n+1 | n      |

| n+3    | n+2 | n+1 | n      |

| MSByte |     |     | LSByte |

| n+3    | n+2 | n+1 | n      |

| n      | n+1 | n+2 | n+3    |

| 0      |     |     | 31     |

| MSBit  |     |     | LSBit  |

#### Table 2-4: Half Word Data Type

| Big-Endian Byte Address           | n      | n+1    |

|-----------------------------------|--------|--------|

| Big-Endian Byte Significance      | MSByte | LSByte |

| Big-Endian Byte Order             | n      | n+1    |

| Big-Endian Byte-Reversed Order    | n+1    | n      |

| Little-Endian Byte Address        | n+1    | n      |

| Little-Endian Byte Significance   | MSByte | LSByte |

| Little-Endian Byte Order          | n+1    | n      |

| Little-Endian Byte-Reversed Order | n      | n+1    |

| Bit Label                         | 0      | 15     |

| Bit Significance                  | MSBit  | LSBit  |

#### Table 2-5: Byte Data Type

| Byte Address     | n     |       |

|------------------|-------|-------|

| Bit Label        | 0     | 7     |

| Bit Significance | MSBit | LSBit |

### Instructions

### **Instruction Summary**

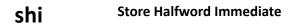

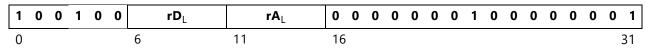

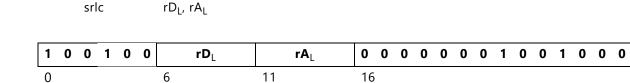

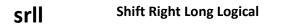

All MicroBlaze instructions are 32 bits and are defined as either Type A or Type B. Type A instructions have up to two source register operands and one destination register operand. Type B instructions have one source register and a 16-bit immediate operand (which can be extended to 32 bits by preceding the Type B instruction with an imm instruction).

Type B instructions have a single destination register operand. Instructions are provided in the following functional categories: arithmetic, logical, branch, load/store, and special. The following table describes the instruction set nomenclature used in the semantics of each instruction. Table 2-6 lists the MicroBlaze instruction set. See Chapter 5, MicroBlaze Instruction Set Architecture, for more information on these instructions.

| Symbol                | Description                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Ra                    | R0 - R31, General Purpose Register, source operand a                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                       | <ul> <li>With 32-bit MicroBlaze represents the entire 32-bit register</li> <li>With 64-bit MicroBlaze and L = 0, represents the 32 least significant bits</li> <li>With 64-bit MicroBlaze and L = 1, represents the entire 64-bit register</li> </ul>                                      |  |  |  |  |  |  |

|                       | The instruction bit L is defined in Table 2-7.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Rb                    | R0 - R31, General Purpose Register, source operand b                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                       | <ul> <li>With 32-bit MicroBlaze represents the entire 32-bit register</li> <li>With 64-bit MicroBlaze and L = 0, represents the 32 least significant bits</li> <li>With 64-bit MicroBlaze and L = 1, represents the entire 64-bit register</li> </ul>                                      |  |  |  |  |  |  |

|                       | The instruction bit L is defined in Table 2-7.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Rd                    | R0 - R31, General Purpose Register, destination operand                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                       | <ul> <li>With 32-bit MicroBlaze the entire 32-bit register is assigned the result</li> <li>With 64-bit MicroBlaze and L = 0, the 32 least significant bits are assigned the result</li> <li>With 64-bit MicroBlaze and L = 1, the entire 64-bit register is assigned the result</li> </ul> |  |  |  |  |  |  |

|                       | The instruction bit L is defined in Table 2-7.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| SPR[x]                | Special Purpose Register number x                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| MSR                   | Machine Status Register = SPR[1]                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| ESR                   | Exception Status Register = SPR[5]                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| EAR                   | Exception Address Register = SPR[3]                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| FSR                   | Floating-point Unit Status Register = SPR[7]                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| PVR <i>x</i>          | Processor Version Register, where x is the register number = $SPR[8192 + x]$                                                                                                                                                                                                               |  |  |  |  |  |  |

| BTR                   | Branch Target Register = SPR[11]                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| PC                    | Execute stage Program Counter = SPR[0]                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| <i>x</i> [ <i>y</i> ] | Bit y of register x                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

Table 2-6: Instruction Set Nomenclature

| Symbol               | Description                                                                                                                                  |  |  |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| x[y:z]               | Bit range y to z of register x                                                                                                               |  |  |  |  |  |  |

| х                    | Bit inverted value of register x                                                                                                             |  |  |  |  |  |  |

| lmm                  | 16 bit immediate value                                                                                                                       |  |  |  |  |  |  |

| lmm <i>x</i>         | x bit immediate value                                                                                                                        |  |  |  |  |  |  |

| FSLx                 | 4 bit AXI4-Stream port designator, where <i>x</i> is the port number                                                                         |  |  |  |  |  |  |

| C                    | Carry flag, MSR[29]                                                                                                                          |  |  |  |  |  |  |

| Sa                   | Special Purpose Register, source operand                                                                                                     |  |  |  |  |  |  |

| Sd                   | Special Purpose Register, destination operand                                                                                                |  |  |  |  |  |  |

| s( <i>x</i> )        | Sign extend argument <i>x</i> to 32-bit or 64-bit value                                                                                      |  |  |  |  |  |  |

| *Addr                | Memory contents at location Addr (data-size aligned)                                                                                         |  |  |  |  |  |  |

| :=                   | Assignment operator                                                                                                                          |  |  |  |  |  |  |

| =                    | Equality comparison                                                                                                                          |  |  |  |  |  |  |

| !=                   | Inequality comparison                                                                                                                        |  |  |  |  |  |  |

| >                    | Greater than comparison                                                                                                                      |  |  |  |  |  |  |

| >=                   | Greater than or equal comparison                                                                                                             |  |  |  |  |  |  |

| <                    | Less than comparison                                                                                                                         |  |  |  |  |  |  |

| <=                   | Less than or equal comparison                                                                                                                |  |  |  |  |  |  |

| +                    | Arithmetic add                                                                                                                               |  |  |  |  |  |  |

| *                    | Arithmetic multiply                                                                                                                          |  |  |  |  |  |  |

| /                    | Arithmetic divide                                                                                                                            |  |  |  |  |  |  |

| >> x                 | Bit shift right <i>x</i> bits                                                                                                                |  |  |  |  |  |  |

| << <i>x</i>          | Bit shift left x bits                                                                                                                        |  |  |  |  |  |  |

| and                  | Logic AND                                                                                                                                    |  |  |  |  |  |  |

| or                   | Logic OR                                                                                                                                     |  |  |  |  |  |  |

| xor                  | Logic exclusive OR                                                                                                                           |  |  |  |  |  |  |

| op1 if cond else op2 | Perform op1 if condition cond is true, else perform op2                                                                                      |  |  |  |  |  |  |

| &                    | Concatenate. For example "0000100 & Imm7" is the concatenation of the fixed field "0000100" and a 7 bit immediate value.                     |  |  |  |  |  |  |

| signed               | Operation performed on signed integer data type. All arithmetic operations are performed on signed word operands, unless otherwise specified |  |  |  |  |  |  |

| unsigned             | Operation performed on unsigned integer data type                                                                                            |  |  |  |  |  |  |

| float                | Operation performed on floating-point data type                                                                                              |  |  |  |  |  |  |

| clz(r)               | Count leading zeros                                                                                                                          |  |  |  |  |  |  |

#### Table 2-6: Instruction Set Nomenclature (Cont'd)

#### Table 2-7: MicroBlaze Instruction Set Summary

| Туре А            | 0-5    | 6-10 | 11-15 | 16-20         | 21-31       | Comontino                                                                                |

|-------------------|--------|------|-------|---------------|-------------|------------------------------------------------------------------------------------------|

| Туре В            | 0-5    | 6-10 | 11-15 |               | 16-31       | Semantics                                                                                |

| ADD Rd,Ra,Rb      | 000000 | Rd   | Ra    | Rb            | 00L00000000 | Rd := Rb + Ra                                                                            |

| RSUB Rd,Ra,Rb     | 000001 | Rd   | Ra    | Rb            | 00L00000000 | $Rd := Rb + \overline{Ra} + 1$                                                           |

| ADDC Rd,Ra,Rb     | 000010 | Rd   | Ra    | Rb            | 00L00000000 | Rd := Rb + Ra + C                                                                        |

| RSUBC Rd,Ra,Rb    | 000011 | Rd   | Ra    | Rb            | 00L00000000 | $Rd := Rb + \overline{Ra} + C$                                                           |

| ADDK Rd,Ra,Rb     | 000100 | Rd   | Ra    | Rb            | 00L00000000 | Rd := Rb + Ra                                                                            |

| RSUBK Rd,Ra,Rb    | 000101 | Rd   | Ra    | Rb            | 00L00000000 | $Rd := Rb + \overline{Ra} + 1$                                                           |

| CMP Rd,Ra,Rb      | 000101 | Rd   | Ra    | Rb            | 00L00000001 | Rd := Rb + Ra + 1<br>Rd[0] := 0 if (Rb >= Ra) else<br>Rd[0] := 1                         |

| CMPU Rd,Ra,Rb     | 000101 | Rd   | Ra    | Rb            | 00L00000011 | Rd := Rb + Ra + 1 (unsigned)<br>Rd[0] := 0 if (Rb >= Ra, unsigned)<br>else<br>Rd[0] := 1 |

| ADDKC Rd,Ra,Rb    | 000110 | Rd   | Ra    | Rb            | 00L00000000 | Rd := Rb + Ra + C                                                                        |

| RSUBKC Rd,Ra,Rb   | 000111 | Rd   | Ra    | Rb            | 00L00000000 | $Rd := Rb + \overline{Ra} + C$                                                           |

| ADDI Rd,Ra,Imm    | 001000 | Rd   | Ra    |               | Imm         | Rd := s(Imm) + Ra                                                                        |

| RSUBI Rd,Ra,Imm   | 001001 | Rd   | Ra    |               | Imm         | $Rd := s(Imm) + \overline{Ra} + 1$                                                       |

| ADDIC Rd,Ra,Imm   | 001010 | Rd   | Ra    |               | lmm         | Rd := s(Imm) + Ra + C                                                                    |

| RSUBIC Rd,Ra,Imm  | 001011 | Rd   | Ra    |               | Imm         | $Rd := s(Imm) + \overline{Ra} + C$                                                       |

| ADDIK Rd,Ra,Imm   | 001100 | Rd   | Ra    | Imm           |             | Rd := s(Imm) + Ra                                                                        |

| RSUBIK Rd,Ra,Imm  | 001101 | Rd   | Ra    | Imm           |             | $Rd := s(Imm) + \overline{Ra} + 1$                                                       |

| ADDIKC Rd,Ra,Imm  | 001110 | Rd   | Ra    |               | lmm         | Rd := s(Imm) + Ra + C                                                                    |

| RSUBIKC Rd,Ra,Imm | 001111 | Rd   | Ra    |               | Imm         | $Rd := s(Imm) + \overline{Ra} + C$                                                       |

| MUL Rd,Ra,Rb      | 010000 | Rd   | Ra    | Rb            | 00000000000 | Rd := Ra * Rb                                                                            |

| MULH Rd,Ra,Rb     | 010000 | Rd   | Ra    | Rb            | 0000000001  | Rd := (Ra * Rb) >> 32 (signed)                                                           |

| MULHU Rd,Ra,Rb    | 010000 | Rd   | Ra    | Rb            | 0000000011  | Rd := (Ra * Rb) >> 32 (unsigned)                                                         |

| MULHSU Rd,Ra,Rb   | 010000 | Rd   | Ra    | Rb 0000000010 |             | Rd := (Ra, signed * Rb, unsigned) >><br>32 (signed)                                      |

| BSRL Rd,Ra,Rb     | 010001 | Rd   | Ra    | Rb            | 00L00000000 | Rd := 0 & (Ra >> Rb)                                                                     |

| BSRA Rd,Ra,Rb     | 010001 | Rd   | Ra    | Rb 01L0000000 |             | Rd := s(Ra >> Rb)                                                                        |

| BSLL Rd,Ra,Rb     | 010001 | Rd   | Ra    | Rb 10L0000000 |             | Rd := (Ra << Rb) & 0                                                                     |

| IDIV Rd,Ra,Rb     | 010010 | Rd   | Ra    | Rb            | 00000000000 | Rd := Rb/Ra                                                                              |

Table 2-7: MicroBlaze Instruction Set Summary (Cont'd)

| Туре А                  | 0-5    | 6-10  | 11-15 | 16-20 | 21-31                    | Semantics                                                                                                         |

|-------------------------|--------|-------|-------|-------|--------------------------|-------------------------------------------------------------------------------------------------------------------|

| Туре В                  | 0-5    | 6-10  | 11-15 |       | 16-31                    | Semantics                                                                                                         |

| IDIVU Rd,Ra,Rb          | 010010 | Rd    | Ra    | Rb    | 0000000010               | Rd := Rb/Ra, unsigned                                                                                             |

| <i>TNEA</i> GETD Rd,Rb  | 010011 | Rd    | 00000 | Rb    | 0 <i>N0TAE</i><br>00000  | Rd := FSL Rb[28:31] (data read)<br>MSR[FSL] := 1 if (FSL_S_Control = 1)<br>MSR[C] := not FSL_S_Exists if N = 1    |

| TNAPUTD Ra,Rb           | 010011 | 00000 | Ra    | Rb    | 1 <i>N0TA</i> 0<br>00000 | FSL Rb[28:31] := Ra (data write)<br>MSR[C] := FSL_M_Full if N = 1                                                 |

| <i>TNE</i> CAGETD Rd,Rb | 010011 | Rd    | 00000 | Rb    | 0 <i>N1TAE</i><br>00000  | Rd := FSL Rb[28:31] (control read)<br>MSR[FSL] := 1 if (FSL_S_Control = 0)<br>MSR[C] := not FSL_S_Exists if N = 1 |

| TNCAPUTD Ra,Rb          | 010011 | 00000 | Ra    | Rb    | 1 <i>N1TA</i> 0<br>00000 | FSL Rb[28:31] := Ra (control write)<br>MSR[C] := FSL_M_Full if N = 1                                              |

| FADD Rd,Ra,Rb           | 010110 | Rd    | Ra    | Rb    | 00000000000              | Rd := Rb+Ra, float <sup>1</sup>                                                                                   |

| FRSUB Rd,Ra,Rb          | 010110 | Rd    | Ra    | Rb    | 00010000000              | Rd := Rb-Ra, float <sup>1</sup>                                                                                   |

| FMUL Rd,Ra,Rb           | 010110 | Rd    | Ra    | Rb    | 0010000000               | Rd := Rb*Ra, float <sup>1</sup>                                                                                   |

| FDIV Rd,Ra,Rb           | 010110 | Rd    | Ra    | Rb    | 00110000000              | Rd := Rb/Ra, float <sup>1</sup>                                                                                   |

| FCMP.UN Rd,Ra,Rb        | 010110 | Rd    | Ra    | Rb    | 01000000000              | Rd := 1 if (Rb = NaN or Ra = NaN,<br>float <sup>1</sup> ) else<br>Rd := 0                                         |

| FCMP.LT Rd,Ra,Rb        | 010110 | Rd    | Ra    | Rb    | 01000010000              | Rd := 1 if (Rb < Ra, float <sup>1</sup> ) else<br>Rd := 0                                                         |

| FCMP.EQ Rd,Ra,Rb        | 010110 | Rd    | Ra    | Rb    | 01000100000              | $Rd := 1$ if $(Rb = Ra, float^1)$ else<br>Rd := 0                                                                 |

| FCMP.LE Rd,Ra,Rb        | 010110 | Rd    | Ra    | Rb    | 01000110000              | Rd := 1 if (Rb <= Ra, float <sup>1</sup> ) else<br>Rd := 0                                                        |

| FCMP.GT Rd,Ra,Rb        | 010110 | Rd    | Ra    | Rb    | 01001000000              | Rd := 1 if (Rb > Ra, float <sup>1</sup> ) else<br>Rd := 0                                                         |

| FCMP.NE Rd,Ra,Rb        | 010110 | Rd    | Ra    | Rb    | 01001010000              | Rd := 1 if (Rb != Ra, float <sup>1</sup> ) else<br>Rd := 0                                                        |

| FCMP.GE Rd,Ra,Rb        | 010110 | Rd    | Ra    | Rb    | 01001100000              | $Rd := 1$ if $(Rb \ge Ra, float^1)$ else<br>Rd := 0                                                               |

| FLT Rd,Ra               | 010110 | Rd    | Ra    | 0     | 01010000000              | Rd := float (Ra) <sup>1</sup>                                                                                     |

| FINT Rd,Ra              | 010110 | Rd    | Ra    | 0     | 01100000000              | Rd := int (Ra) <sup>1</sup>                                                                                       |

| FSQRT Rd,Ra             | 010110 | Rd    | Ra    | 0     | 01110000000              | Rd := sqrt (Ra) <sup>1</sup>                                                                                      |

#### Table 2-7: MicroBlaze Instruction Set Summary (Cont'd)

| Туре А                                 | 0-5    | 6-10 | 11-15 | 16-20            | 21-31                                          | Compating                                                               |

|----------------------------------------|--------|------|-------|------------------|------------------------------------------------|-------------------------------------------------------------------------|

| Туре В                                 | 0-5    | 6-10 | 11-15 |                  | 16-31                                          | Semantics                                                               |

| DADD Rd,Ra,Rb <sup>2</sup>             | 010110 | Rd   | Ra    | Rb               | 10000000000                                    | Rd := Rb+Ra, double <sup>1</sup>                                        |

| DRSUB Rd,Ra,Rb <sup>2</sup>            | 010110 | Rd   | Ra    | Rb               | 10010000000                                    | Rd := Rb-Ra, double <sup>1</sup>                                        |

| DMUL Rd,Ra,Rb <sup>2</sup>             | 010110 | Rd   | Ra    | Rb               | 10100000000                                    | Rd := Rb*Ra, double <sup>1</sup>                                        |

| DDIV Rd,Ra,Rb <sup>2</sup>             | 010110 | Rd   | Ra    | Rb               | 10110000000                                    | Rd := Rb/Ra, double <sup>1</sup>                                        |

| DCMP.UN Rd,Ra,Rb <sup>2</sup>          | 010110 | Rd   | Ra    | Rb               | 11000000000                                    | Rd := 1 if (Rb = NaN or Ra = NaN,<br>double <sup>1</sup> ) else Rd := 0 |

| DCMP.LT Rd,Ra,Rb <sup>2</sup>          | 010110 | Rd   | Ra    | Rb               | 11000010000                                    | Rd := 1 if (Rb < Ra, double <sup>1</sup> ) else<br>Rd := 0              |

| DCMP.EQ Rd,Ra,Rb <sup>2</sup>          | 010110 | Rd   | Ra    | Rb               | 11000100000                                    | Rd := 1 if (Rb = Ra, double <sup>1</sup> ) else<br>Rd := 0              |

| DCMP.LE Rd,Ra,Rb <sup>2</sup>          | 010110 | Rd   | Ra    | Rb               | 11000110000                                    | Rd := 1 if (Rb <= Ra, double <sup>1</sup> ) else<br>Rd := 0             |

| DCMP.GT Rd,Ra,Rb <sup>2</sup>          | 010110 | Rd   | Ra    | Rb               | 11001000000                                    | Rd := 1 if (Rb > Ra, double <sup>1</sup> ) else<br>Rd := 0              |

| DCMP.NE Rd,Ra,Rb <sup>2</sup>          | 010110 | Rd   | Ra    | Rb               | 11001010000                                    | Rd := 1 if (Rb != Ra, double <sup>1</sup> ) else<br>Rd := 0             |

| DCMP.GE Rd,Ra,Rb <sup>2</sup>          | 010110 | Rd   | Ra    | Rb               | 11001100000                                    | Rd := 1 if (Rb >= Ra, double <sup>1</sup> ) else<br>Rd := 0             |

| DBL Rd,Ra <sup>2</sup>                 | 010110 | Rd   | Ra    | 0                | 11010000000                                    | Rd := double (Ra) <sup>1</sup>                                          |

| DLONG Rd,Ra <sup>2</sup>               | 010110 | Rd   | Ra    | 0                | 11100000000                                    | Rd := long (Ra) <sup>1</sup>                                            |

| DSQRT Rd,Ra <sup>2</sup>               | 010110 | Rd   | Ra    | 0                | 11110000000                                    | Rd := dsqrt (Ra) <sup>1</sup>                                           |

| MULI Rd,Ra,Imm                         | 011000 | Rd   | Ra    |                  | Imm                                            | Rd := Ra * s(Imm)                                                       |

| BSRLI Rd,Ra,Imm                        | 011001 | Rd   | Ra    | 00L0             | 00000000 &<br>Imm5                             | Rd : = 0 & (Ra >> Imm5)                                                 |

| BSRAI Rd,Ra,Imm                        | 011001 | Rd   | Ra    | 00L0             | 00010000 &<br>Imm5                             | Rd := s(Ra >> Imm5)                                                     |

| BSLLI Rd,Ra,Imm                        | 011001 | Rd   | Ra    | 0010             | 00100000 &<br>Imm5                             | Rd := (Ra << Imm5) & 0                                                  |

| BSEFI Rd,Ra,                           | 011001 | Rd   | Ra    |                  | 01L00 &                                        | Rd[0:31-Imm <sub>W</sub> ] := 0                                         |

| Imm <sub>W</sub> ,Imm <sub>S</sub>     |        |      |       | Imm <sub>W</sub> | v & 0 & Imm <sub>S</sub>                       | $Rd[32-Imm_W:31] := (Ra >> Imm_S)$                                      |

| BSIFI Rd,Ra,<br>Width,Imm <sub>S</sub> | 011001 | Rd   | Ra    |                  | 10L00 &<br><sub>V</sub> & 0 & Imm <sub>S</sub> | eq:massessessessessessessessessessessessesse                            |

| Table 2-7: | MicroBlaze Instruction Set Summary (Cont' | d) |

|------------|-------------------------------------------|----|

|------------|-------------------------------------------|----|

| Туре А                       | 0-5    | 6-10  | 11-15 | 16-20         | 21-31                    | Semantics                                                                                                                                                                     |

|------------------------------|--------|-------|-------|---------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре В                       | 0-5    | 6-10  | 11-15 |               | 16-31                    | Semantics                                                                                                                                                                     |

| ADDLI Rd,Imm <sup>2</sup>    | 011010 | Rd    | 00000 |               | lmm                      | Rd[0:63] := s(Imm) + Rd[0:63]                                                                                                                                                 |

| RSUBLI Rd,Imm <sup>2</sup>   | 011010 | Rd    | 00001 |               | Imm                      | Rd[0:63] := s(Imm) + Rd[0:63]                                                                                                                                                 |

| ADDLIC Rd,Imm <sup>2</sup>   | 011010 | Rd    | 00010 |               | Imm                      | Rd[0:63] := s(Imm) + Rd[0:63] + C                                                                                                                                             |

| RSUBLIC Rd, Imm <sup>2</sup> | 011010 | Rd    | 00011 |               | Imm                      | Rd[0:63] := s(Imm) + Rd[0:63] + C                                                                                                                                             |

| ADDLIK Rd,Imm <sup>2</sup>   | 011010 | Rd    | 00100 |               | Imm                      | Rd[0:63] := s(Imm) + Rd[0:63]                                                                                                                                                 |

| RSUBLIK Rd, Imm <sup>2</sup> | 011010 | Rd    | 00101 |               | Imm                      | Rd[0:63] := s(Imm) + Rd[0:63]                                                                                                                                                 |

| ADDLIKC Rd,Imm <sup>2</sup>  | 011010 | Rd    | 00110 |               | Imm                      | Rd[0:63] := s(Imm) + Rd[0:63] + C                                                                                                                                             |

| RSUBLIKC Rd,Imm <sup>2</sup> | 011010 | Rd    | 00111 |               | Imm                      | Rd[0:63] := s(Imm) + Rd[0:63] + C                                                                                                                                             |

| ORLI Rd,Imm <sup>2</sup>     | 011010 | Rd    | 10000 |               | Imm                      | Rd[0:63] := s(Imm) or Rd[0:63]                                                                                                                                                |

| ANDLI Rd,Imm <sup>2</sup>    | 011010 | Rd    | 10001 |               | Imm                      | Rd[0:63] := s(Imm) and Rd[0:63]                                                                                                                                               |

| XORLI Rd,Imm <sup>2</sup>    | 011010 | Rd    | 10010 |               | lmm                      | Rd[0:63] := s(Imm) xor Rd[0:63]                                                                                                                                               |

| ANDNLI Rd,Imm <sup>2</sup>   | 011010 | Rd    | 10011 |               | lmm                      | Rd[0:63] := s(Imm) and Rd[0:63]                                                                                                                                               |

| TNEAGET Rd,FSLx              | 011011 | Rd    | 00000 | 0N07          | <i>FAE</i> 000000 & FSLx | Rd := FSLx (data read, blocking if $N = 0$ )                                                                                                                                  |

|                              |        |       |       |               |                          | $MSR[FSL] := 1 \text{ if } (FSLx_S\_Control = 1)$<br>$MSR[C] := not FSLx\_S\_Exists \text{ if } N = 1$                                                                        |

| TNAPUT Ra,FSLx               | 011011 | 00000 | Ra    | 1 <i>N</i> 07 | A0000000 &<br>FSLx       | FSLx := Ra (data write, block if N = 0)<br>MSR[C] := FSLx_M_Full if N = 1                                                                                                     |

| TNECAGET Rd,FSLx             | 011011 | Rd    | 00000 | 0N17          | <i>FAE</i> 000000 & FSLx | Rd := FSLx (control read, block if $N = 0$ )                                                                                                                                  |

|                              |        |       |       |               |                          | MSR[FSL] := 1 if (FSLx_S_Control = 0)<br>MSR[C] := not FSLx_S_Exists if N = 1                                                                                                 |

| TNCAPUT Ra,FSLx              | 011011 | 00000 | Ra    | 1 <i>N</i> 17 | ۲A0000000 &<br>FSLx      | FSLx := Ra (control write, block if $N = 0$ )                                                                                                                                 |

|                              |        |       |       |               |                          | $MSR[C] := FSLx_M_Full if N = 1$                                                                                                                                              |

| OR Rd,Ra,Rb                  | 100000 | Rd    | Ra    | Rb            | 00000000000              | Rd := Ra or Rb                                                                                                                                                                |

| PCMPBF Rd,Ra,Rb              | 100000 | Rd    | Ra    | Rb            | 10000000000              | Rd := 1 if (Rb[0:7] = Ra[0:7]) else<br>Rd := 2 if (Rb[8:15] = Ra[8:15]) else<br>Rd := 3 if (Rb[16:23] = Ra[16:23]) else<br>Rd := 4 if (Rb[24:31] = Ra[24:31]) else<br>Rd := 0 |

| AND Rd,Ra,Rb                 | 100001 | Rd    | Ra    | Rb            | 00000000000              | Rd := Ra and Rb                                                                                                                                                               |

| XOR Rd,Ra,Rb                 | 100010 | Rd    | Ra    | Rb            | 0000000000               | Rd := Ra xor Rb                                                                                                                                                               |

Table 2-7: MicroBlaze Instruction Set Summary (Cont'd)

| Туре А                     | 0-5    | 6-10  | 11-15 | 16-20 | 21-31            | Comonting                                                                                                                                                                                                                                       |

|----------------------------|--------|-------|-------|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре В                     | 0-5    | 6-10  | 11-15 |       | 16-31            | Semantics                                                                                                                                                                                                                                       |

| PCMPEQ Rd,Ra,Rb            | 100010 | Rd    | Ra    | Rb    | 10000000000      | Rd := 1 if (Rb = Ra) else<br>Rd := 0                                                                                                                                                                                                            |

| ANDN Rd,Ra,Rb              | 100011 | Rd    | Ra    | Rb    | 00000000000      | Rd := Ra and $\overline{Rb}$                                                                                                                                                                                                                    |

| PCMPNE Rd,Ra,Rb            | 100011 | Rd    | Ra    | Rb    | 10000000000      | Rd := 1 if (Rb != Ra) else<br>Rd := 0                                                                                                                                                                                                           |

| SRA Rd,Ra                  | 100100 | Rd    | Ra    | 00000 | 0000000000000001 | Rd := s(Ra >> 1)<br>C := Ra[31]                                                                                                                                                                                                                 |

| SRC Rd,Ra                  | 100100 | Rd    | Ra    | 00000 | 00000100001      | Rd := C & (Ra >> 1)<br>C := Ra[31]                                                                                                                                                                                                              |

| SRL Rd,Ra                  | 100100 | Rd    | Ra    | 00000 | 00001000001      | Rd := 0 & (Ra >> 1)<br>C := Ra[31]                                                                                                                                                                                                              |

| SEXT8 Rd,Ra                | 100100 | Rd    | Ra    | 00000 | 00001100000      | Rd := s(Ra[24:31])                                                                                                                                                                                                                              |

| SEXT16 Rd,Ra               | 100100 | Rd    | Ra    | 00000 | 00001100001      | Rd := s(Ra[16:31])                                                                                                                                                                                                                              |

| SEXTL32 Rd,Ra <sup>2</sup> | 100100 | Rd    | Ra    | 00000 | 00001100010      | Rd := s(Ra[32:63])                                                                                                                                                                                                                              |

| CLZ Rd, Ra                 | 100100 | Rd    | Ra    | 00000 | 00011100000      | Rd = clz(Ra)                                                                                                                                                                                                                                    |

| SWAPB Rd, Ra               | 100100 | Rd    | Ra    | 00000 | 00111100000      | Rd = (Ra)[24:31, 16:23, 8:15, 0:7]                                                                                                                                                                                                              |

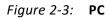

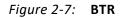

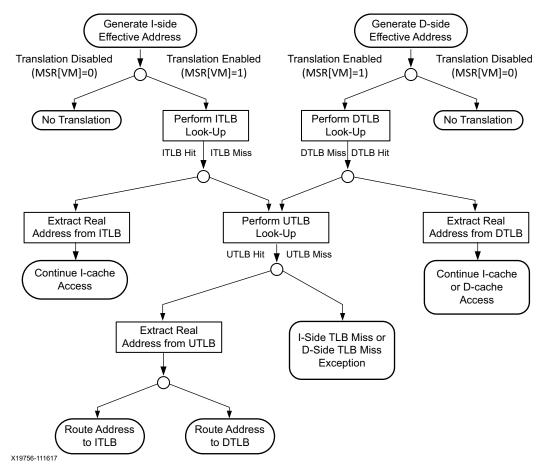

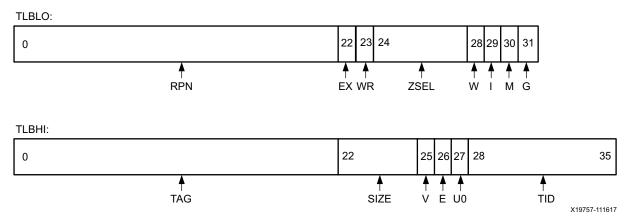

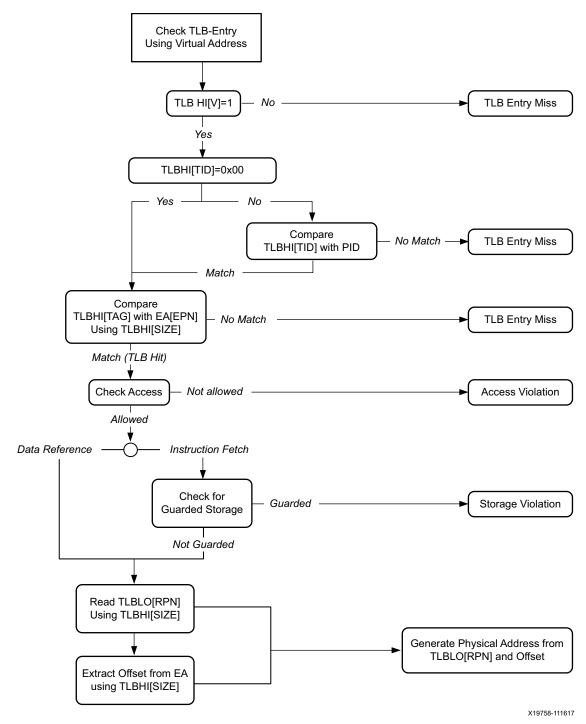

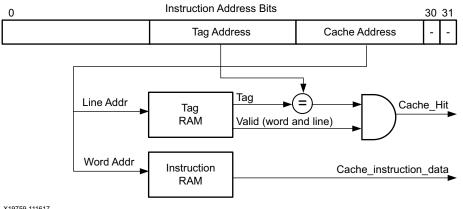

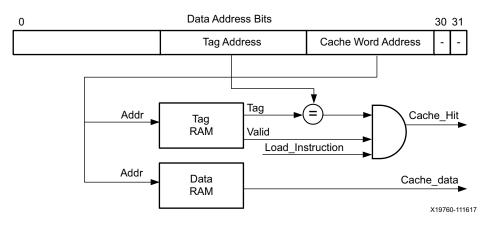

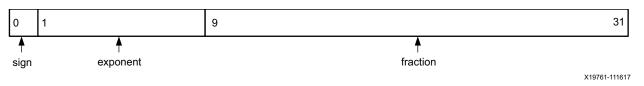

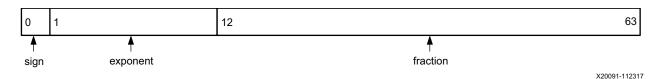

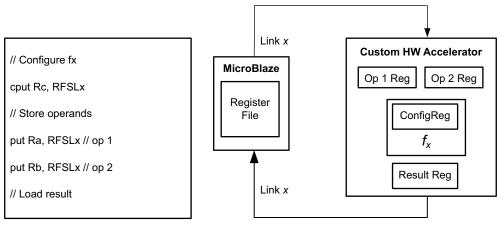

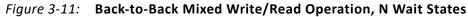

| SWAPH Rd, Ra               | 100100 | Rd    | Ra    | 00000 | 00111100010      | Rd = (Ra)[16:31, 0:15]                                                                                                                                                                                                                          |