# PRODUCT SELECTOR GUIDE

October 2024

# Lattice Semiconductor: The Low Power Programmable Leader

| CONTENTS                              |       |

|---------------------------------------|-------|

| FPGA Products                         | 4-6   |

| Video Connectivity                    | 7-8   |

| Control & Security                    | 9-11  |

| Ultra Low Power                       | 12    |

| Power and Thermal Management Products | 13    |

| FPGA and CPLD Design Software         | 14    |

| Solution Stacks                       | 15-22 |

| IP Cores and Reference Designs        | 23-27 |

| Development Kits                      | 28-39 |

| Programming Hardware                  | 40    |

# Lattice Semiconductor: The Low Power Programmable Leader

# **General Purpose FPGAs**

## Low Power FPGAs (CertusPro-NX, Certus-NX, ECP, and LatticeXP2 families)

Addresses a broad range of connectivity and acceleration applications across multiple markets.

- Lowest power and smallest package with up to 10G SERDES and 100K LCs

- Industry-leading reliability and efficient processing (with class-leading on-chip memory and LPDDR4 support)

# Specialized Families Tailored For Specific Needs

## Video Connectivity FPGAs (CrossLink Families)

Optimized for high speed video and sensor applications

- First FPGA with hardened MIPI D-PHY

- Highest performance at lowest power

## Ultra Low Power FPGAs (iCE40 Families)

World's lowest power FPGAs; Optimized for small form factor

- Static current as low as 25 uA

- World's most popular ultra low power FPGA

## Control & Security FPGAs (Mach & L-ASC10 Families)

Optimized for platform management & security applications

- Instant-on, non-volatile

- Highest I/O density

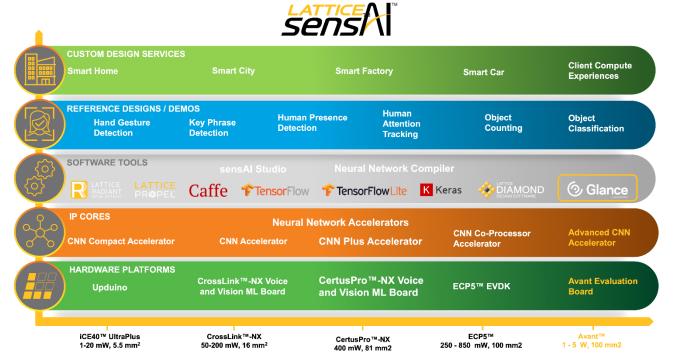

# Lattice sensAI<sup>™</sup> Solution Stack

## Accelerate Integration of Flexible, Ultra Low Power Inferencing

With solutions optimized for ultra low power consumption (under 1 mW – 1 W), small package size (5.5 mm2 – 100 mm2), customizable performance and accuracy, and interface flexibility (MIPI CSI-2, LVDS, GigE, etc.), the Lattice sensAI stack accelerates integration of scalable, always-on, on-device AI.

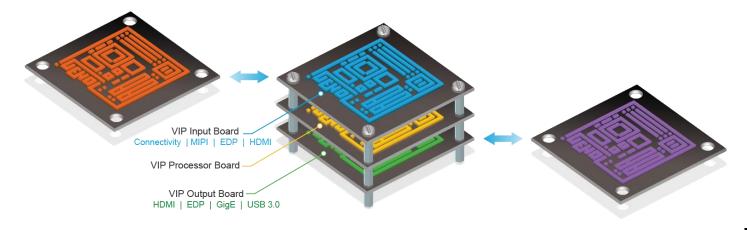

# Lattice mVision<sup>™</sup> Solution Stack

## Accelerate Implementation of Low Power Embedded Vision Applications

With solutions optimized for low power consumption ranging from under 150 mW to 1 W and small package size (2.5 x 2.5 mm to 10 x 10 mm) the Lattice mVision solution stack provides customizable performance and flexible interface connectivity (MIPI CSI-2, LVDS, PCIe, GigE, etc.). Lattice's mVision solution stack accelerates the integration of scalable Embedded Vision solutions for Smart Factory, Machine Vision, Smart City, and Smart Home applications.

# Lattice Sentry<sup>™</sup> Solution Stack

## Software Solution for Platform Firmware Resiliency (PFR) Root of Trust

The Lattice Sentry solution stack consists of a complete reference platform, fully validated IP building blocks, easy to use FPGA design tools, reference design/demonstrations, as well as a network of custom design services. In many instances, a fully functioning PFR solution can be developed by modifying the included RISC-V C source code.

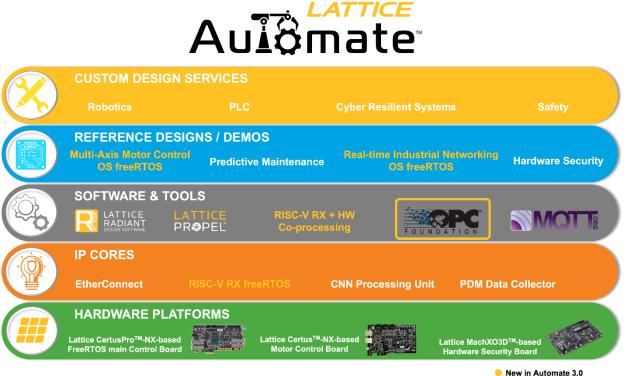

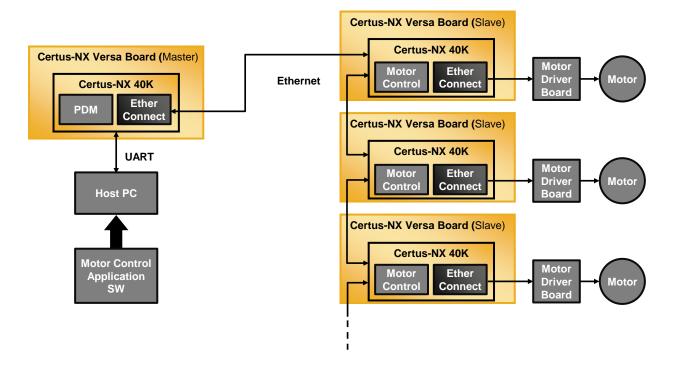

# Lattice Automate<sup>™</sup> Solution Stack

Lattice Automate helps designers accelerate high performance, low power, secure solutions for next generation factory automation solutions. The stack includes modular hardware development boards and software-programmable reference designs and demos that simplify and accelerate implementation of applications like robotics, scalable multi-channel motor control with predictive maintenance, and real-time industrial networking.

# Lattice SupplyGuard™

## End-to-End Supply Chain Protection Service

The Lattice SupplyGuard<sup>™</sup> service provides customers with factory-locked ICs. These ICs can only be programmed using a configuration bitstream which has been developed, signed and encrypted by the intended customer. The solution is designed to provide protection against counterfeiting, over-building, malware insertion and IP theft.

# For more information go to LATTICESEMI.COM

## **General Purpose FPGAs**

| Fe                  | atures                                         |                  | Avant-AT-E                              |                  |                      | Avant-AT-G                                                       |                      |                      | Avant-AT-X                                                      |                     |  |

|---------------------|------------------------------------------------|------------------|-----------------------------------------|------------------|----------------------|------------------------------------------------------------------|----------------------|----------------------|-----------------------------------------------------------------|---------------------|--|

| D                   | evice                                          | E30              | E50                                     | E70              | G30                  | G50                                                              | G70                  | X30                  | X50                                                             | X70                 |  |

| System Logic Cells  | (k)                                            | 262              | 409                                     | 637              | 262                  | 409                                                              | 637                  | 262                  | 409                                                             | 637                 |  |

| Look-Up-Tables (k l | LUTs)                                          | 163              | 255                                     | 397              | 163                  | 255                                                              | 397                  | 163                  | 255                                                             | 397                 |  |

|                     | Blocks                                         | 400              | 630                                     | 990              | 400                  | 630                                                              | 990                  | 400                  | 630                                                             | 990                 |  |

| EBR SRAM            | Mbits                                          | 14.4             | 22.7                                    | 35.6             | 14.4                 | 22.7                                                             | 35.6                 | 14.4                 | 22.7                                                            | 35.6                |  |

| Distributed RAM     | kbits                                          | 1700             | 2660                                    | 4140             | 1700                 | 2660                                                             | 4140                 | 1700                 | 2660                                                            | 4140                |  |

| DSP Blocks          | 18 x 18 Multipliers                            | 700              | 1120                                    | 1800             | 700                  | 1120                                                             | 1800                 | 700                  | 1120                                                            | 1800                |  |

| Dol Diocks          | 8 x 8 <sup>1</sup> Multipliers                 | 2800             | 4480                                    | 7200             | 2800                 | 4480                                                             | 7200                 | 2800                 | 4480                                                            | 7200                |  |

| High Frequency Os   | cillator                                       |                  | 1                                       |                  |                      | 1                                                                |                      |                      | 1                                                               |                     |  |

| GPLL                |                                                | 7                | 9                                       | 11               | 7                    | 9                                                                | 11                   | 7 9 11               |                                                                 |                     |  |

| External Memory In  | terface                                        | L                | PDDR4 / DDF                             | R4               | L                    | PDDR4 / DDF                                                      | 84                   | LPDD                 | 0R4 / DDR4 / I                                                  | DDR5                |  |

| SerDes Maximum S    | peed (Gbps)                                    |                  |                                         |                  |                      | 12.5                                                             |                      |                      | 25                                                              |                     |  |

| SerDes Protocols    |                                                |                  |                                         |                  | PCle                 | Gen 1 / 2 / 3,                                                   | 10GE                 | PCle G               | ien 1 / 2 / 3 / 4                                               | l, 25GE             |  |

| Security            |                                                |                  |                                         |                  |                      | eam Encryptic<br>Authenticatior                                  |                      | Avant-G f            | eatures + Use                                                   | er Security         |  |

| Temperature         |                                                |                  | C,I                                     |                  | C,I                  |                                                                  |                      |                      | C,I                                                             |                     |  |

|                     | Package type, #Balls,<br>Size)                 | Total I/C        | D <sup>2</sup> (Wide Ran<br>Performance | ge, High<br>)    | Total I/C<br>Perfo   | D <sup>2</sup> (Wide Ran<br>ormance) / Se                        | ge, High<br>erDes    |                      | D <sup>2</sup> (Wide Rang<br>ormance) / Se                      |                     |  |

| ASG (FOWLP) 41      | 0 11 x 9 mm                                    | 247 (94,<br>153) |                                         |                  | 196 (43,<br>153) / 4 |                                                                  |                      | 196 (43,<br>153) / 4 |                                                                 |                     |  |

| CSG (FCCSP) 48      | 4 12 x 12 mm                                   |                  |                                         |                  |                      | 218 (43,<br>175) / 8                                             |                      |                      | 218 (43,<br>175) / 8                                            |                     |  |

| CSG (FCCSP) 84      | 1 15 x 13 mm                                   |                  |                                         | 520 (94,<br>408) |                      |                                                                  | 303 (43,<br>260) / 8 |                      |                                                                 | 303 (43<br>260) / 8 |  |

|                     | Package type, #Balls,<br>Size)                 | Total I/C        | D <sup>2</sup> (Wide Ran<br>Performance | ge, High<br>)    | Total I/0<br>Perfo   | D <sup>2</sup> (Wide Ran<br>ormance) / Se                        | ge, High<br>erDes    | Total I/C<br>Perfo   | D <sup>2</sup> (Wide Rangormance) / Se                          | ge, High<br>erDes   |  |

| CBG (FCCSP) 48      | 4 19 x 19 mm                                   | 329 (94,<br>235) | 329 (94,<br>235)                        | 349 (94,<br>255) |                      |                                                                  |                      |                      |                                                                 |                     |  |

|                     | G (FCBGA) 484 19 x 19 mm                       |                  |                                         |                  | 218 (43,             | 218 (43,                                                         |                      | 218 (43,<br>175) / 8 | 218 (43,                                                        |                     |  |

| BG (FCBGA) 48       | 4 19 x 19 mm                                   |                  |                                         |                  | 175) / 8             | 175) / 8                                                         |                      | 110,10               | 175) / 8                                                        |                     |  |

| 1.0 mm Spacing (    | 4 19 x 19 mm<br>Package type, #Balls,<br>Size) |                  | D <sup>2</sup> (Wide Ran<br>Performance |                  | Total I/C            | <sup>175) / 8</sup><br>D <sup>2</sup> (Wide Ran<br>ormance) / Se |                      | Total I/C            | <sup>175)78</sup><br>D <sup>2</sup> (Wide Rang<br>ormance) / Se |                     |  |

| 1.0 mm Spacing (    | Package type, #Balls,<br>Size)                 |                  |                                         |                  | Total I/C            | D <sup>2</sup> (Wide Ran                                         |                      | Total I/C            | D <sup>2</sup> (Wide Ran                                        |                     |  |

1) One 18 x 18 multiplier fractures into four 8 x 8 multipliers 2) WRIO (3.3V. 2.5V, 1.8V, 1.2V) and HPIO (1.8V, 1.2V, 1.1V, 1.0V, 0.9V) single ended I/O standard support

## **General Purpose FPGAs**

| Fea                          | tures      |                  |                     | Certus                          | s™-NX                                |                      | CertusF                             | Pro™-NX                                         |  |

|------------------------------|------------|------------------|---------------------|---------------------------------|--------------------------------------|----------------------|-------------------------------------|-------------------------------------------------|--|

| De                           | evice      |                  | LFD2NX-9            | LFD2NX-17                       | LFD2NX-28                            | LFD2NX-40            | LFCPNX-50                           | LFCPNX-100                                      |  |

| Logic Cells <sup>1</sup> (k) |            |                  | 9                   | 17                              | 28                                   | 39                   | 52                                  | 96                                              |  |

|                              | Blocks     | S                | 15                  | 24                              | 58                                   | 84                   | 96                                  | 208                                             |  |

| EBR SRAM                     | kbits      |                  | 270                 | 432                             | 1054                                 | 1512                 | 1728                                | 3744                                            |  |

| Distributed RAM              | kbits      |                  | 80                  | 80                              | 240                                  | 240                  | 344                                 | 639                                             |  |

|                              | Blocks     | S                | 3                   | 5                               | 2                                    | 2                    | 4                                   | 7                                               |  |

| Large RAM (LRAM)             | kbits      |                  | 1536                | 2560                            | 1024                                 | 1024                 | 2048                                | 3584                                            |  |

| DSP Blocks                   | 18 x 1     | 8 Multipliers    | 12                  | 24                              | 40                                   | 56                   | 96                                  | 156                                             |  |

| PCIe Hard IP                 |            |                  |                     |                                 | 1 (Gen2, 5 Gbps)                     | 1 (Gen2, 5 Gbps)     | 1 (Gen3, 8 Gbps)                    | 1 (Gen3, 8 Gbps)                                |  |

| PCIe Lanes                   |            |                  |                     |                                 | 1                                    | 1                    | 4                                   | 4                                               |  |

| SERDES maximum               | speed      | Gbps             |                     |                                 | 5                                    | 5                    | 10 <sup>5</sup>                     | 10 <sup>5</sup>                                 |  |

| SGMII (1.25 Gbps)            | Lanes      |                  | 2                   | 2                               | 2                                    | 2                    | 2                                   | 2                                               |  |

| GPLL                         |            |                  | 2                   | 2                               | 3                                    | 3                    | 3                                   | 4                                               |  |

| ADC Blocks                   |            |                  | 2                   | 2                               | 2                                    | 2                    | 2                                   | 2                                               |  |

| 450 MHz High Freq            | uency Os   | cillator         | 1                   | 1                               | 1                                    | 1                    | 1                                   | 1                                               |  |

| 128 KHz Low Powe             | r Oscillat | or               | 1                   | 1                               | 1                                    | 1                    | 1 1                                 |                                                 |  |

| DDR Memory Supp              | ort (Up to | o 1066 Mbps)     |                     | LPDDR2,                         | DDR3/3L                              |                      | LPDDR4, LPDDR2, DDR3/3L             |                                                 |  |

| Boot Flash                   |            |                  |                     | Exte                            |                                      | External             |                                     |                                                 |  |

| Dual Boot                    |            |                  |                     | ~                               |                                      | √                    |                                     |                                                 |  |

| Multiple Boot                |            |                  |                     | ~                               | $\checkmark$                         |                      |                                     |                                                 |  |

| Bitstream Encrypti           | on (AES-2  | 256)             |                     | ~                               | v                                    | /                    |                                     |                                                 |  |

| Bitstream Authentic          | cation (EC | CDSA)            |                     | ~                               | $\checkmark$                         |                      |                                     |                                                 |  |

| Full-chip Configura          | tion Time  | e² (ms)          | 8                   | 8                               | 14                                   | 14                   | 29                                  | 29                                              |  |

| I/O Configuration T          | ime² (ms)  |                  | 3                   | 3                               | 3                                    | 3                    | 4                                   | 4                                               |  |

| Core Vcc                     |            |                  |                     | 1.0                             | ) V                                  |                      | 1.0                                 | 0 V                                             |  |

| Temperature                  |            |                  |                     | C, I                            | I, A                                 |                      |                                     | I, A                                            |  |

| 0.5 mm Spacing (Pa           | ackage typ | e, #Balls, Size) | Tota                | I/O (Wide Range, High P         | Performance, ADC <sup>3</sup> ) / PC | le Lane              |                                     | e, High Performance,<br>RDES Lanes              |  |

| csfBGA                       | 121        | 6 x 6 mm         | 77 (23, 48, 6) / 04 | 77 (23, 48, 6) / 04             | 81 (23, 58, 0) / 14                  | 81 (23, 58, 0) / 14  |                                     |                                                 |  |

| ASG256                       | 256        | 9 x 9 mm         |                     | · ·                             |                                      |                      | 165 (75, 84, 6) / 4 <sup>4</sup>    | 165 (75, 84, 6) / 44                            |  |

| 0.8 mm Spacing (Pa           | ackage tvp | e. #Balls. Size) | Tota                | I/O (Wide Range, High P         | Performance ADC <sup>3</sup> ) / PC  | ie Lane              |                                     | e, High Performance,                            |  |

|                              |            | 12 x 12 mm       | 77 (23, 48, 6) / 04 | 77 (23, 48, 6) / 0 <sup>4</sup> | 156 (92, 58, 6) / 0 <sup>4</sup>     | 156 (92, 58, 6) / 04 | ADC <sup>3</sup> )/SE               | RDES Lanes                                      |  |

| caBGA                        |            | 14 x 14 mm       | 11 (23, 40, 0) / 0' | 11 (23, 40, 0) / 0              | 191 (111, 74, 6) / 1 <sup>4</sup>    |                      |                                     |                                                 |  |

| CBG256                       |            | 14 x 14 mm       |                     |                                 | 131 (111, 74, 0)/ 1                  | 131 (111, 74, 0)/ 1  | 165 (75, 84, 6) / 4 <sup>4</sup>    | 165 (75, 84, 6) / 4 <sup>4</sup>                |  |

| BBG484                       |            | 19 x 19 mm       |                     |                                 |                                      |                      | 269 (167, 96, 6) / 4 <sup>4,6</sup> |                                                 |  |

|                              |            |                  |                     |                                 |                                      |                      | · · · · · ·                         | 305 (167, 132, 6) / 84<br>je, High Performance, |  |

| 1.0 mm Spacing (Paci         | kage type, | #Balls, Size)    | Tota                | I/O (Wide Range, High P         | erformance, ADC <sup>3</sup> ) / PC  | le Lane              |                                     | RDES Lanes                                      |  |

| BFG484                       | 484        | 23 x 23 mm       |                     |                                 |                                      |                      | 269 (167, 96, 6) / 47               | 305 (167, 132, 6) / 47                          |  |

| LFG672                       | 672        | 27 x 27 mm       |                     |                                 |                                      |                      |                                     | 305 (167, 132, 6) / 8                           |  |

Logic Cells = LUTs x 1.2 effectiveness

QSPI mode at 150 MHz nominal frequency

Each ADC pin count reflects using dedicated complement pair and vRef

Commercial, Industrial, Automotive (AEC-Q100)

8 Gbps for Automotive Grade

SERDES speed up to 6.25 Gbps

7) SERDES speed up to 5.5 Gbps

# **FPGA Products**

## **General Purpose FPGAs**

|                   | Featu  | res          | EC          | CP5TM-                      | 5G          | ECP       | 5 Auton                    | notive   |              |           |           | ECP5™        | И        |          |          |              | Latti     | ceECP3       | гм        |            |

|-------------------|--------|--------------|-------------|-----------------------------|-------------|-----------|----------------------------|----------|--------------|-----------|-----------|--------------|----------|----------|----------|--------------|-----------|--------------|-----------|------------|

|                   | Devi   | ce           | LFE5UM5G-25 | LFE5UM5G-45                 | LFE5UM5G-85 | LAE5UM-25 | LAE5UM-45                  | LAE5U-12 | LFE5UM-25    | LFE5UM-45 | LFE5UM-85 | LFE5U-12     | LFE5U-25 | LFE5U-45 | LFE5U-85 | LFE3-17EA    | LFE3-35EA | LFE3-70EA    | LFE3-95EA | LFE3-150EA |

|                   | LUT    | s            | 24 k        | 44 k                        | 84 k        | 24 k      | 44 k                       | 12 k     | 24 k         | 44 k      | 84 k      | 12 k         | 24 k     | 44 k     | 84 k     | 17 k         | 33 k      | 67 k         | 92 k      | 149 k      |

|                   |        | # of Blocks  | 56          | 108                         | 208         | 56        | 108                        | 32       | 56           | 108       | 208       | 32           | 56       | 108      | 208      | 38           | 72        | 240          | 240       | 372        |

| EBR SRAN          | //     | kbits        | 1008        | 1944                        | 3744        | 1008      | 1944                       | 576      | 1008         | 1944      | 3744      | 576          | 1008     | 1944     | 3744     | 700          | 1,327     | 4,420        | 4,420     | 6,850      |

| Distrib RA        | М      | kbits        | 194         | 351                         | 669         | 194       | 351                        | 97       | 194          | 351       | 669       | 97           | 194      | 351      | 669      | 36           | 68        | 145          | 188       | 303        |

| sysDSP™<br>Blocks |        | Multipliers  | 28          | 72                          | 156         | 28        | 72                         | 28       | 28           | 72        | 156       | 28           | 28       | 72       | 156      | 24           | 64        | 128          | 128       | 320        |

| SERDES            |        | Max. Chan.   | 1/2         | 2                           |             | 1/2       | 2/4                        | 0        | 1/2          | 2         |           | 0            |          | 0        |          |              | 4         |              | 2         | 16         |

|                   |        | Max. Rate    |             | 5 Gbps                      |             |           | 3.2 Gbp                    |          |              |           |           | 3.2 Gbps     |          |          |          |              |           | 3.2 Gbps     |           |            |

| PLL + DLL         |        |              | 2+2         |                             | +4          | 2+2       | 4+4                        | 2+2      | 2+2          | 4-        | ⊦4        | 2+2          | 2+2      | 4-       | +4       | 2+2          | 4+2       |              | 10+2      |            |

| DDR Suppo         | ort    |              | LP          | DR3 80<br>DDR3 8<br>DR3L 80 | 00,         | LP        | DR3 80<br>DDR3 8<br>DR3L 8 | 00,      |              | DDR3      | 300, LPI  | DDR3 8       | 00, DDF  | R3L 800  |          | DD           | R3 800,   | DDR2 53      | 33, DDR   | 400        |

| Boot Flash        | ı      |              | E           | xternal                     |             | E         | xternal                    |          |              |           |           | Externa      | I        |          |          |              |           | External     | l         |            |

| Dual Boot         |        |              |             | $\checkmark$                |             |           | $\checkmark$               |          | $\checkmark$ |           |           |              |          | √        |          |              |           |              |           |            |

| Multiple Bo       | oot    |              |             | $\checkmark$                |             |           | $\checkmark$               |          | $\checkmark$ |           |           |              |          |          |          |              |           |              |           |            |

| Bit-stream        | Encryp | otion        |             | $\checkmark$                |             |           | $\checkmark$               |          | $\checkmark$ |           |           |              |          | √        |          |              |           |              |           |            |

| Core Vcc          |        |              |             | 1.2 V                       |             |           | 1.1 V                      |          | 1.1 V        |           |           |              |          |          |          | 1.2 V        |           |              |           |            |

|                   |        | С            |             | $\checkmark$                |             |           |                            |          | ✓            |           |           |              |          |          |          | $\checkmark$ |           |              |           |            |

| Temp.             |        | I            |             | $\checkmark$                |             |           |                            |          |              |           |           | $\checkmark$ |          |          |          |              |           | $\checkmark$ |           |            |

|                   |        | A (AEC-Q100) |             |                             |             |           | $\checkmark$               |          |              |           |           |              |          |          |          | \<br>\       | /         |              |           |            |

| 0.5 n             | nm Spa | acing        |             | Count<br>ERDES              | /           |           | Count .<br>ERDES           | /        |              |           |           |              | I/       | O Coun   | t / SER  | DES          |           |              |           |            |

| TQFP              | 144    | 20 x 20 mm   |             |                             |             |           |                            |          |              |           |           | 98/0         | 98/0     | 98/0     |          |              |           |              |           |            |

| csfBGA            | 285    | 10 x 10 mm   | 118/2       | 118/2                       | 118/2       |           |                            |          | 118/2        | 118/2     | 118/2     | 118/0        | 118/0    | 118/0    | 118/0    |              |           |              |           |            |

| csBGA             | 328    | 10 x 10 mm   |             |                             |             |           |                            |          |              |           |           |              |          |          |          | 116/2        |           |              |           |            |

| 0.8 n             | nm Spa | cing         |             | Count<br>ERDES              | /           |           | Count<br>ERDES             | /        |              |           |           |              | ١/       | O Coun   | t / SER  | DES          |           |              |           |            |

|                   | 256    | 14 x 14 mm   |             |                             |             |           |                            |          |              |           |           | 197/0        | 197/0    | 197/0    |          |              |           |              |           |            |

| -                 | 381    | 17 x 17 mm   | 197/2       | 203/4                       | 205/4       | 197/2     | 203/4                      | 197/0    | 197/2        | 203/4     | 205/4     | 197/0        | 197/0    | 203/0    | 205/0    |              |           |              |           |            |

| caBGA             | 554    | 23 x 23 mm   |             | 245/4                       | 259/4       |           |                            |          |              | 245/4     | 259/4     |              |          | 245/0    | 259/0    |              |           |              |           |            |

|                   | 756    | 27 x 27 mm   |             |                             | 365/4       |           |                            |          |              |           | 365/4     |              |          |          | 365/0    |              |           |              |           |            |

| 1.0 n             | nm Spa | acing        |             | Count<br>ERDES              | /           |           | Count<br>ERDES             | /        |              |           | _         |              | 1/       | O Coun   | t / SER  | DES          |           |              |           |            |

| ftBGA             | 256    | 17 x 17 mm   |             | -112-0                      |             | 3         | -112-0                     |          |              |           |           |              |          |          |          | 133/4        | 133/4     |              |           |            |

|                   | 484    | 23 x 23 mm   |             |                             |             |           |                            |          |              |           |           |              |          |          |          | 222/4        | 295/4     | 295/4        | 295/4     |            |

| -                 | 672    | 27 x 27 mm   |             |                             |             |           |                            |          |              |           |           |              |          |          |          |              | 310/4     | 380/8        | 380/8     | 380/8      |

| fpBGA             | 012    |              |             |                             |             |           |                            |          |              |           |           |              |          |          |          |              |           |              |           |            |

# Video Connectivity

## CrossLink Series – Embedded Vision FPGAs

| Features   |          |              |                   |                   |                  | Cros              | sLink™            |                  |                   |                   | CrossLir           | nkPlus™            |

|------------|----------|--------------|-------------------|-------------------|------------------|-------------------|-------------------|------------------|-------------------|-------------------|--------------------|--------------------|

| Device     |          |              | LIF-MD6000-6UWG36 | LIF-MD6000-6UMG64 | LIF-MD6000-6MG81 | LIF-MD6000-6JMG80 | LIF-MD6000-6KMG80 | LIA-MD6000-6MG81 | LIA-MD6000-6JMG80 | LIA-MD6000-6KMG80 | LIF-MDF6000-6UMG64 | LIF-MDF6000-6KMG80 |

| LCs (k)    |          |              |                   |                   |                  |                   | 7                 |                  | 1                 |                   | 7                  | 7                  |

|            |          | Blocks       |                   |                   |                  |                   | 20                |                  |                   |                   | 20                 | 20                 |

| EBR SRAI   | IVI      | kbits        |                   |                   |                  |                   | 180               |                  |                   |                   | 180                | 180                |

| Distribute | d RAM    | kbits        |                   |                   |                  |                   | 47                |                  |                   |                   | 47                 | 47                 |

|            |          | Port         | 1                 |                   |                  |                   | 2                 |                  |                   |                   | 2                  | 2                  |

| MIPI D-PH  | IY       | Lane         | 4                 | 4 8               |                  |                   |                   |                  |                   |                   |                    | 8                  |

|            |          | Max Rate     |                   | 1.5 Gbps          |                  |                   |                   |                  |                   |                   |                    | 1.5 Gbps           |

| GPLL       |          |              |                   |                   |                  |                   | 1                 |                  |                   |                   | 1                  | 1                  |

| Edge Cloc  | :k       |              | 2                 |                   |                  |                   | 4                 |                  |                   |                   | 4                  | 4                  |

| Boot Flas  | h        |              |                   |                   |                  | Ext               | ternal            |                  |                   |                   | Internal           | Internal           |

| Dual Boot  |          |              |                   |                   |                  | Ex                | ternal            |                  |                   |                   | External           | External           |

| Internal C | onfigura | tion Memory  |                   |                   |                  | N                 | VCM               |                  |                   |                   | Flash              | Flash              |

| Temp       |          | С            |                   |                   | $\checkmark$     |                   |                   |                  |                   |                   | √                  | √                  |

| remp       |          | 1            |                   |                   | $\checkmark$     |                   |                   |                  |                   |                   | $\checkmark$       | $\checkmark$       |

|            |          | A (AEC-Q100) |                   |                   |                  |                   |                   | $\checkmark$     | $\checkmark$      | $\checkmark$      |                    |                    |

|            | 0.4 mm F | Pitch        |                   |                   |                  | I/O (Low Spe      | ed/High Speed     | (b               |                   |                   | 1/0                | (L/H)              |

| WLCSP      | 36       | 2.5 x 2.5 mm | 17/10             |                   |                  |                   |                   |                  |                   |                   |                    |                    |

| ucfBGA     | 64       | 3.5 x 3.5 mm |                   | 29/22             |                  |                   |                   |                  |                   |                   | 29/22              |                    |

|            | 0.5 mm   |              |                   |                   |                  | I/O (Low Spe      | ed/High Speed     | ·                |                   |                   | I/O (              | (L/H)              |

| csfBGA     | 81       | 4.5 x 4.5 mm |                   |                   | 37/30            |                   |                   | 37/30            |                   |                   |                    |                    |

|            | 0.65 mm  |              |                   |                   |                  | I/O (Low Spe      | ed/High Speed     | (k               |                   |                   | I/O (              | (L/H)              |

| ctfBGA     | 80       | 6.5 x 6.5 mm |                   |                   |                  | 37/30             |                   |                  | 37/30             |                   |                    |                    |

| ckfBGA     | 80       | 7 x 7 mm     |                   |                   |                  |                   | 37/30             |                  |                   | 37/30             |                    | 37/30              |

# Video Connectivity

## **CrossLink Series – Embedded Vision FPGAs**

| Features        | 5           |              |                       | CrossLi                         | nk™-NX                                                  |                         |  |  |  |  |  |  |  |  |

|-----------------|-------------|--------------|-----------------------|---------------------------------|---------------------------------------------------------|-------------------------|--|--|--|--|--|--|--|--|

| Device          |             |              | LIFCL-17              | LIFCL-33                        | LIFCL-33U                                               | LIFCL-40                |  |  |  |  |  |  |  |  |

| LCs (k)         |             |              | 17                    | 33                              | 33                                                      | 39                      |  |  |  |  |  |  |  |  |

| EBR SRA         |             | Blocks       | 24                    | 64                              | 64                                                      | 84                      |  |  |  |  |  |  |  |  |

| EBR SRA         |             | kbits        | 432                   | 1152                            | 1152                                                    | 1512                    |  |  |  |  |  |  |  |  |

| Distribute      | ed RAM      | kbits        | 80                    | 220                             | 220                                                     | 240                     |  |  |  |  |  |  |  |  |

| Large<br>Memory |             | Blocks       | 5                     | 5                               | 5                                                       | 2                       |  |  |  |  |  |  |  |  |

| (LRAM)          |             | kbits        | 2560                  | 2560                            | 2560                                                    | 1024                    |  |  |  |  |  |  |  |  |

| sysDSP™         | M Blocks    | 18 x 18      | 24                    | 64                              | 64                                                      | 56                      |  |  |  |  |  |  |  |  |

|                 |             | Ports        | 2                     | -                               | -                                                       | 2                       |  |  |  |  |  |  |  |  |

| MIPI D-PH       | НҮ          | Lanes        | 8                     | -                               | -                                                       | 8                       |  |  |  |  |  |  |  |  |

| PCIe (5 G       | ibps)       | Lanes        | -                     | -                               |                                                         | 1                       |  |  |  |  |  |  |  |  |

| USB 2.0 /       | / USB 3.2 ( | 5 Gbps)      | -                     | -                               | 1/1                                                     | -                       |  |  |  |  |  |  |  |  |

| GPLL            |             |              | 2                     | 3                               |                                                         |                         |  |  |  |  |  |  |  |  |

| Boot Flas       | sh          |              |                       | Exte                            | ernal                                                   |                         |  |  |  |  |  |  |  |  |

| Dual Boo        | t           |              | External              |                                 |                                                         |                         |  |  |  |  |  |  |  |  |

| Multiple E      | Boot        |              | $\checkmark$          |                                 |                                                         |                         |  |  |  |  |  |  |  |  |

| Bit-strear      | m Encrypti  | ion          |                       | v                               | /                                                       |                         |  |  |  |  |  |  |  |  |

|                 |             | С            | $\checkmark$          | $\checkmark$                    | $\checkmark$                                            | $\checkmark$            |  |  |  |  |  |  |  |  |

| Temp            |             | I            | $\checkmark$          | $\checkmark$                    | $\checkmark$                                            | $\checkmark$            |  |  |  |  |  |  |  |  |

|                 |             | A (AEC-Q100) | $\checkmark$          |                                 |                                                         | $\checkmark$            |  |  |  |  |  |  |  |  |

|                 | 0.4 mm      | n Pitch      | Total                 | I/O (Wide Range, High Performan | ce, ADC <sup>1</sup> ) (D-PHY Quads <sup>2</sup> , PCIe | Lane <sup>3</sup> )     |  |  |  |  |  |  |  |  |

| WLCSP           | 72          | 3.7 x 4.1 mm | 45 (15, 24, 6) (1, 0) |                                 |                                                         |                         |  |  |  |  |  |  |  |  |

|                 | 0.5 mn      | n Pitch      | Total                 | I/O (Wide Range, High Performan | ce, ADC <sup>1</sup> ) (D-PHY Quads <sup>2</sup> , PCIe | Lane <sup>3</sup> )     |  |  |  |  |  |  |  |  |

| QFN             | 72          | 10 x 10 mm   | 46 (18, 22, 6) (1, 0) |                                 |                                                         | 45 (17, 22, 6) (1, 0)   |  |  |  |  |  |  |  |  |

| WLCSP           | 84          | 3.1 x 7.3 mm |                       | 60 (34 , 26, 0) (0, 0)          | 44 (17, 27, 0) (0, 0)                                   |                         |  |  |  |  |  |  |  |  |

| csfBGA          | 121         | 6 x 6 mm     | 77 (23, 48, 6) (2, 0) |                                 |                                                         | 77 (23, 48, 6) (2, 0)   |  |  |  |  |  |  |  |  |

| csBGA           | 289         | 9.5 x 9.5 mm |                       |                                 |                                                         | 179 (99 , 74, 6) (2, 1) |  |  |  |  |  |  |  |  |

|                 | 0.65 m      | m Pitch      | Total                 | I/O (Wide Range, High Performan | ce, ADC <sup>1</sup> ) (D-PHY Quads <sup>2</sup> , PCIe | Lane <sup>3</sup> )     |  |  |  |  |  |  |  |  |

| fcCSP           | 104         | 5.5 x 8.5 mm |                       |                                 | 52 (20, 32, 0) (0, 0)                                   |                         |  |  |  |  |  |  |  |  |

|                 | 0.8 mn      | n Pitch      | Total                 | I/O (Wide Range, High Performan | ce, ADC <sup>1</sup> ) (D-PHY Quads <sup>2</sup> , PCIe | Lane <sup>3</sup> )     |  |  |  |  |  |  |  |  |

|                 | 256         | 14 x 14 mm   | 77 (23, 48,6) (2, 0)  |                                 |                                                         | 162 (82, 74, 6) (2, 1)  |  |  |  |  |  |  |  |  |

| caBGA           | 400         | 17 x 17 mm   |                       |                                 |                                                         | 191 (111, 74, 6) (2, 1) |  |  |  |  |  |  |  |  |

Each ADC pin count reflects using dedicated complement pair and vRef

Each D-PHY quad consists of 4 D-PHY data lanes

Each PCIe lane consists of a Tx and Rx complement pair

# Control and Security

## MachXO5-NX - Secure, Control Bridging and I/O Expansion FPGAs

|                  | Features        |               |                       |                                          | MachXO5™-NX                               |                                 |                                           |

|------------------|-----------------|---------------|-----------------------|------------------------------------------|-------------------------------------------|---------------------------------|-------------------------------------------|

|                  | Device          |               | LFMXO5-15D            | LFMXO5-25                                | LFMXO5-55T                                | LFMXO5-55TD                     | LFMXO5-100T                               |

| Logic Cells¹ (k) |                 |               | 14                    | 27                                       | 53                                        | 53                              | 96                                        |

|                  |                 | Blocks        | 20                    | 80                                       | 166                                       | 166                             | 208                                       |

| EBR SRAM         |                 | kbits         | 360                   | 1,440                                    | 2,988                                     | 2988                            | 3,744                                     |

| Distributed RAM  |                 | kbits         | 95                    | 184                                      | 320                                       | 320                             | 639                                       |

|                  |                 | Blocks        | 1                     | 1                                        | 5                                         | 5                               | 7                                         |

| Large RAM (LRA   | M)              | kbits         | 512                   | 512                                      | 2,560                                     | 2,560                           | 3,584                                     |

| Multipliers      |                 | 18 x 18       | 16                    | 20                                       | 146                                       | 146                             | 156                                       |

| PCIe Hard IP     |                 |               | 0                     | 0                                        | 1                                         | 1                               | 1                                         |

| PCIe Lanes       |                 |               | 0                     | 0                                        | 2                                         | 2                               | 2                                         |

| SERDES maxim     | um speed        | Gbps          | 0                     | 0                                        | 5                                         | 5                               | 5                                         |

| SGMII (1.25 Gbp  | s) CDR Hard IP  |               | 2                     | 2                                        | 2                                         | 2                               | 2                                         |

| SGMII (1.25 Gbp  | s) Lanes        |               | 2                     | 2                                        | 2                                         | 2                               | 2                                         |

| GPLL             |                 |               | 2                     | 2                                        | 4                                         | 4                               | 4                                         |

| ADC Blocks       |                 |               | 2                     | 2                                        | 2                                         | 2                               | 2                                         |

| 450 MHz High Fr  | equency Oscill  | ator          | 1                     | 1                                        | 1                                         | 1                               | 1                                         |

| 128 KHz Low Po   | wer Oscillator  |               | 1                     | 1                                        | 1                                         | 1                               | 1                                         |

| DDR Memory Su    | pport (Up to 10 | 66 Mbps)      | DDR3/3L               | DDR3/3L                                  | DDR3/3L, LPDDR4                           | DDR3/3L, LPDDR4                 | DDR3/3L, LPDDR4                           |

| Non-Volatile Co  | nfig Memory     |               | Yes                   | Yes                                      | Yes                                       | Yes                             | Yes                                       |

| On-chip Multi-Bo | oot             |               | 2                     | 3                                        | 3                                         | 3                               | 3                                         |

| User Flash Memo  | ory (kb)        |               |                       | 9,216 <sup>2</sup> / 15,360 <sup>2</sup> | 56,832 <sup>2</sup> / 79,872 <sup>2</sup> |                                 | 56,832 <sup>2</sup> / 79,872 <sup>2</sup> |

| Bitstream Encry  | ption           |               | AES-256               | AES-256                                  | AES-256                                   | AES-256                         | AES-256                                   |

| Bitstream Auther | ntication       |               | ECDSA-384             | ECDSA-256                                | ECDSA-256                                 | ECDSA-384                       | ECDSA-256                                 |

| Core Vcc         |                 |               | 1.0 V                 | 1.0 V                                    | 1.0 V                                     | 1.0 V                           | 1.0 V                                     |

|                  |                 | С             | $\checkmark$          | $\checkmark$                             | $\checkmark$                              | $\checkmark$                    | $\checkmark$                              |

| Temp.            |                 | I             | $\checkmark$          | $\checkmark$                             | $\checkmark$                              | $\checkmark$                    | $\checkmark$                              |

|                  |                 | A (AEC-Q100)  |                       |                                          |                                           |                                 |                                           |

| 0.8 mm Spacing   | (Package type,  | #Balls, Size) |                       | Total I/O (Wide Rang                     | ge, High Performance) / A                 | ADC <sup>3</sup> / SERDES Lanes |                                           |

| BBG256           | 256             | 14 x 14 mm    | 199 (159, 40) / 6 / 0 | 199 (159, 40) / 6 / 0                    |                                           |                                 |                                           |

| BBG400           | 400             | 17 x 17 mm    | 299 (251, 48) / 6 / 0 | 299 (251, 48) / 6 / 0                    | 291 (159, 132) / 6 / 2                    | 291 (159, 132) / 6 / 2          | 291 (159, 132) / 6 / 2                    |

Logic Cells = LUTs x 1.2 effectiveness

Initialize 100% of memory / Initialize 0% of memory

3) Dedicated inputs for ADC

## Mach-NX & MachXO3/3D - Secure, Control Bridging and I/O Expansion FPGAs

|          | Featu                  | res                    | Mach™-NX               | Mach             | KO3D™        |             |                  | Mach)        | (O3L™            |                 |                  |              |                  | MachX          | O3LF™                  |                  |               |

|----------|------------------------|------------------------|------------------------|------------------|--------------|-------------|------------------|--------------|------------------|-----------------|------------------|--------------|------------------|----------------|------------------------|------------------|---------------|

|          | Devid                  | ce                     | LFMNX-50               | LCMX03D-4300     | LCMXO3D-9400 | LCMXO3L-640 | LCMXO3L-1300     | LCMX03L-2100 | LCMX03L-4300     | LCMXO3L-6900    | LCMXO3L-9400     | LCMXO3LF-640 | LCMX03LF-1300    | LCMXO3LF-2100  | LCMXO3LF-4300          | LCMXO3LF-6900    | LCMXO3LF-9400 |

|          | LUT                    | Ś                      | <br>11280 <sup>8</sup> | 4300             | 9400         | <b>6</b> 40 | 1300             | 2100         | 4300             | 6900            | 9400             | <b>6</b> 40  | 1300             | 2100           | 4300                   | 6900             | 9400          |

| EBR SF   | RAM                    | # of Blocks            | 48                     | 10               | 48           | 7           | 7                | 8            | 10               | 26              | 48               | 7            | 7                | 8              | 10                     | 26               | 48            |

|          | kbit                   | s                      | 432                    | 92               | 432          | 64          | 64               | 74           | 92               | 240             | 432              | 64           | 64               | 74             | 92                     | 240              | 432           |

| Distrib. | RAM                    | kbits                  | 73                     | 34               | 73           | 5           | 10               | 16           | 34               | 54              | 73               | 5            | 10               | 16             | 34                     | 54               | 73            |

| UFN      | Λ                      | kbits                  | 1064/26694             | 367/11224        | 1088/26934   |             |                  |              |                  |                 |                  | 64           | 64               | 80             | 96                     | 256              | 448           |

| Config   | uratior                | n Memory               | Dual Flash             | Dual Flash       | Dual Flash   |             |                  | Interna      | al NVM           |                 | -                |              |                  | Fla            | ash                    | -                |               |

| I        | Dual B                 | oot                    | √6                     | 、<br>、           | /6           |             |                  | V            | 5                |                 |                  |              |                  | V              | /5                     |                  |               |

| Embedde  | ed Func                | ction Blocks           | I²C (2                 | ?), SPI (1), Tin | ner (1)      |             | I <sup>2</sup> C | (2), SPI (   | 1), Time         | r (1)           |                  |              | I <sup>2</sup> C | (2), SPI (     | (1), Time              | r (1)            |               |

| Crypto K | Key Stre               | ength (bits)           | 384                    | 256              | 256          |             |                  |              |                  |                 |                  |              |                  |                |                        |                  |               |

|          |                        | 1 V                    | ~                      |                  |              |             |                  |              |                  |                 |                  |              |                  |                |                        |                  |               |

| Core \   | /cc                    | 1.2 V                  |                        |                  | $\checkmark$ |             |                  | v            | /                |                 |                  |              |                  | `              | /                      |                  |               |

|          |                        | 2.5 - 3.3 V            |                        | $\checkmark$     | $\checkmark$ |             |                  |              | $\checkmark$     |                 |                  |              |                  |                | $\checkmark$           |                  |               |

|          |                        | A (AEC-<br>Q100)       |                        | $\checkmark$     | $\checkmark$ |             |                  |              |                  |                 |                  | √            |                  |                |                        |                  |               |

| Tem      | р.                     | С                      | $\checkmark$           | $\checkmark$     | $\checkmark$ |             |                  | v            | /                |                 | -                |              |                  | Ň              | /                      |                  |               |

| -        | -                      | I                      | $\checkmark$           | $\checkmark$     | $\checkmark$ |             |                  | v            | /                |                 |                  |              |                  |                | /                      |                  |               |

| 0.4      | mm Sp                  | pacing                 |                        |                  |              |             |                  |              |                  |                 |                  |              |                  |                |                        |                  |               |

|          | <b>36</b> <sup>1</sup> | 2.5 x 2.5 mm           |                        |                  |              |             | 28               |              |                  |                 |                  |              | 28               |                |                        |                  |               |

| WLCSP    | <b>49</b> <sup>1</sup> | 3.2 x 3.2 mm           |                        |                  |              |             |                  | 38           |                  |                 |                  |              |                  | 38             |                        |                  |               |

|          |                        | 3.8 x 3.8 mm           |                        |                  |              |             |                  |              | 63               |                 |                  |              |                  |                | 63                     |                  |               |

|          | mm Sp                  | pacing                 |                        |                  |              |             |                  |              | Total I          | /0              |                  |              |                  |                |                        |                  |               |

| QFN      | 72                     | 10 x 10 mm             |                        | 58               | 58           |             |                  | 20           |                  |                 |                  |              |                  | 20             |                        |                  |               |

| (7.5.1   | 121 <sup>1</sup>       | 6 x 6 mm               |                        |                  |              |             | 10               | 00           | 206              |                 |                  |              | 10               | 00             | 206                    |                  |               |

| csfBGA   | 256 <sup>1</sup>       | 9 x 9 mm               |                        |                  |              |             |                  | 20           | 200              | 281             |                  |              |                  | 2              | 200<br>68 <sup>7</sup> | 281              |               |

| sBGA     | 324 <sup>1</sup>       | 10 x 10 mm<br>8 x 8 mm |                        |                  |              |             |                  | 20           |                  | 201             |                  |              | 10               | )47            |                        | 201              |               |

| TQFP     | 100                    | 14 x 14 mm             |                        |                  |              |             |                  |              |                  |                 |                  |              | 797              | / <del>-</del> |                        |                  |               |

|          |                        | pacing                 |                        |                  |              |             |                  |              | Total I          | /0              |                  |              |                  |                |                        |                  |               |

| WLCSP    |                        | 5.2 x 6.2 mm           |                        |                  | 58           |             |                  |              |                  |                 |                  |              |                  |                |                        |                  |               |

| 0.8      | mm Sp                  | pacing                 |                        |                  |              |             |                  |              | Total I          | /0              |                  |              |                  |                |                        |                  |               |

|          | 256                    | 14 x 14 mm             | 188                    | 2067             | 2067         |             |                  | 20           | 16 <sup>2</sup>  |                 | 206 <sup>3</sup> |              |                  | 2067           |                        | 206 <sup>2</sup> | 206           |

| D.C.     | 324                    | 15 x 15 mm             |                        |                  |              |             |                  |              | 279 <sup>2</sup> |                 |                  |              |                  | 27             | 797                    | 279²             |               |

| caBGA    | 400                    | 17 x 17 mm             |                        |                  | 335          |             |                  |              | 33               | 35 <sup>2</sup> | 335 <sup>3</sup> |              |                  |                | 33                     | 35 <sup>2</sup>  | 335           |

|          | 484                    | 19 x 19 mm             | 378                    |                  | 3837         |             |                  |              |                  |                 | 384 <sup>3</sup> |              |                  |                |                        |                  | 384           |

| 1.00     | 0 mm S                 | Spacing                |                        |                  |              |             |                  |              | Total I          | /0              |                  |              |                  |                |                        |                  |               |

| tBGA     | 256 <sup>2</sup>       | 17 x 17 mm             |                        | 206              |              |             |                  |              |                  |                 |                  |              |                  |                |                        |                  |               |

Package is only available for E=1.2 V devices.

Package is only available for C=2.5 V/3.3 V devices.

Package is available for both E=1.2 V and C=2.5 V/3.3 V devices.

When Dual Boot is disabled, image space can be repurposed as extra UFM.

5) Dual Boot supported with external boot Flash.

6) Dual Boot is supported by on chip dual configuration flash memory.

7) Available in automotive grade

8) Shown in LCs

## MachXO2 & LatticeXP2 Series – Bridging and I/O Expansion FPGAs

|                             | Feature                                                   | es                                                                                   |              |                 |               | N             | lachXO2                 | тм           |                |                                |               |            |            | Lattice                 | XP2™        |             |  |

|-----------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|--------------|-----------------|---------------|---------------|-------------------------|--------------|----------------|--------------------------------|---------------|------------|------------|-------------------------|-------------|-------------|--|

|                             | Devico                                                    | 9                                                                                    | LCMXO2 - 256 | LCMXO2 - 640    | LCMXO2 - 640U | LCMXO2 - 1200 | LCMXO2 - 1200U          | LCMXO2- 2000 | LCMXO2 - 2000U | LCMXO2 - 4000                  | LCMXO2 - 7000 | LFXP2 - 5E | LFXP2 - 8E | LFXP2 - 17E             | LFXP2 - 30E | LFXP2 - 40E |  |

|                             |                                                           |                                                                                      |              |                 |               |               |                         |              |                |                                |               |            |            |                         |             |             |  |

| EBR SRAM                    | LUTs                                                      | # of Blocks                                                                          | 256<br>0     | 640<br>2        | 640<br>7      | 1280<br>7     | 1280<br>8               | 2112<br>8    | 2112<br>10     | 4320<br>10                     | 6864<br>26    | 5 k<br>9   | 8 k<br>12  | 17 k<br>15              | 29 k<br>21  | 40 k<br>48  |  |

| kbits                       |                                                           | # OT BIOCKS                                                                          | 0            | 18              | 64            | 64            | 0<br>74                 | 0<br>74      | 92             | 92                             | 240           | 9<br>166   | 221        | 276                     | 387         | 885         |  |

| Distrib. RAM                |                                                           | kbits                                                                                | 2            | 5               | 5             | 10            | 10                      | 16           | 16             | 34                             | 54            | 100        | 18         | 35                      | 56          | 83          |  |

| UFM                         |                                                           | kbits                                                                                | 0            | 24              | 64            | 64            | 80                      | 80           | 96             | 96                             | 256           | 10         | 10         |                         | 50          | 03          |  |

|                             |                                                           | 18x18 Blocks                                                                         | 0            | 24              | 04            | 04            | 00                      | 80           | 30             | - 30                           | 230           | 3          | 4          | 5                       | 7           | 8           |  |

| sysDSP™ B                   | locks                                                     | Multipliers                                                                          |              |                 |               |               |                         |              |                |                                |               | 12         | 16         | 20                      | 28          | 32          |  |

| PLL + DLL                   |                                                           | wultipliers                                                                          |              |                 |               | 1             | +2                      |              |                | 2+2                            |               |            | +0         | 20                      | 4+0         | 32          |  |

|                             | •                                                         |                                                                                      |              |                 |               |               |                         | 0000000      | ימססקו         |                                |               | Z·         |            | DDR/2 40                | -           |             |  |

| DDR Support                 |                                                           |                                                                                      |              |                 |               |               | DR 266, D<br>ternal Fla |              | , LPUUR2       | 200                            |               |            |            | DDR/2 40<br>Iternal Fla |             |             |  |

| Configuration               | n wemory                                                  |                                                                                      |              |                 |               | 11            |                         | sn           |                |                                |               |            | Iſ         |                         | ISN         |             |  |

| Dual Boot4<br>Bit-stream Ei | non <i>untic</i> -                                        |                                                                                      |              |                 |               |               | $\checkmark$            |              |                |                                |               |            |            | √<br>√                  |             |             |  |