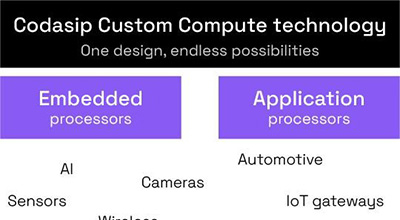

Codasip 700系列正式问世,赋能定制计算!

如今,利用新的方法来创造差异化的产品是当今技术创新者们所追求的目标。当半导体扩展规律已经显示出极限时,我们该如何满足对更高计算性能的需求?办法只有一个:为特定需求定制计算。

如今,利用新的方法来创造差异化的产品是当今技术创新者们所追求的目标。当半导体扩展规律已经显示出极限时,我们该如何满足对更高计算性能的需求?办法只有一个:为特定需求定制计算。

推出高度灵活的700系列,以实现无限创新

该解决方案即使在最复杂的异构和定制化设计中也能显著提高生产效率

在人们的生活中,声学应用普遍存在,听障患者的助听器、医院的超声波检查、大街上的环境噪声检测,都是非常典型的应用。而随着计算处理、安全、网络等技术的持续演进,声学应用设备也在不断提升其数字化和智能化程度,从而为使用者带来更大的便利和更优的体验。

Axel Strotbek为Codasip带来了其任职董事会专业人士的丰富经验,曾长期在奥迪公司担任首席财务官

外设IP的一站式购买可简化定制RISC-V处理器设计

在本文中,我们将以西门子EDA处理器验证应用程序为例,结合Codasip L31这款广受欢迎的RISC-V处理器IP提供的特性,来介绍一种利用先进的EDA工具,在实际设计工作中对处理器进行验证的具体方法。

RISC-V的开放性允许定制和扩展基于 RISC-V 内核的架构和微架构,以满足特定需求。这种对设计自由的渴望也正在将验证部分的职责转移到不断壮大的开发人员社群。然而,随着越来越多的企业和开发人员转型RISC-V,大家才发现处理器验证绝非易事。

随着越来越多的研究伙伴加入以及新技术和新产品的不断披露,欧盟于2022年底启动的NimbleAI这一前沿项目在喧嚣的GPT热潮中,开始展现出一条新的智能化和数字化转型之道。NimbleAI旨在推动神经形态视觉(neuromorphic vision)传感和处理技术的发展和研究。

IAR获得ISO 26262认证的工具支持基于屡获殊荣的Codasip L31内核的参考设计