RISC-V芯片出货量突破100亿!爱普特微电子助力中国RISC-V MCU生态建设

在近日召开的嵌入式世界展览会上,RISC-V国际公司的首席执行官Calista Redmond表示RISC-V芯片出货量突破100亿:“我们估计市场上已经有100亿个核。”

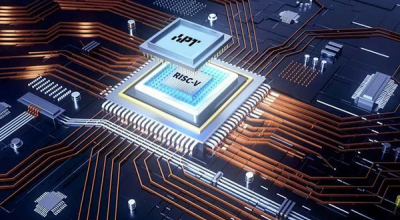

RISC-V是一种基于精简指令集计算机(RISC)架构的开源指令集架构(ISA)。与其他商业架构(如ARM或x86)不同,RISC-V是由加州大学伯克利分校的学术界和行业合作伙伴开发的,它是一种开放、免费的指令集架构,具有可扩展性和灵活性。

RISC-V的设计目标是提供一种简洁、灵活且可扩展的架构,使其能够适应各种不同的应用场景,从微控制器到超级计算机等。RISC-V架构采用了模块化设计的理念,定义了基本的指令集,并允许用户根据自己的需求添加自定义指令集扩展(ISA扩展),从而实现对特定应用的优化。

由于其开放的特性,RISC-V架构在学术界和工业界都受到了广泛的关注和采用。它已经成为了各种不同领域的研究和开发的重要工具,如嵌入式系统、物联网、人工智能、边缘计算等。很多公司和组织都开始采用RISC-V架构设计自己的处理器芯片或者开发板,以满足不同领域的需求。

总的来说,RISC-V作为一种开放、免费的指令集架构,具有可扩展性、灵活性和通用性,已经成为了计算机体系结构领域的重要创新,并在全球范围内得到了广泛的应用和推广。

在近日召开的嵌入式世界展览会上,RISC-V国际公司的首席执行官Calista Redmond表示RISC-V芯片出货量突破100亿:“我们估计市场上已经有100亿个核。”

兆易创新与Ashling联合宣布,兆易创新GD32V系列RISC-V内核通用MCU已与Ashling旗下的RiscFree™工具链全面适配,包含集成开发环境(IDE)和软件开发支持。

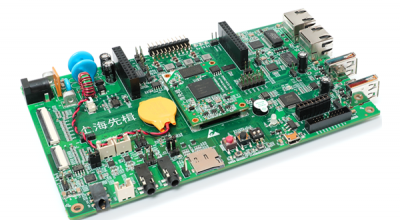

近日,先楫半导体与国际领先的嵌入式开发系统供应商德国SEGGER Microcontroller GmbH联合宣布:通过买断许可,先楫半导体向所有使用其HPM6000系列RISC-V微控制器的客户提供免费的SEGGER的多平台集成开发环境(IDE)“Embedded Studio”,共同推动RISC-V生态的发展。

近日,广东跃昉科技有限公司(“跃昉科技”)宣布推出了一款全新的RISC-V SoC产品NB2。

瑞萨电子集团(TSE:6723)今日宣布,推出基于64位RISC-V CPU内核的RZ/Five通用微处理器(MPU)——RZ/Five采用Andes AX45MP,基于RISC-V CPU指令集架构(ISA),增强了瑞萨现有基于Arm® CPU内核的MPU阵容,扩充了客户的选择,并在产品开发过程中提供更大灵活性。

电子创新网采访数十位半导体高管,并以"行业领袖看2022”系列问答形式向业界传达知名半导体眼中的2022 ,这是该系列第八篇报道——来自IAR Systems公司首席执行官Richard Lind的答复。

随着物联网爆发以及处理器应用日益场景化,开源指令集RISC-V推出后立即受到业界尤其是中国厂商的追捧!

深圳市爱普特微电子有限公司董事兼副总经理袁永生表示爱普特自成立后就一直坚持国产MCU ,经过5年时间,打造了全自主知识产权的纯国产MCU ,公司不像其他MCU走follow之路,是打造自己特色的MCU ,坚持国产创新!

上海先楫半导体科技有限公司于近日发布了全新的高性能实时RISC-V微控制器HPM6000系列。

芯片是数字化能力入口之一。大会期间,作为中国移动旗下专业芯片子公司,中移芯昇(芯昇科技有限公司)携中国移动首款基于RISC-V内核的MCU芯片——CM32M4xxR隆重亮相。