作者:刘煜

目录

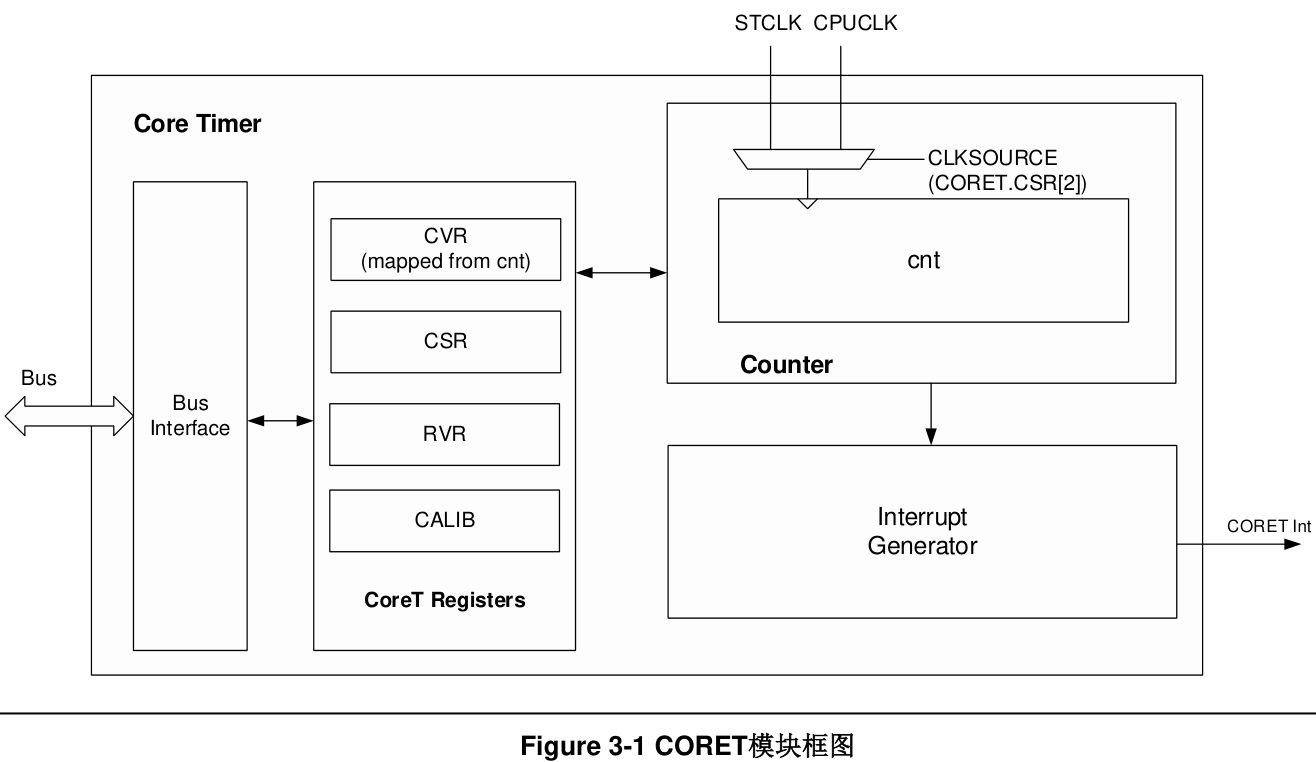

1. 24位递减计数器

2. 递减到0可以产生中断

3. 递减到0需软件重新置位

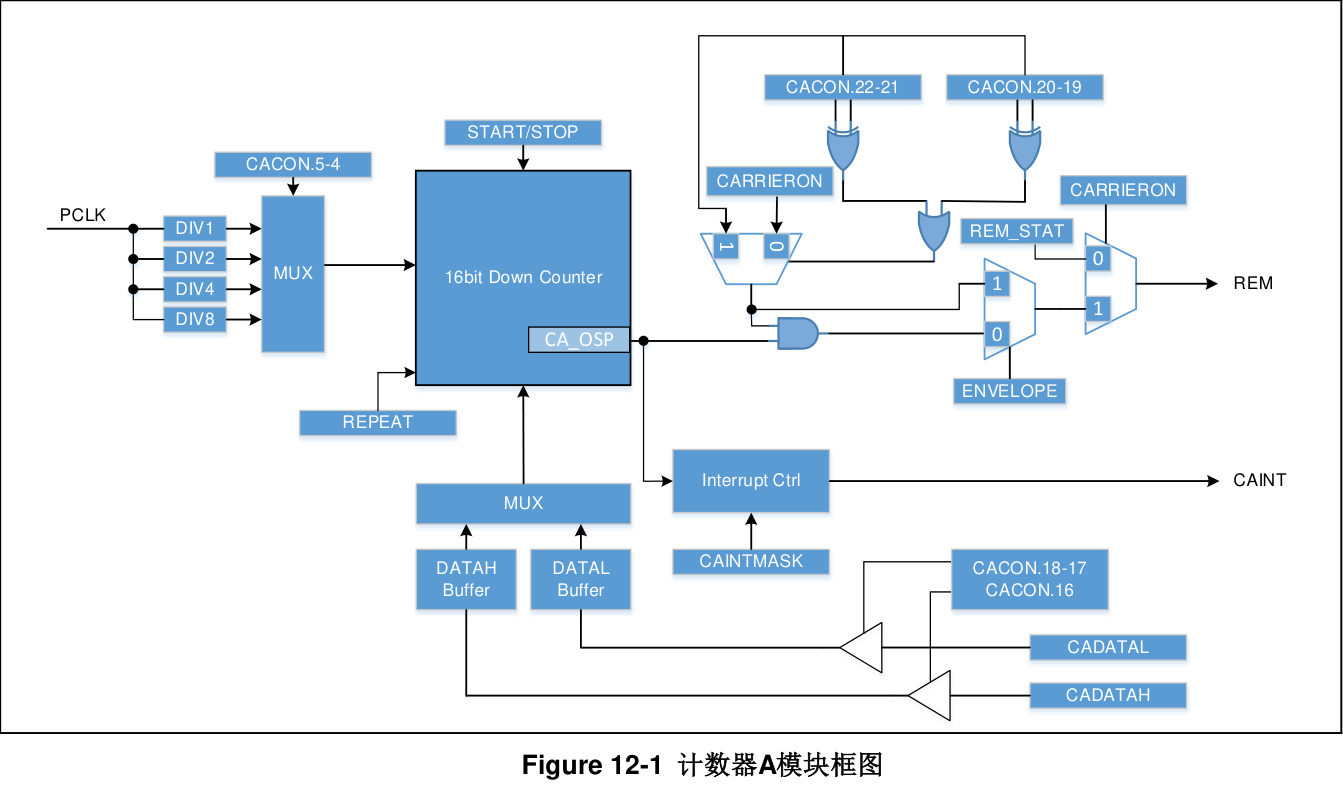

1. 16位递增计数器

2. 16位预分频器

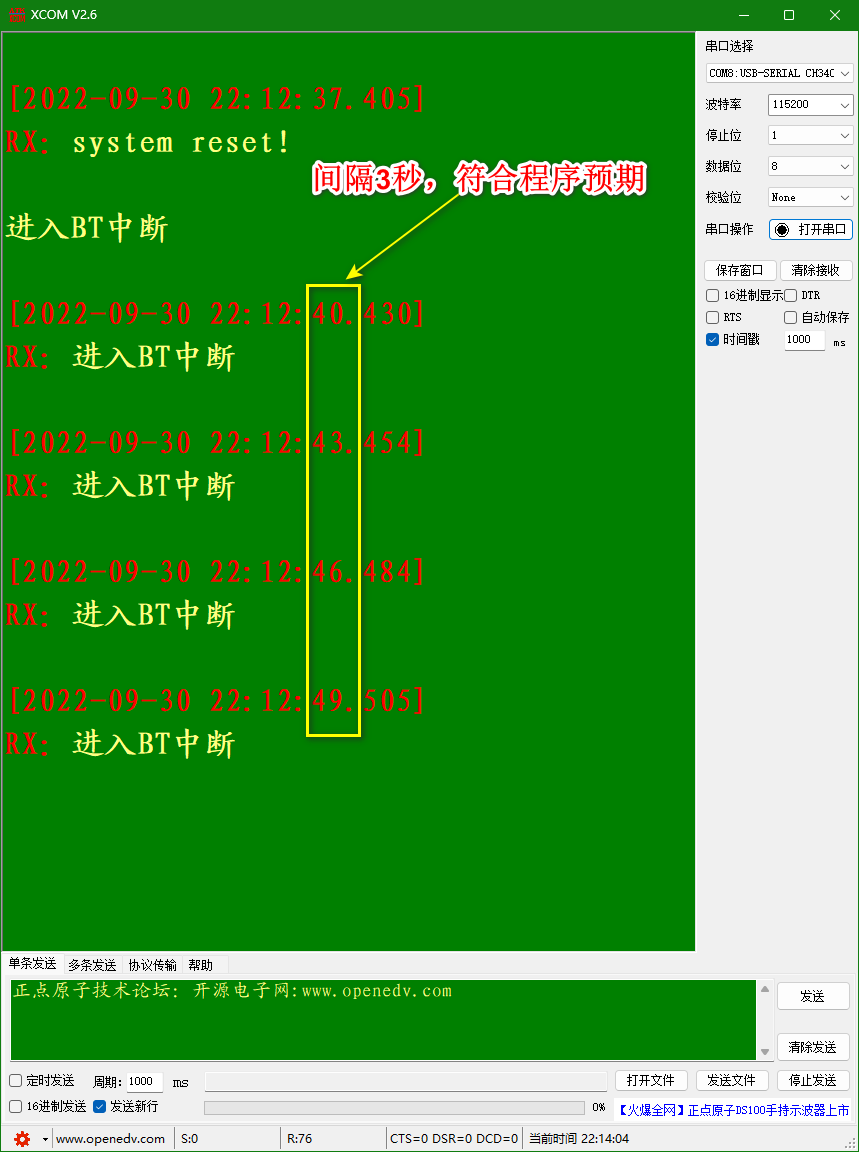

3. PWM输出

4. 支持ETCB

5. 四类中断

a) PEND事件:计数器周期结束时发生。

b) CMP事件:计数器计数值等于CMP寄存器设置时发生。

c) OVF事件:计数器计数溢出(0xFFFF)时发生。

d) TRGEV事件:同步触发输出事件有输出是发生

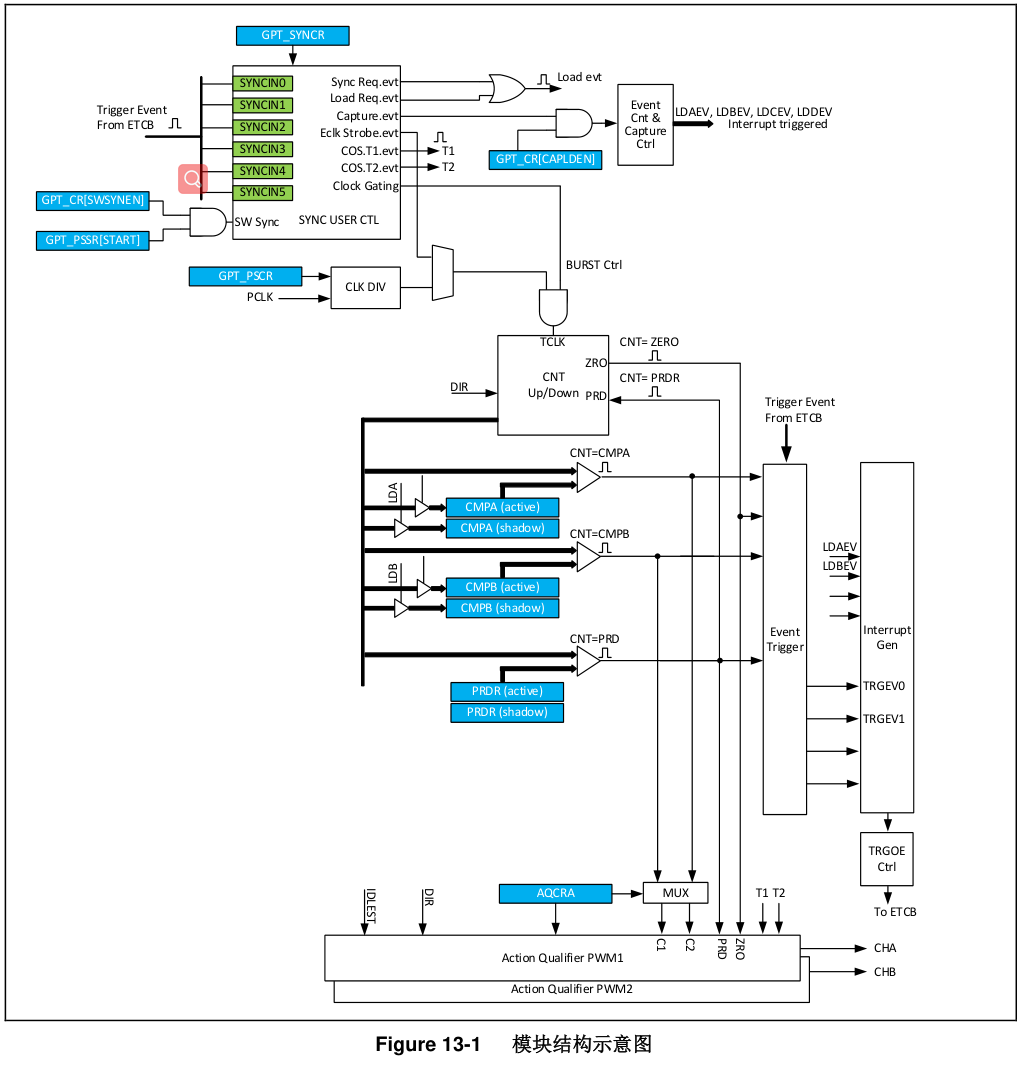

1. 16/24 位可复位计数器(GPT0 为 24bit; GPT1 为 16bit;)

2. 可编程计数器计数方式

a) 递增计数(Up-counting)

b) 递减计数(Down-counting)

c) 递增递减计数(Up-down-counting)

3. 支持事件计数器,可通过配置事件计数器(最大 15)触发相应中断

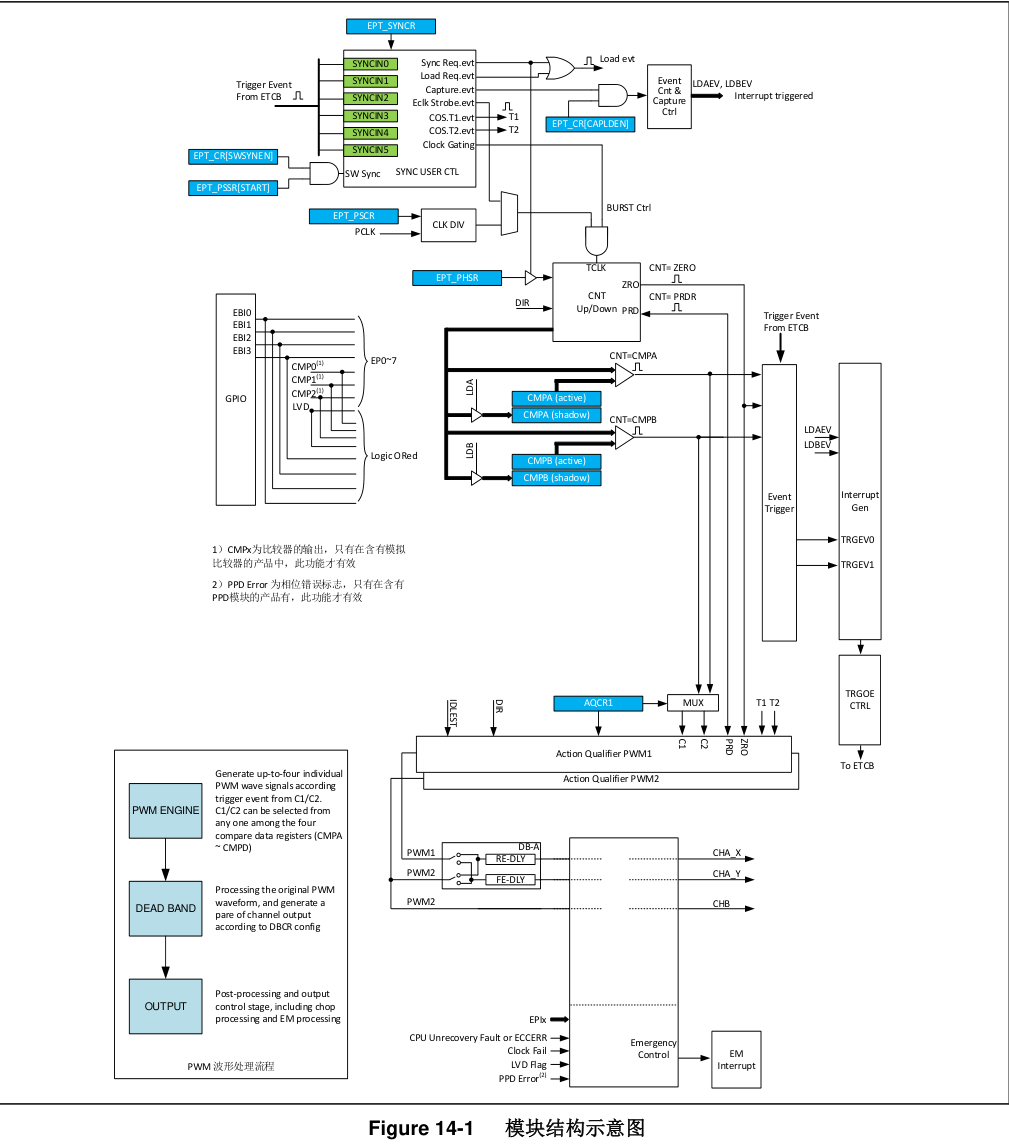

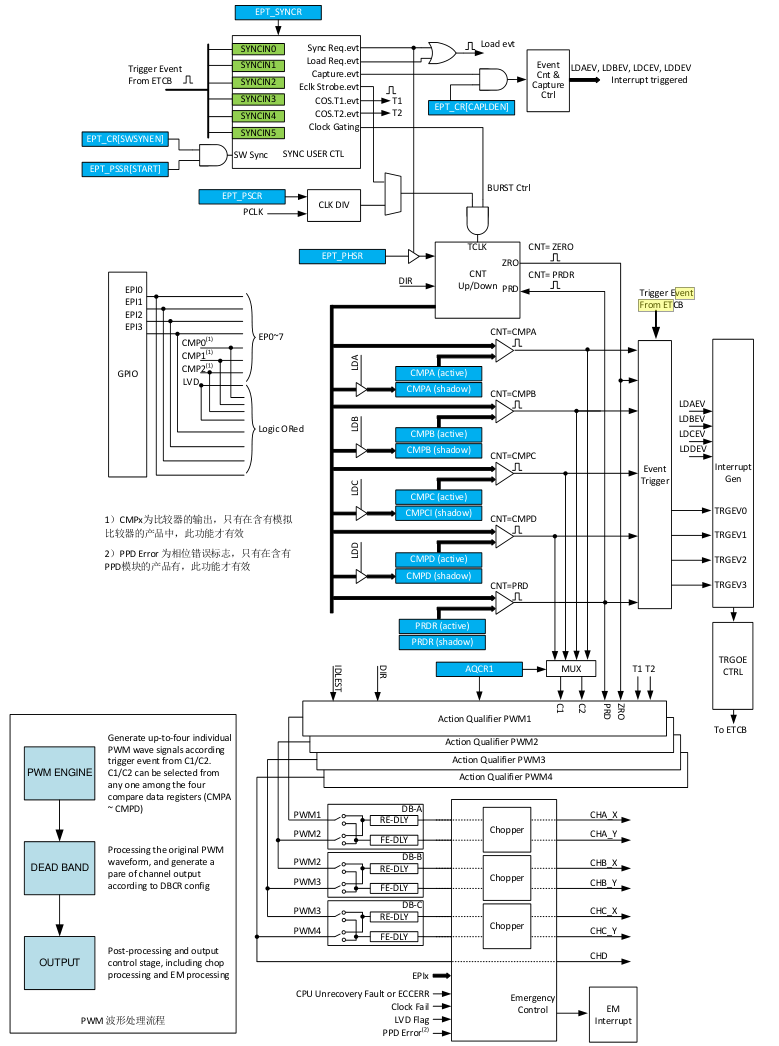

1. 16 位可复位计数器

2. 可编程计数器计数方式

a) 递增计数(Up-counting)

b) 递减计数(Down-counting)

c) 递增递减计数(Up-down-counting)

3. 两路波形产生控制单元,支持双路独立输出:

a) 两路独立的 PWM 输出,单边沿工作

b) 两路独立的 PWM 输出,双边沿对称工作

c) 1 组独立的 PWM 互补输出 + 1 路独立的 PWM 输出

4. 异常事件发生时,自动触发预设波形输出

5. 触发源包括 GPIO 输入,其他外设触发,软件设置和事件触发

6. 支持单次触发和连续触发模式

7. 支持单脉冲输出模式

8. 支持事件计数器,可通过配置事件计数器(最大 15)触发相应中断

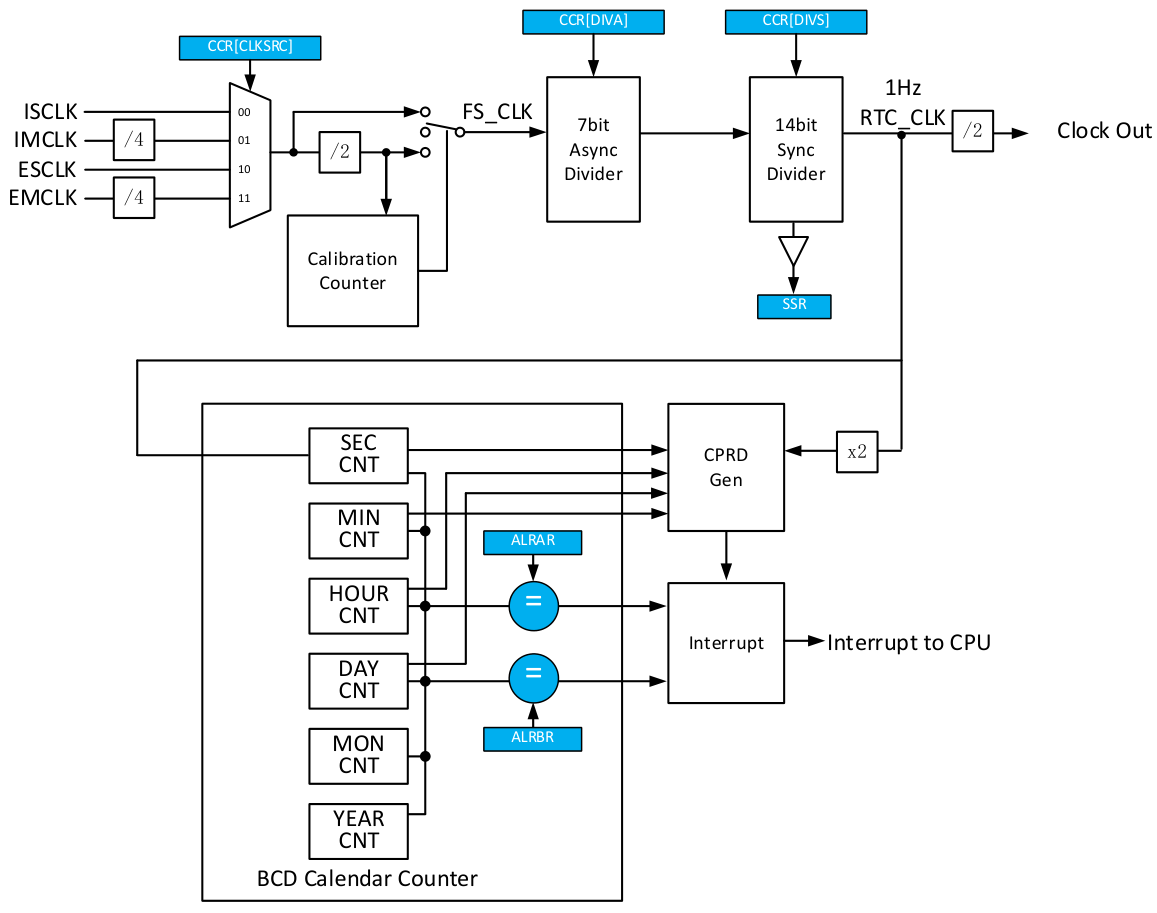

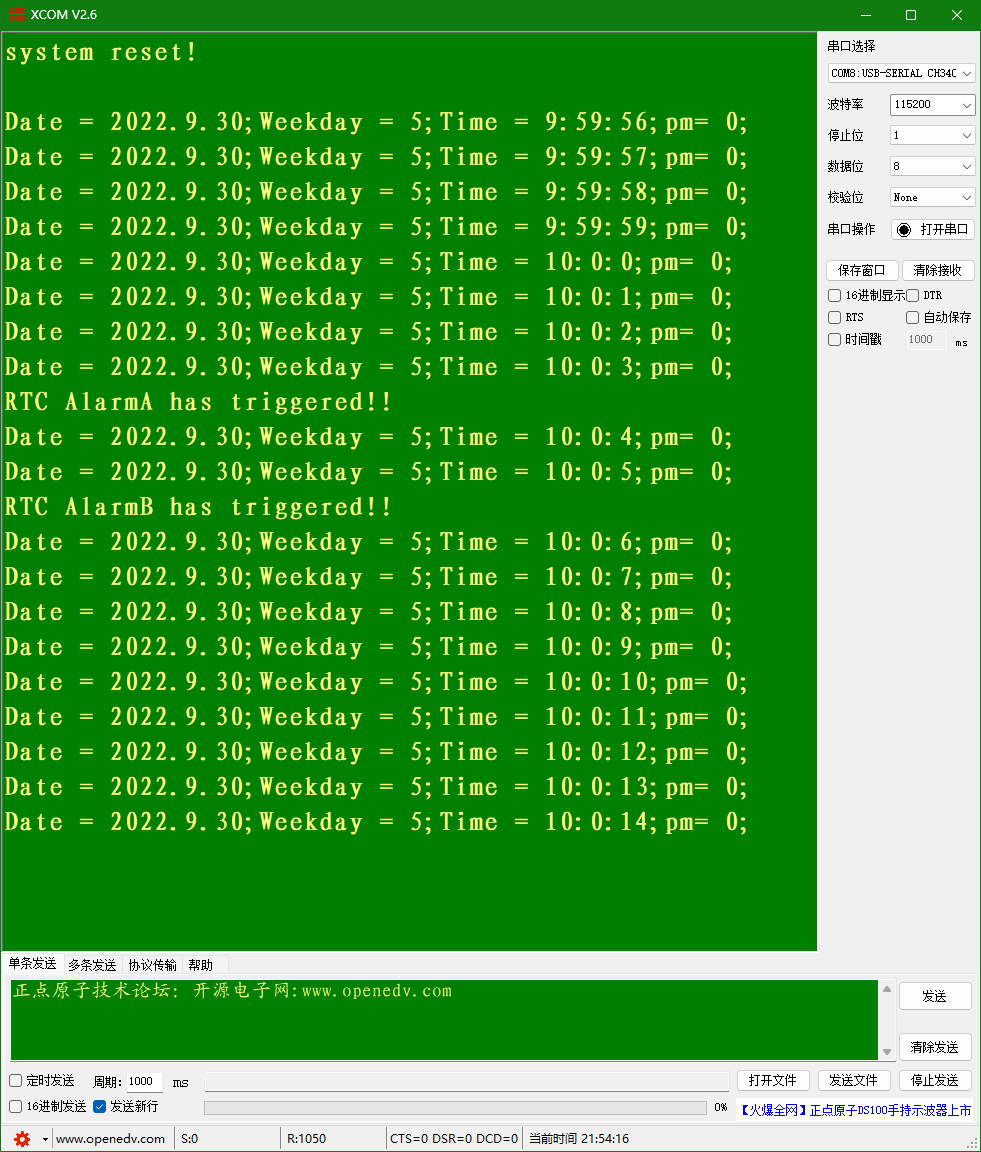

1. 所有低功耗模式下均可独立运行

2. 支持系统唤醒

3. BCD 编码

4. 提供实时的日历和时间信息

5. 产生周期性的中断事件

6. 一旦初始化成功并开始工作,任何复位信号均不能影响其工作,除非重新上电

7. 支持多个时钟源,包括外部晶振、内部低速振荡器和内部主振荡器

1. 16 位递增计数器

2. 4 Bit 预分频控制,支持(1,2,4,8,16,32,64,128,256,512,1024,2048,4096 分频)

3. 支持多种计数时钟:

a) 内部时钟:ISCLK, IMCLK, EMCLK,ESCLK 或 PCLK

b) 外部时钟:LPT_IN(当没有内部时钟时,可以作为脉冲计数)

c) 一路独立的 PWM 输出

4. 一个比较值寄存器

5. 支持连续或单次计数模式

6. 支持通过 ETCB 触发

7. 支持脉冲和 PWM 输出模式

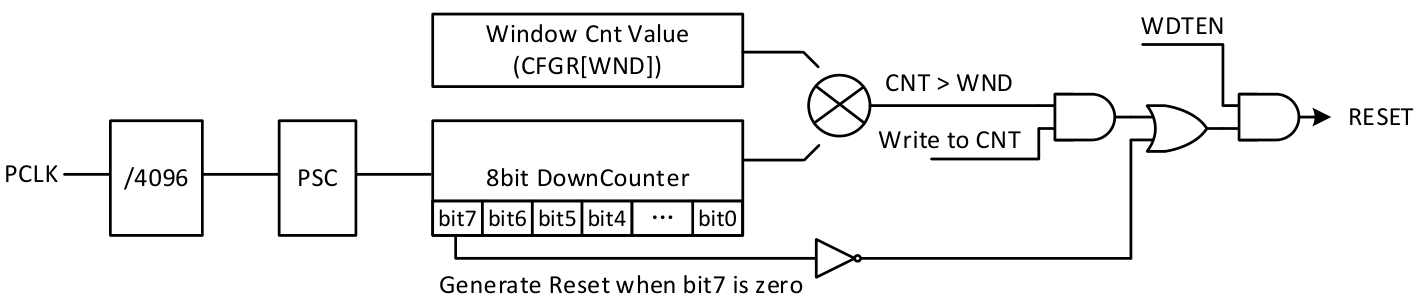

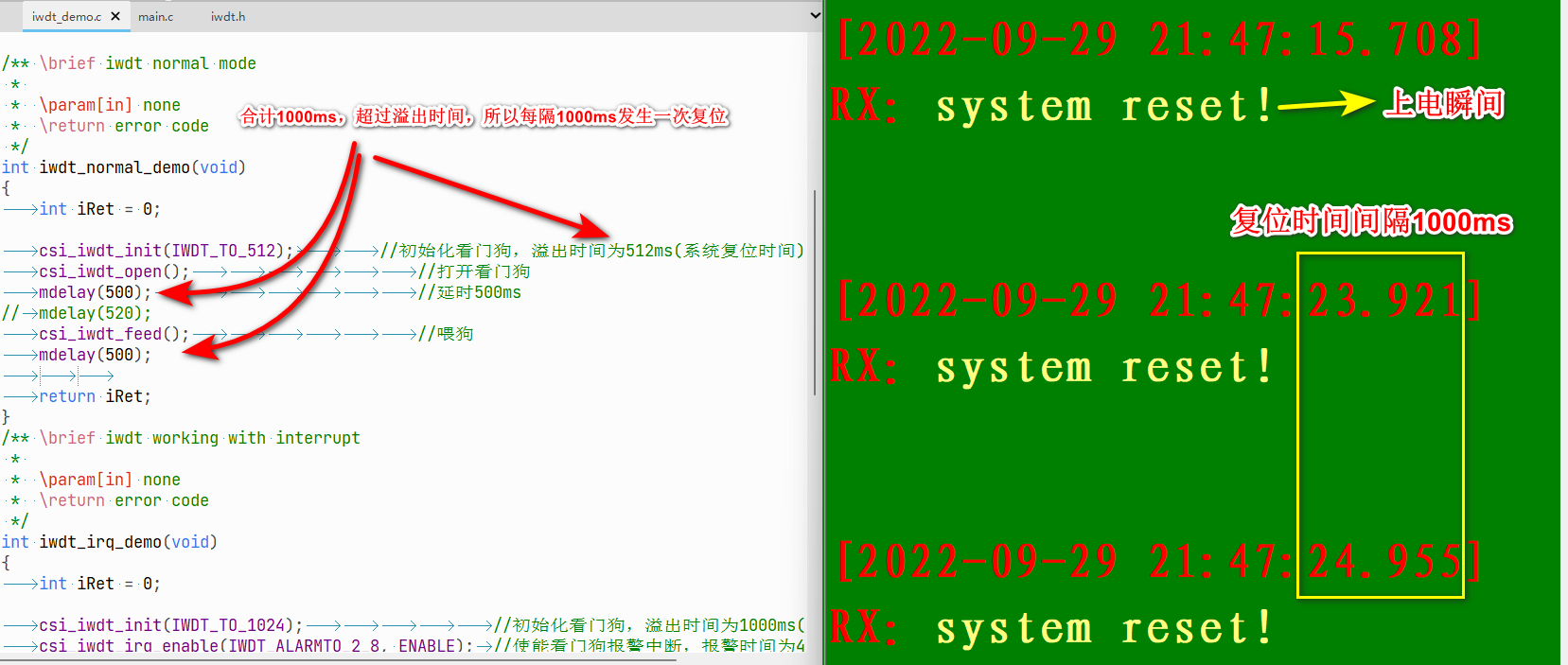

1. 8 位可编程递减计数器

2. 预设计数器时钟分频器:Div (1/2/4/8 x 4096)

a) 计数器时钟基于 PCLK 工作

b) 分频器的基础分频为 PCLK/4096

c) 可选择基于 4096 分频后的二次分频:DIV1,DIV2、DIV4 和 DIV8

3. 产生复位的条件:

a) 递减计数器计数器值小于 0x80

b) 软件刷新计数器发生在预设窗口外

c) 软件写入的刷新计数器的数值小于 0x80

4. 报警中断:当计数器值等于 0x80 时,可产生中断

1. 中断可作为处理器在 DEEP-SLEEP 模式下定时唤醒的中断源

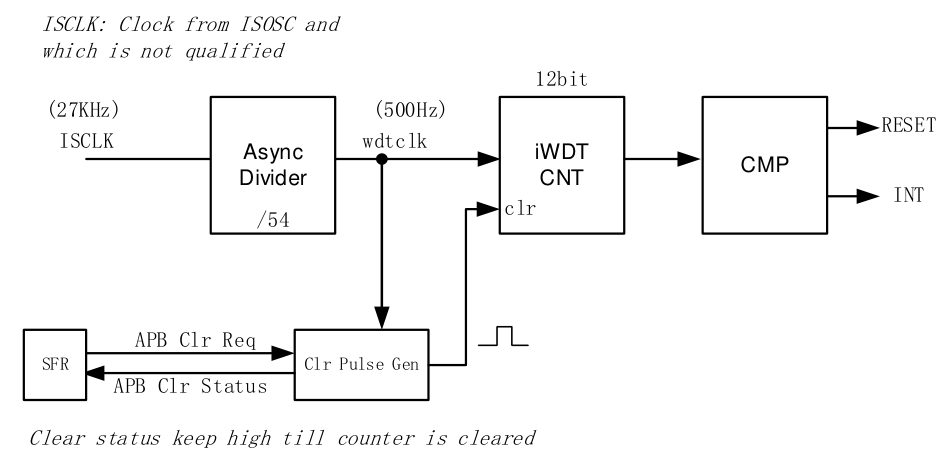

2. 12 位的 Free Running递减计数器

3. 一旦使能则必须在计数器溢出前进行清除,否则会产生系统复位

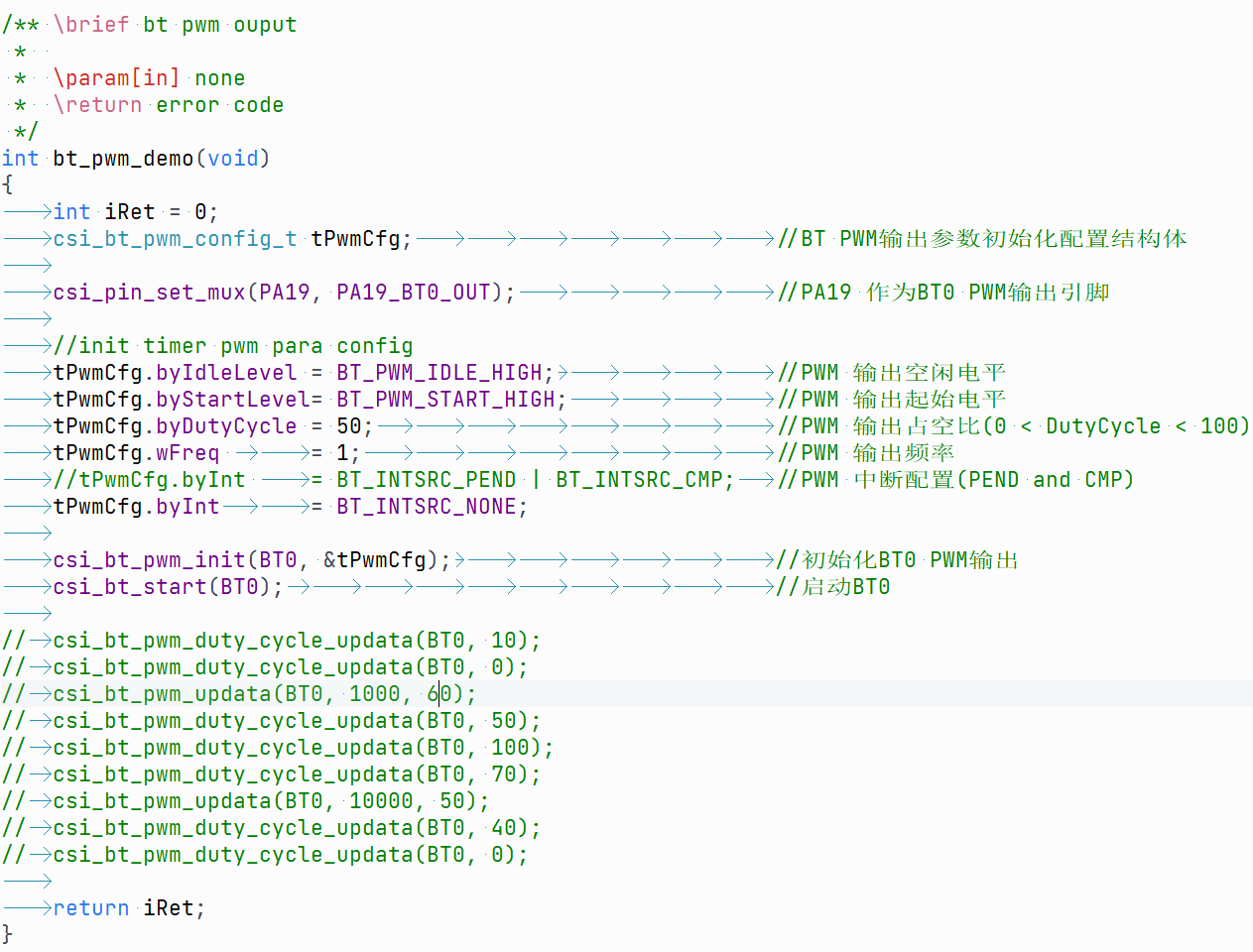

主循环调节占空比实现呼吸灯效果

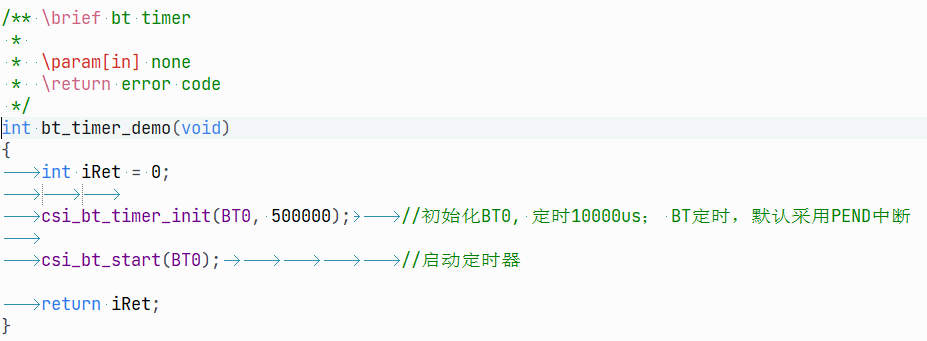

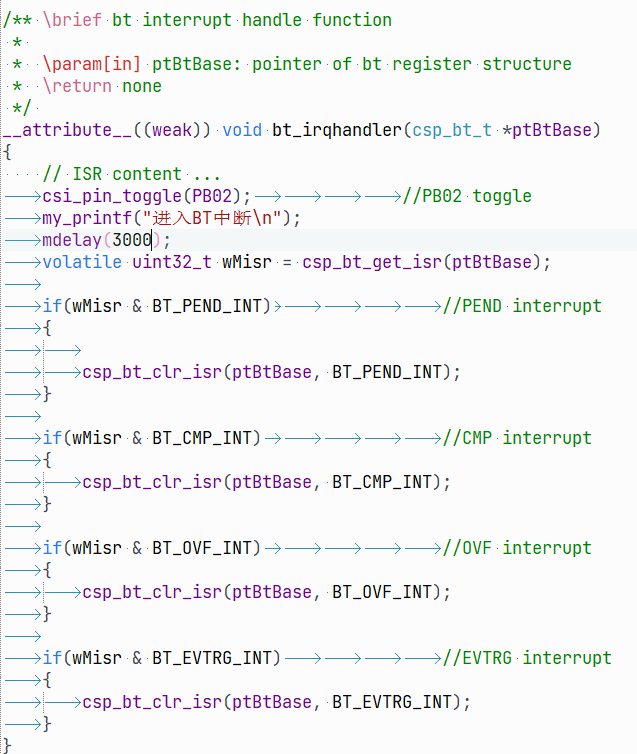

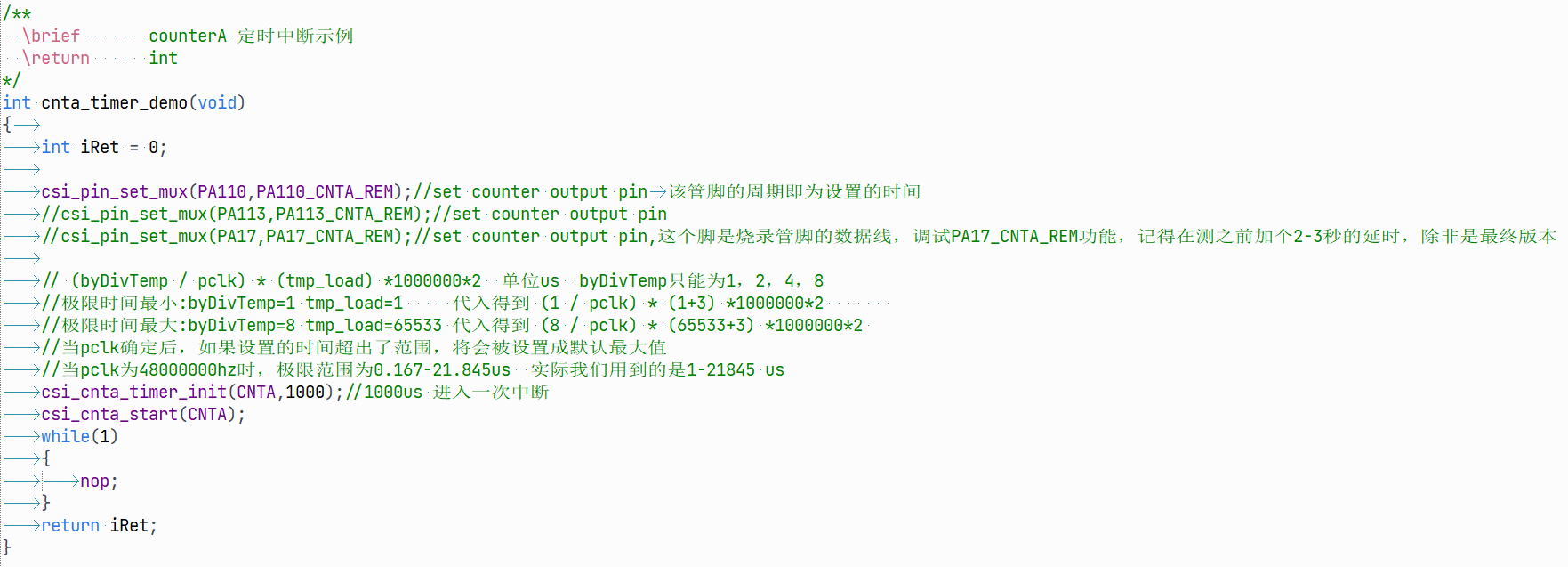

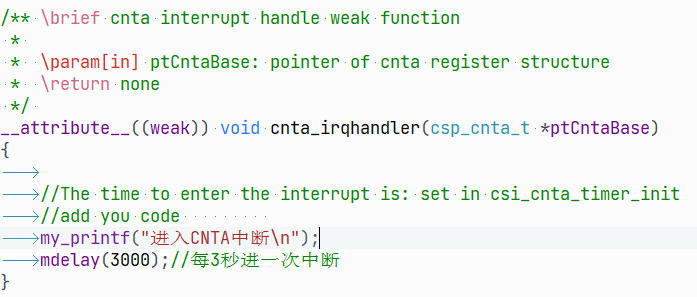

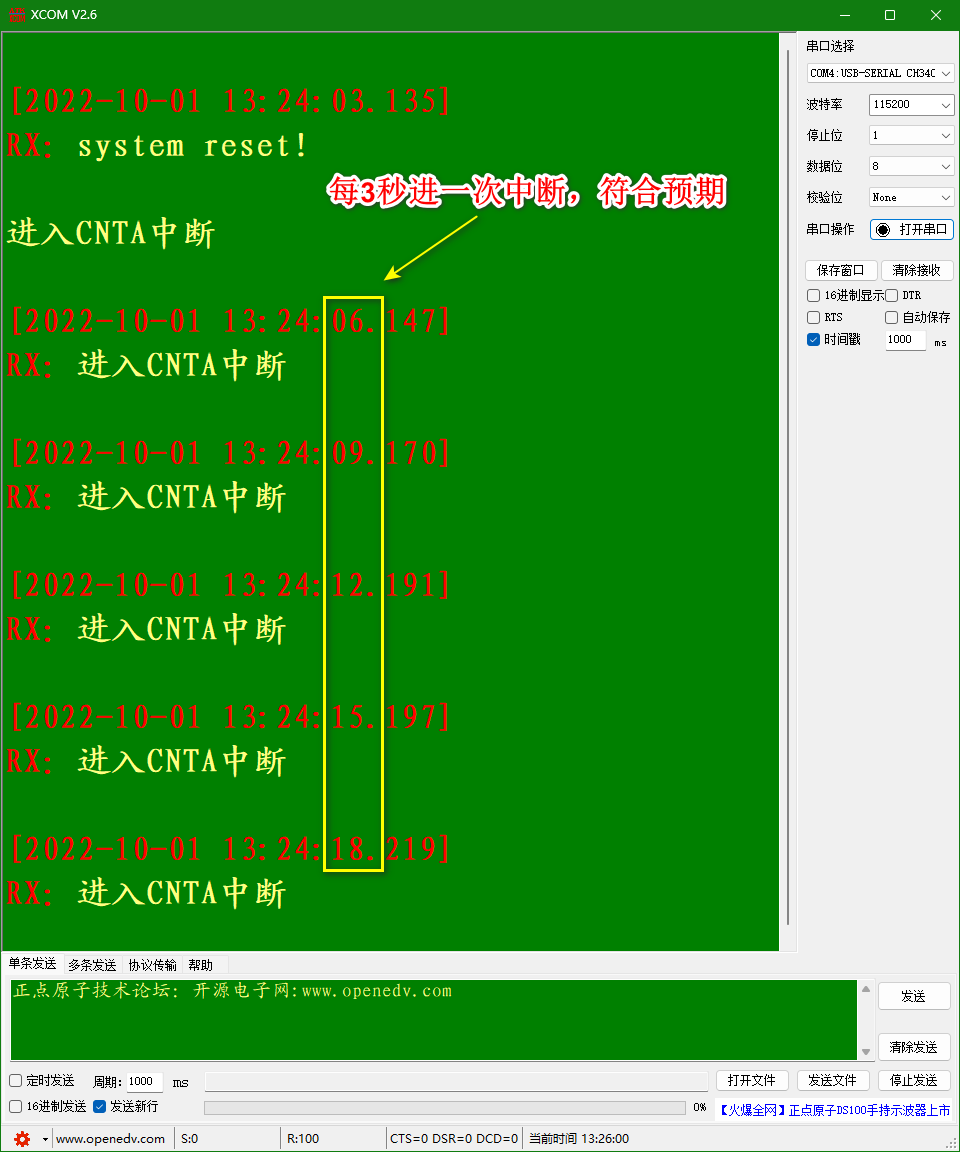

中断函数中每隔3秒串口输出“进入CNTA中断”

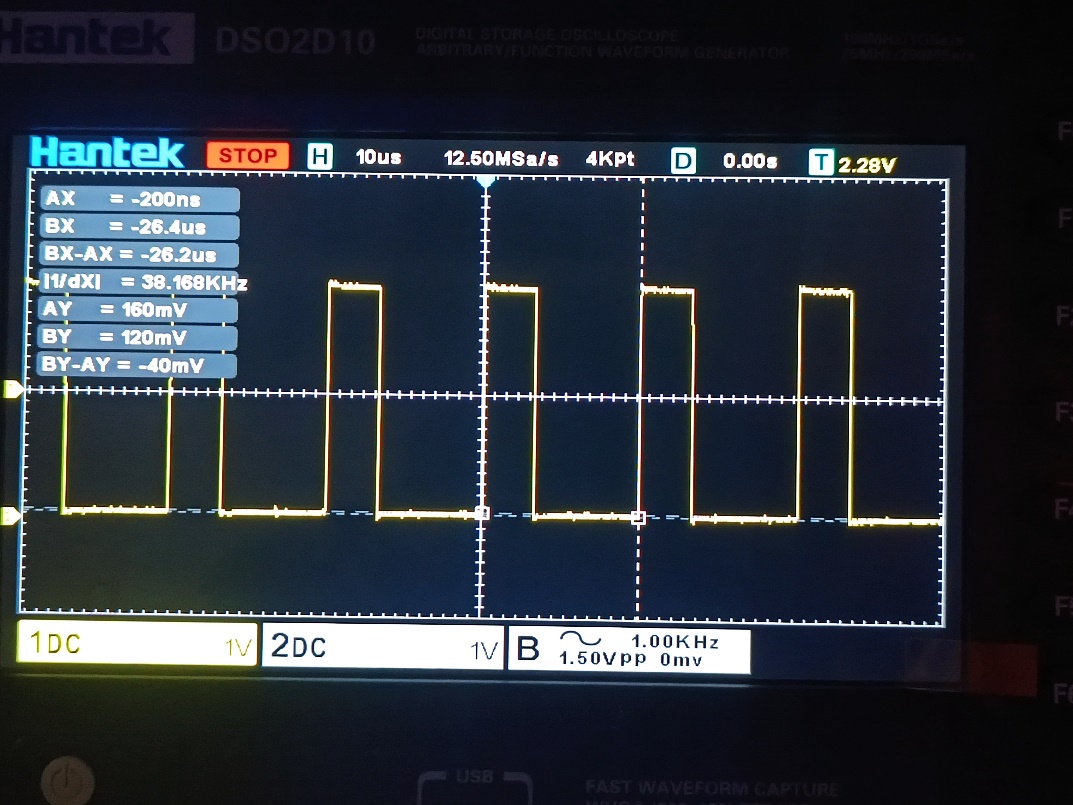

程序设计频率38KHz,占空比33%,实测频率为38.168KHz,占空比为38.168/116.279=32.82%,符合预期。

本期为定时器集合,学习了所有定时器外设并挑选其中的部分外设作简要调试测试。

根据实测效果来看,APT32F1104芯片定时器精度符合预期,代码封装较完善,实际只需小幅修改即可看到现象。