Microchip Technology Inc.

航空航天业务部高级产品营销工程师

Julian Di Matteo

在挑选现场可编程门阵列(FPGA)半导体产品时,卫星和航天器系统设计人员有几种不同的选择。一种是选择商用现货(COTS)组件,这种做法可降低组件单位成本,缩短交付时间,但可靠性通常不足,必须进行筛选(导致成本和工程资源增加),并且需要使用软硬三重模块冗余(TMR)来减轻空间辐射效应。对于要求不能出现故障的任务,设计人员通常会选择采用抗辐射设计(RHBD)技术的FPGA,虽然成本较高,但这类产品经过筛选和认证,符合合格制造商清单(QML)Q类和V类标准。QML V类是航天用半导体的最高认证标准。载人任务和安全关键型任务依靠QML-V组件降低故障风险。

提高性能、增强板上数据处理能力以及提供高速通信能力,这些航空领域的挑战性需求日益增加,设计人员必须设计出满足这些需求的系统。此类耐辐射RT FPGA以其制造商的航天经验和专业知识为后盾,依托通过QML V类测试的多个解决方案,提供了一种采用耐辐射设计的解决方案。本文重点介绍航天应用可以采用的不同FPGA技术以及组件的开发过程。

空间辐射效应

由于商用现货组件无法免疫各种空间辐射效应的影响,会导致集成电路性能下降或出现故障,因此需使用RT FPGA。

在各种辐射效应中,有一种称为总电离剂量(TID),它是由空间中的带电粒子和伽马射线引起的辐射所致。这种辐射可通过在材料中产生电离而积聚能量。电离会改变材料的电荷激发、电荷传输、键合和解离特性,从而对器件参数造成不利影响。TID是电子器件在指定时段(通常是任务时间)的电离辐射累加。损伤程度取决于辐射量,用辐射吸收剂量(RAD)表示。视TID辐射耐受性而定,器件可能会产生功能性或参数性故障。FPGA中受TID辐射影响的常见参数包括传输延时增加,这会降低器件性能。另一个故障机制是,在受到高TID辐射后,泄漏电流会增大。

另一类辐射效应是单粒子效应(SEE)。这是指瞬态翻转、瞬变或永久性损伤,因粒子(例如质子、重离子和α粒子等)辐射撞击到晶体管的敏感区域所致,会引发各种故障。SEE表现为包括单粒子翻转(SEU)在内的不同形式,在重离子、α粒子或质子等高能电离粒子照射电路或通过集成电路时产生,会导致系统逻辑中断。

同样令人棘手的是单粒子锁定(SEL),这是一种因单粒子诱导的高电流状态导致器件功能丧失的情况。SEL不一定具有破坏性。对于具有破坏性的锁定粒子,电流不会恢复到标称值。而对于不具有破坏性的锁定粒子,在FPGA上电循环后,高电平电流将恢复到标称值。

FPGA技术比较

FPGA有四种基本类型:

SRAM型FPGA

SRAM型FPGA使用静态存储器存储逻辑单元配置数据。SRAM具有易失性,掉电后器件配置会丢失。而上电时必须对FPGA进行编程。SRAM型技术的功耗往往更高,对辐射更敏感。

闪存型FPGA

可重新编程的闪存型FPGA主要使用闪存来存储配置。闪存技术不受SEU影响,因而不再受到FPGA配置存储器中辐射所致粒子翻转的威胁。与SRAM型FPGA的功耗相比,RTG4闪存型FPGA的功耗最多可减少50%。采用闪存技术不需要外部存储器、冗余或连续配置监视,从而在多个方面简化了设计。这种技术也无需使用散热器,因此可缩小设计尺寸并减小重量,而且有助于降低功耗,这对于电子模块通过太阳能电池板供电的情况尤为重要。

SONOS型FPGA

此类FPGA的一个示例是Microchip的RT PolarFire FPGA,其具备表征化辐射数据、低功耗以及不受SEU配置影响的辐射性能,并提供经过QML-V认证的高可靠性组件。这些FPGA在28纳米工艺节点上基于硅-氧化物-氮化物-氧化物-硅(SONOS)非易失性(NV)技术开发。已通过测量逆变器的传输延时对28纳米和较早的65纳米进行了技术对比。测试结果表明,在性能上,采用28纳米SONOS技术比采用65纳米闪存技术要高出2.5倍。这些SONOS型FPGA在提供低功耗解决方案的同时,还具备出色的抗辐射性能,并且不受SEU影响。SONOS型FPGA已通过QML-V认证,是需要进行高速信号处理的应用的理想之选。

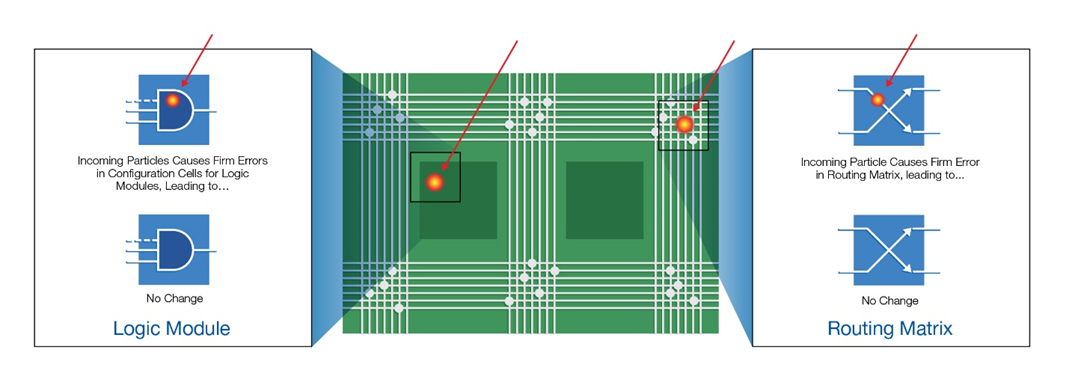

图1给出了闪存型FPGA和SONOS型FPGA为免受SEU影响而采用的架构。

Incoming Particles Causes Firm Errors in Configuration Cells for Logic Modules, Leading to... | 入射粒子导致逻辑模块的配置单元中出现固件错误,从而导致... |

No Change | 无变化 |

Logic Module | 逻辑模块 |

Incoming Particle Causes Firm Error in Routing Matrix, leading to... | 入射粒子导致路由矩阵中出现固件错误,从而导致... |

Routing Matrix | 路由矩阵 |

图1——闪存型FPGA和SONOS型FPGA的配置存储器不受SEU影响

反熔丝型FPGA

反熔丝型FPGA只可编程一次,与闪存型FPGA和SONOS型FPGA相比,关键的可重编程优势受到限制。反熔丝开始并不导电,但烧断后可以导电(其特性与熔丝相反)。反熔丝技术的抗辐射能力非常强。

如何开发RT FPGA

RT FPGA基于具备卓越辐射TID性能的多种制造工艺开发。这包括通过在电路级内置TMR的触发器实现的RHBD。如果尚未在芯片级实现TMR,则可以实现部署在软件中的TMR(称为软TMR)。芯片开发完成后,会对RT FPGA进行严格的认证。

要使器件达到最高标准,必须符合美国国防部发布的MIL-PRF-38535标准,这项标准为军用和航空集成电路确立了一致的认证、测试和可靠性标准。MIL-PRF-38535针对想加入美国国防后勤局(DLA)发布的QML中的制造商定义了一些要求。

产品开发的另一方面是表征SEE性能,在未改变芯片设计的情况下,它不随晶圆批次而变化。冻结设计后,FPGA制造商即可开始SEE表征过程。器件投产后,只要设计没有变化,并且组件已完全表征,就不需要进行额外的SEE性能测试。

一些工艺方法的TID性能可能会因晶圆批次而异,因此,必须在生产期间基于晶圆执行TID性能测试,以保证器件符合目标TID等级规格(25 krad、100 krad和300 krad)。

RT FPGA对航天器设计的影响

最新的RT FPGA具有诸多优势,为简化相关设计提供了丰富的选择,而且能显著提高板上数据处理能力。为满足这些需求,RT FPGA工艺节点在缩小以提高性能及加快信号处理速度,并提供更大的存储容量和更多DSP功能。此外,RT FPGA还提供其他一些关键优势,包括可重新编程,比ASIC的开发速度快等。通常,FPGA在升空后不会重新编程,但随着设计复杂性的提高,在系统设计人员遵循设计原则并对与在轨重新编程相关的成功率和风险进行审慎评估的前提下,可以选择重新编程。