Stephen Russell博士(TechInsights)与Peter Gammon教授(PGC)合作

罗姆今年发布了他们的第4代(Gen4)金氧半场效晶体管(MOSFET)产品。新系列包括额定电压为750 V(从650 V提升至750 V)和1200 V的金氧半场效晶体管,以及多个可用的TO247封装元件,其汽车级合格认证达56A/24mΩ。这一阵容表明罗姆将继续瞄准他们之前取得成功的车载充电器市场。

在产品发布声明中,罗姆声称其第4代产品“通过进一步改进原有的双沟槽结构,在不影响短路耐受时间的情况下,使单位面积导通电阻比传统产品降低40%。”他们还表示,“此外,显著降低寄生电容使得开关损耗比我们的上一代碳化硅金氧半场效晶体管降低50%成为可能”。

TechInsights仅用数周就迅速采购并剖析了罗姆第4代金氧半场效晶体管,并于2022年7月公布了首批图像。从那时起,PGC一直致力于提供相关器件的电气数据,这些数据与剖面图结合,有助于我们理解罗姆在沟槽工艺技术方面取得的进步。

届时,TechInsights订户将获得有关该设备的稳健性、可靠性和数据表范围外特性检测的全面分析。在本文中,我们将公开一些具有启发性的早期分析,以便验证罗姆的上述声明,并理解其所做的改进。

沟槽式金氧半场效晶体管基础知识

传统的“平面”金氧半场效晶体管的栅极和沟道区设置在半导体表面。平面金氧半场效晶体管易于制造且非常可靠。但在减小芯片尺寸以提高产量的过程中,其横向拓扑结构限制了最终缩小范围。

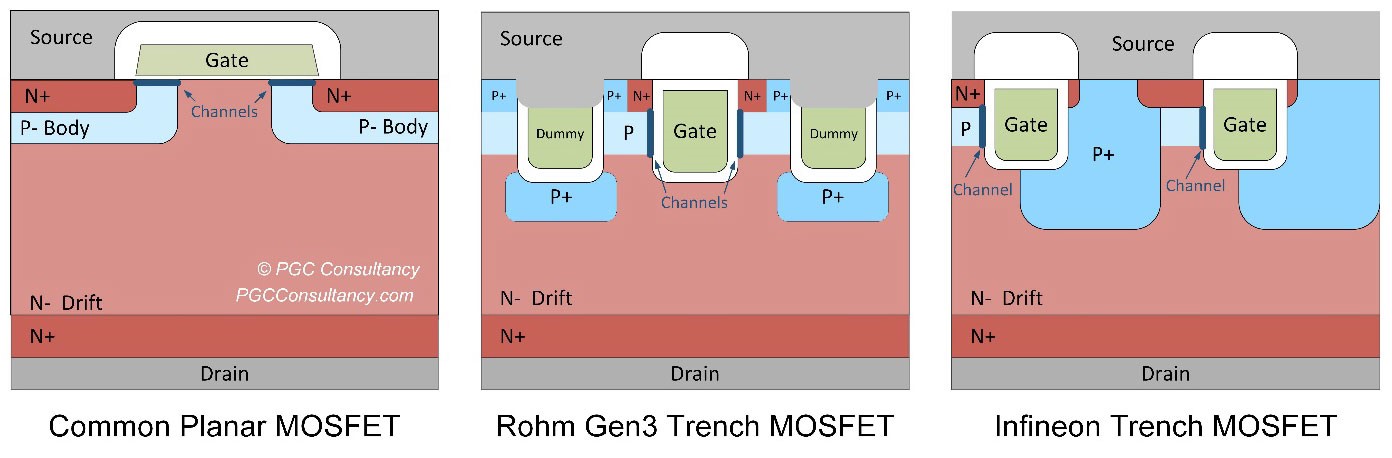

图1:碳化硅金氧半场效晶体管设计示意图,图中显示了罗姆(第3代)和英飞凌的典型平面结构和沟槽式设计。

沟槽式金氧半场效晶体管包括沟槽边缘形成并已被蚀刻在碳化硅表面的栅极。沟槽栅极用于制造低电阻器件,准确地说,是低比导通电阻(Ronsp,电阻x面积)。如能降低Ronsp,则芯片制造商能缩小芯片尺寸,从而实现RDSon=15 mOhm的产品,这能降低碳化硅用量,从而提高产量。

沟槽式金氧半场效晶体管的较低Ronsp背后有多种原因。首先,在碳化硅沟槽侧壁上制备的栅极具有更高的沟道迁移率,这意味着与平面器件相比,电子穿过沟槽栅极的阻碍较少。这能降低沟道电阻。其次,沟槽式金氧半场效晶体管可能消除平面金氧半场效晶体管的JFET电阻,在该区域中,来自两个沟道的电流被挤压到p体触点之间的狭窄通道中。但正如我们将看到的那样,实用、务实的设计可能导致再次引入一个类似JFET的区域。第三,与平面栅极的数量相比,垂直沟槽栅极密度应当更大,从而减小单元间距并增大电流密度。

但要小心其中的陷阱。沟槽式金氧半场效晶体管可能难以优化以实现可靠、稳健的运行。特别地,成功的设计必须解决在尽量增大器件顶部碳化硅高电场(比硅高9倍)的同时保护同样位于器件顶部的精密栅极氧化物免受该电场影响的问题。维持这种平衡需要巧妙但复杂的器件布局,否则漂移区需要严重降额,从而侵蚀沟槽架构的增益。因此,沟槽式金氧半场效晶体管的一个缺点是它们的设计更复杂,通常需要更多的制造步骤,其中一些步骤可能具有特殊的复杂性——深度高能注入(英飞凌)或深沟槽蚀刻(罗姆第4代器件)。

罗姆和英飞凌的沟槽设计

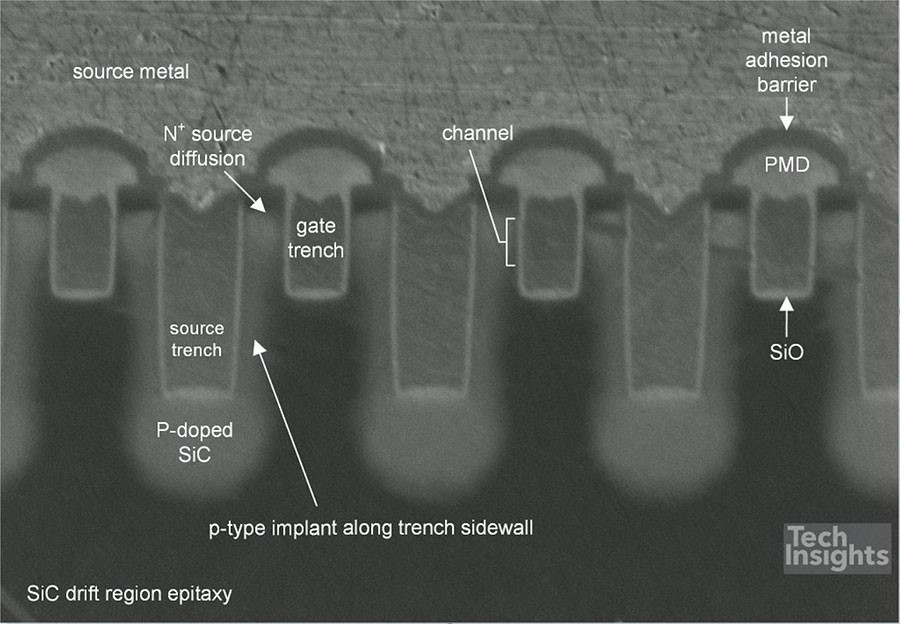

罗姆和英飞凌率先转向沟槽式金氧半场效晶体管,但采用了截然不同的设计。罗姆第3代的TechInsights剖面图如图2所示,以及图1中的卡通形式。罗姆选择了更传统的设计,即每个栅极沟槽的每侧都有沟道,并利用每一侧的虚拟沟槽,其中,通过深P型注入保护栅极沟槽。英飞凌让每条沟槽都物尽其用!每条沟槽的一侧均有一条沟道,另一侧被深P+注入所覆盖,以防高电场影响栅极氧化物。这种布局使沟槽的沟道侧与4°离轴碳化硅晶体完美对齐;这是一种降低电阻的巧妙技巧。

图3中值得注意的是,每个有源栅极沟槽之间的两个非有源源极沟槽,它们与宽体电极触点一同形成了沟槽器件的宽单元间距。但从平面图中看到该设备时,这个明显浪费芯片面积的布局有其存在的意义。不同于传统的仅在一个维度上跨越器件的栅极条,这款第3代器件的布局具有从上到下和从左到右延伸的栅极,从而创建了一个巧妙的二维栅极网格,使单位面积内的栅极密度几乎翻倍。这在概念上类似于Wolfspeed的六边形布局,该布局将栅极密度增加了约1.3倍。

然而,在罗姆最新的第4代产品发布前,这两款沟槽器件均无法拥有低于一流平面双扩散型场效应晶体管的Ronsp。第3代设计的另一个问题在于,源极沟槽能为栅极提供多少保护,使其免受高电场的影响?

图2:罗姆的第3代碳化硅金氧半场效晶体管(来源:TechInsights)

罗姆的第4代碳化硅金氧半场效晶体管

在TechInsights快速采购并剖析了罗姆的新型第4代碳化硅金氧半场效晶体管后,下图显示了TechInsights为新型第4代器件制作的高分辨率电镜图。

图3:罗姆的新型第4代碳化硅金氧半场效晶体管(来源:TechInsights)

第4代器件与第3代器件有部分相似之处,也有一些明显差异。

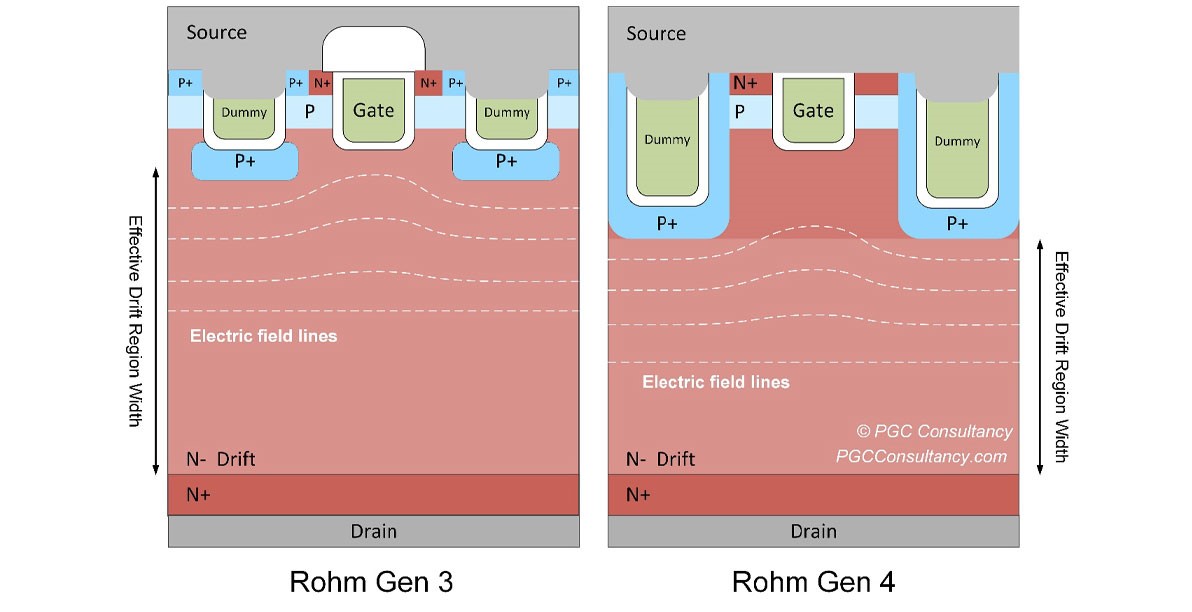

相似之处在于罗姆采用传统的沟槽式金氧半场效晶体管设计方法,在栅极沟槽的两个侧壁上均有沟道。然而,现在每个栅极沟槽的两侧均有一个接地的源极沟槽,它延伸至漂移区的深度为第3代的两倍。正如我们所解释的那样,这是关键的设计特征,罗姆巧妙地利用它来更好地保护栅极氧化物和降低电阻。

每个栅极沟槽的单个虚拟/源极沟槽使单元间距能减小3倍。这标志着罗姆在第3代中使用的新型单元布局的终结,但这种布局几乎使栅极密度增加了一倍,有利于传统的一维条形布局。总之,这代表每单位面积的栅极沟槽密度净增加50%(至少),这有助于进一步降低困扰其他器件的沟道电阻问题,在我们之前展示的650V平面金氧半场效晶体管串联电阻中,该电阻可能会贡献达30%。

电阻的另一主要贡献者为衬底电阻,也在这一代器件中首次被减薄,从而大大减少了该元件电阻。

审查罗姆对其第4代器件的声明

使用PGC提供的各式最先进的电气表征设备,结合Techinsights的分析,我们审查了罗姆对这些器件的多项声明。我们直接比较了新型第4代650V罗姆金氧半场效晶体管、第3代金氧半场效晶体管和一流的平面碳化硅金氧半场效晶体管,它们具有相似的Rdson额定值。

首先是损耗。罗姆在图中的第一项声明为,他们将导通损耗降低了40%,从而实现了等效的芯片尺寸缩减。事实上,根据TechInsights公布的剖面图,我们可以确认芯片有源区域的比导通电阻(Ron×A)几乎比上一代产品低40%,尽管实际上器件的必要非有源区域会略微降低这一增益。更进一步而言,新的Ronsp也比我们描述的一流平面器件小20%。正如我们之前所讨论的那样,这是一个至关重要的进步,因为它能缩小芯片尺寸,从而提高产量并降低成本。

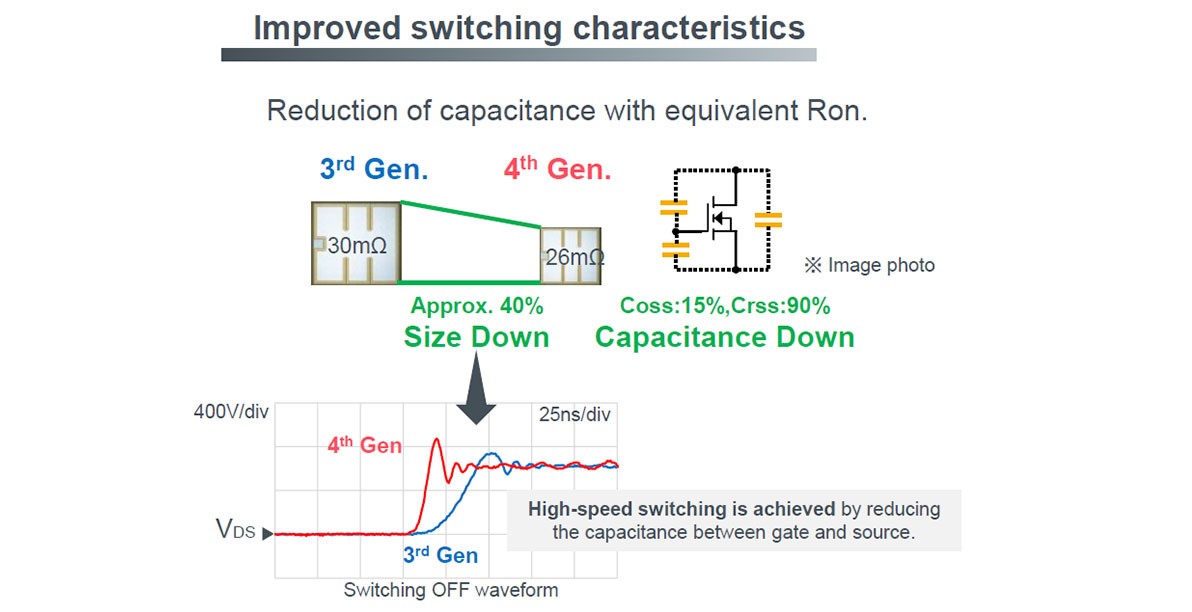

图4:罗姆的第4代器件具有更低的Ronsp、Coss和Crss(来源:罗姆)

图中的第二个声明为,因为各个密勒电容的降低,所以开关损耗将会降低。事实上,虽然我们比较的芯片的测试结果与之并不完全匹配,但我们可以确认Crss(在额定电压下)降低了约90%,而且Coss也有所降低,具体取决于电压。我们正在开展自己的开关基准测试。

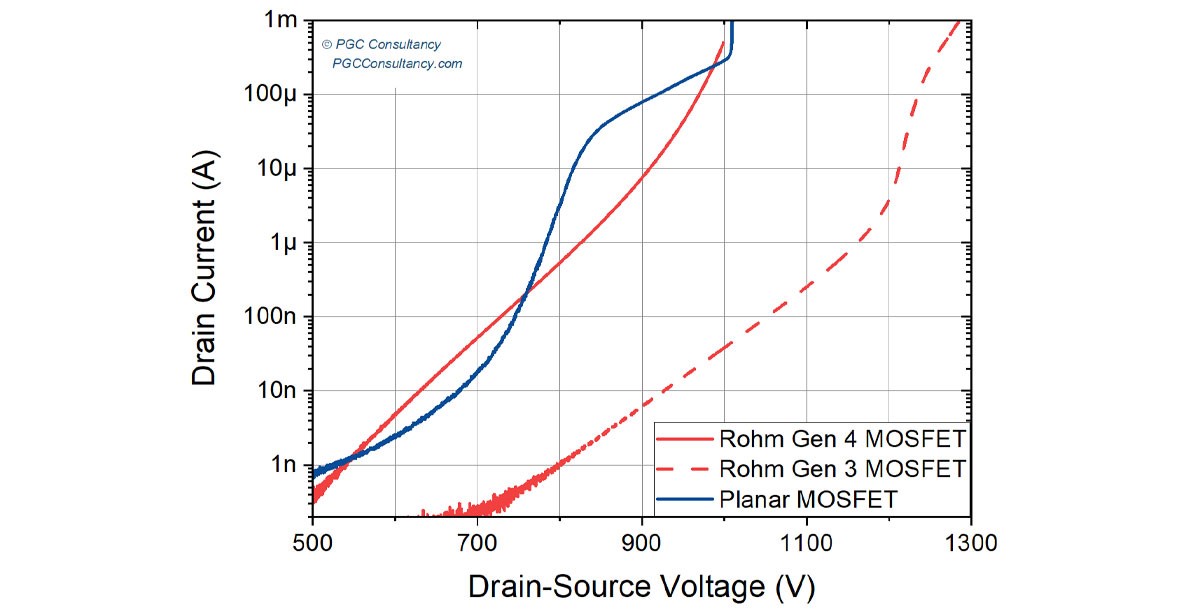

罗姆提出的一项声明涉及将额定电压范围从650 V提高至750 V。罗姆表示:“750 V击穿电压可确保设计裕度不受VDS浪涌影响”。我们发现这是一个正在席卷整个行业的有趣发展。然而,实际上,在静态条件下测试的新型第4代器件的实际击穿电压约为1000 V,实际低于在超过1200 V时击穿的第3代器件。新型第4代器件与一流的平面器件不相上下。结合他们关于裕度的说法和实际数据,这的确令人印象深刻。他们允许以75%的实际击穿电压下使用该器件,该数据高于第3代的50%以上,这表明第4代的可靠性大幅提高。正如我们将在下一节中解释的那样,这种降额的减少是一个很大的改进,可以在一定程度上降低电阻。

图5:尽管额定击穿电压有所增加,但测得的真实击穿电压显示第4代要小于第3代。这表明漂移区降额显著降低。

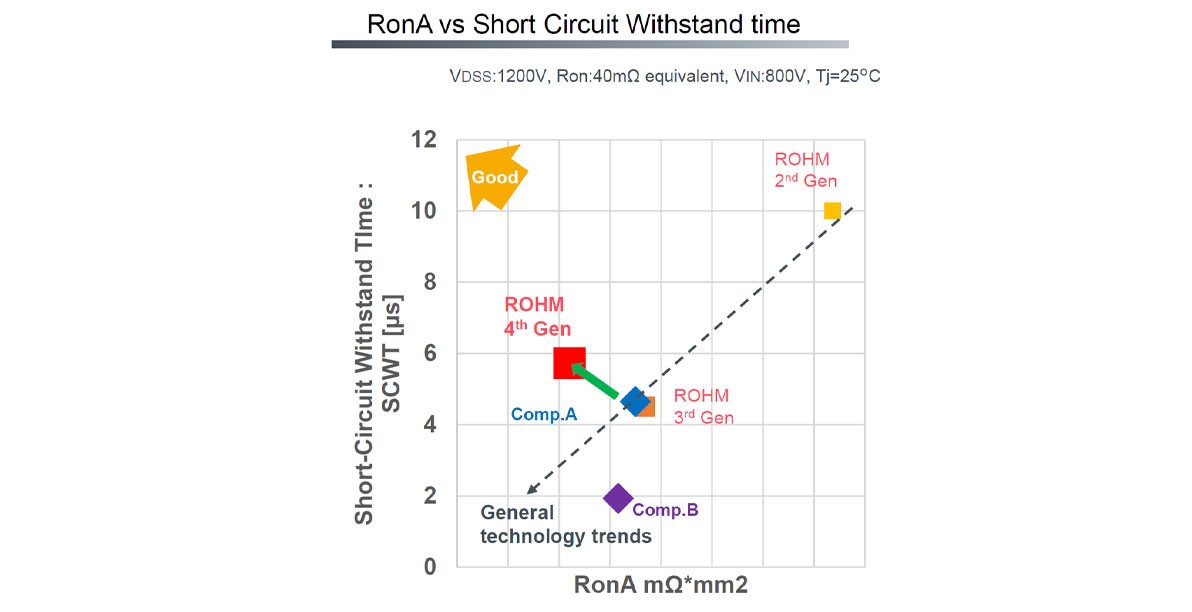

PGC实验室将很快对第4代器件开展短路测试,但罗姆的第三个有趣的说法是,尽管缩减了芯片尺寸并增大了电流密度,但实质增加了器件的短路耐受时间。如果他们所言不虚,考虑到降额减少,这进一步证明罗姆在其器件可靠性和稳健性方面迈出了一大步。

图6:据称罗姆的第4代器件增加了短路耐受时间,同时降低了Ronsp(来源:罗姆)

总之,罗姆第4代器件的强劲表现有力回应了对早期碳化硅沟槽器件的诸多批评。但这一切究竟如何实现?

第101条规则:保护栅极氧化层

下图为PGC对新型第4代设计的图解复制。图中并未考虑缩减间距,而是强调了栅极周围的变化。

图7:PGC展示的新型第4代罗姆器件,其中电场线展示如何保护栅极氧化层。

关于金氧半场效晶体管设计,尤其是碳化硅沟槽式金氧半场效晶体管的设计,主要用于在器件处于关断状态时保护栅极氧化层,阻断大电压。器件表面此时存在高电场,如果与栅极氧化层重合,会引起栅极泄漏并导致可靠性问题。在第3代器件中,源极沟槽与栅极沟槽深度相同,因而其下方的P+注入仅比栅极沟槽本身深一点。因此,图中所示的电场线(可以想象为正在膨胀的气球的外缘)围绕沟槽拐角弯曲,并能更轻易地与栅极沟槽的底部相互作用。

相反,罗姆的新型第4代器件的源极沟槽被注入到源极沟槽侧壁和底部的P+区域包围,位置更深。这将保护栅极的p-n结向下推入漂移区,远离其保护的栅极氧化物。如第4代器件图所示,峰值电场线(气球的外缘)远离栅极氧化物。

栅极保护的收益

栅极获得了更好的保护,那又怎样?好吧,假如没有采取相对的栅极保护措施,如第3代器件,则需要采取措施来确保电场永远不会达到足以损坏栅极的数值。因此,支持阻断电压的漂移区被过度设计(实际已降额,参见关于该主题的我的文章),以支持超过应用所需的电压。试着回想一下,可用于400 V电动汽车的650 V第3代器件的击穿电压超过了1200 V。虽然这确保能长期安全运行,但代价是漂移区的电阻随着它能支持的电压呈指数上升(Rdr∝ V^2.28).

因此,通过更好地保护栅极,第4代器件需要的降额更少。我们测量的击穿电压为1000 V,比第3代降低了20%以上,因此漂移区电阻可能降低了40%以上。这似乎在TechInsights提供的剖面图中得到证实,新器件具有类似的漂移区宽度,尽管图7所示的深沟槽使其进一步变薄。此外,我们预计漂移区的掺杂将增加,从而进一步降低电阻。

有效的栅极氧化物保护也能提高可靠性。具体而言,这将解释为何罗姆建议的栅极氧化层短路耐受时间从最小值4.5 µs增加到5.5 µs。在短路故障期间,支持最高电场的器件区域通常会达到最高温度。如果该位置离栅极更远,则栅极烧坏的时间将随之增加。

另一个巧妙的技巧:是时候往碳化硅超结结构前进?

学术界对碳化硅超结结构的探讨已持续了十年或更长时间,最近一次由我的研究小组提出。我们利用7 µm深的沟槽,并在其侧壁上注入P,从而提出了一种1700 V碳化硅超结器件。

罗姆的器件不是超结结构器件,它们的p型内衬沟槽只占我们提出的器件的一小部分,但我们怀疑超结结构原理能在栅极沟槽下方的区域起作用。毕竟挤压在两个P柱之间的狭窄的n掺杂区会显著增加器件的JFET电阻。但我们怀疑该区域中的n型掺杂区将高于漂移区,利用超结结构的电荷平衡原理(下次讲解)在不破坏电场阻断能力的情况下增加掺杂。

要点和结论

公平地说,这个设计让我们感到非常兴奋;它似乎是一种发挥碳化硅潜力的沟槽式碳化硅设计。根据该设计,我们得知罗姆已经找到了一种方法,利用其深沟槽设计来同时:

将单元间距减少三倍,显著降低了沟道电阻;

保护栅极氧化物,提高可靠性,减少漂移区降额,从而降低其电阻;

大幅降低衬底电阻;

引入JFET区(负面影响),但可能通过超结结构/电荷平衡原理降低其影响。

虽然目前只有英飞凌和罗姆的沟槽器件可用,但博世(Bosch)紧随其后,而且其他集成器件制造商也可能效仿,以获取潜在的产量和成本优势。该技术的实效将通过普及率得到验证。我们或许可以期待更多的电动汽车原始设备制造商和一级供应商在其车载充电器中采用该技术,甚至可能在以平面器件为主的动力传动系统逆变器中采用该技术。

Peter Gammon教授在碳化硅电力电子器件的设计、制造和测试方面拥有15年的工作经验。他不仅是PGC的创始人,还是华威大学的电力电子器件专业教授。他领导了额定电压从1200 V到15 kV不等的定制功率器件(绝缘栅双极型晶体管、金氧半场效晶体管和二极管)研发项目,涉及电动汽车、航天、工业机械和电网。他已发表了80多篇论文和3项专利,其工作成果已广泛应用于整个碳化硅行业。

TechInsights以支持促进创新的公平市场为荣,该市场能创造电子知识产权并实现货币化,以推动现实世界发展。我们致力于引领全球微电子逆向工程,并打造半导体行业内容平台。

Stephen Russell博士在宽禁带(WBG)器件制造和表征方面有超过15年的从业经验。他于2013年获得格拉斯哥大学电子工程博士学位,专业研究金刚石场效应晶体管,之后前往华威大学研发3.3 kV和10 kV碳化硅器件。他凭借论文《碳化硅功率金刚石场效应晶体管的高温电老化和热老化性能及应用注意事项》赢得《电气与电子工程师协会汇刊电力电子学卷》2018年最佳论文奖。自2018年进入业界以来,他领导了新型硅绝缘栅双极型晶体管产品线研发,并发起了一个在电路保护应用中使用碳化硅JFET的研发项目。他于2020年加入TechInsights并成为功率半导体器件的学科专家,同时持续了解整个行业的最新发展。

关于TechInsights

TechInsights是全球领先的先进技术分析和知识产权服务提供商。三十年来,我们一直致力于支持一个公平的市场,让半导体和电子知识产权实现创新并达成变现。我们为超过200家的全球半导体、微电子以及全球科技巨头提供最值得信赖的技术分析和解决方案,帮助客户做出最明智的技术和投资决策。近日,我们收购了一批专业的行业机构,为半导体行业提供技术进展、成本和市场动态方面的信息。

TechInsights成立于1989年,总部位于加拿大渥太华,拥有320多名员工,并在世界多地设立了分支机构。TechInsights为客户提供先进的逆向工程服务。我们拥有全球领先的实验室、先进的工具和设备,能够在逻辑、图像传感器、物联网连接SoC、移动RF创新、存储和电源半导体方面进行深入的,世界级的分析。

欢迎访问TechInsights官网:https://www.techinsights.com/,了解更多技术趋势和市场洞察。