超低功耗嵌入式存储器专家 SureCore 宣布,由英国创新署 (IUK) 资助的 "开发 CryoCMOS 以实现下一代可扩展量子计算机 "项目的下一个关键部分已成功完成。该芯片将验证项目中开发的低温 SPICE 模型和 IP,这些模型和 IP 将用于控制和测量 ASIC,与量子比特一起放置在低温恒温器中。 将控制电子设备从低温恒温器外部移到内部是减少延迟和布线的需要,但这意味着电子设备必须在前所未有的低温(低至 4 开尔文)下运行,而这正是该项目的目的所在。

sureCore 首席执行官保罗-威尔斯(Paul Wells)说:"这是联盟成员团队合作的结晶,他们都为这一控制芯片设计做出了宝贵贡献。他们的低温 IP 已被 Agile Analog 一个非常有能力的物理设计团队成功集成。

Agile Analog 首席执行官 Barry Paterson 补充说:"我们很高兴能参与这个项目,并获得在极具挑战性的低温条件下硅性能方面的经验和知识。这些经验将有助于未来量子领域的 IP 开发。

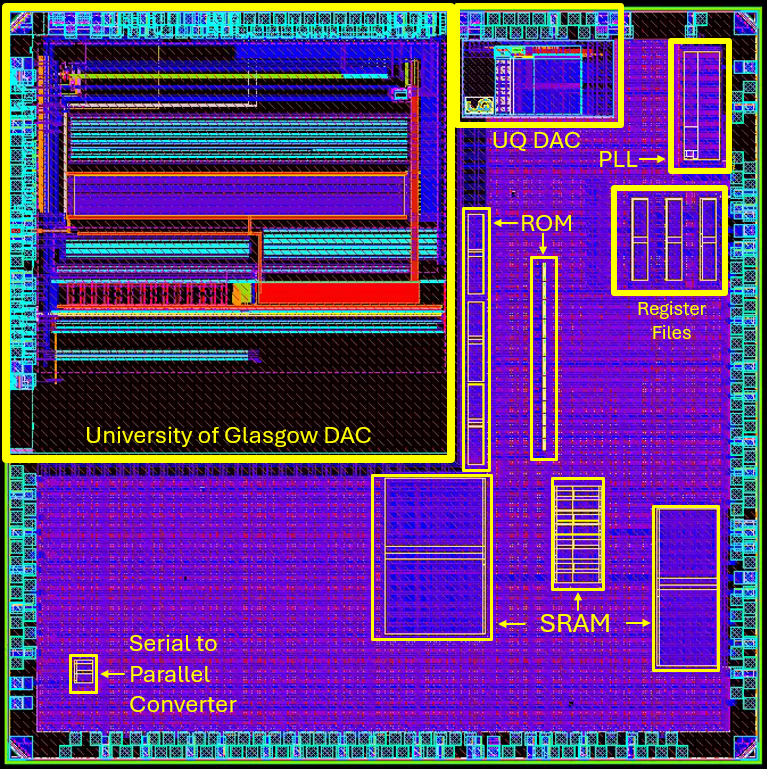

图中显示了各种 IP 块。其中包括格拉斯哥大学的 DAC、Universal Quantum 的 DAC 以及 sureCore 的 PLL、ROM 块、寄存器文件块和 SRAM 块。其余紫色区域主要是控制逻辑。

威尔斯补充说:"这是一个很好的例子,说明英国创新署如何将专家团队聚集在一起,创造出其他方式无法实现的创新。该项目将使英国不仅成为量子计算的卓越中心,而且成为低温晶体管建模以及低温 IP 和芯片设计的卓越中心。通过作为一个重点突出的专家团队开展工作,该项目得以及时、高效地成功实现关键的里程碑和最后期限。如果没有英国创新署的支持,这一切是不可能实现的。

项目背景

sureCore 利用其最先进的超低功耗存储器设计技术,创建了嵌入式静态随机存取存储器 (SRAM),这是任何数字子系统的基本构件,能够在 77K (-196°C) 低至量子计算机 (QC) 所需的接近绝对零度的温度下工作。此外,标准单元和 IO 单元库都针对低温下的运行进行了重新表征,从而使行业标准的 RTL 到 GDSII 物理设计流程得以轻松采用。

QC 扩展的一个关键障碍是能否将日益复杂的控制电子元件安装在必须在低温条件下置于低温恒温器中的量子比特附近。在此过程中,必须尽可能降低控制芯片的功耗,以确保将多余的热量控制在最低水平,从而避免对低温恒温器造成额外的热负荷。在这方面,sureCore 的低功耗设计专业技术证明是至关重要的。

目前的 QC 设计将控制电子元件安装在低温恒温器外,因为现代半导体技术只能在低至 -40°C 的温度下工作。当温度降低到接近绝对零度时,晶体管的工作特性会发生明显变化。在过去的几个月中,对这种行为变化的测量、理解和建模展示了制造能够在低温条件下控制和监测量子比特的接口芯片的潜力。

目前,连接室温控制电子元件和低温恒温器中的量子比特的是昂贵而笨重的电缆。使 QC 开发人员能够利用无晶圆厂设计模式,创建自己的定制低温控制 SoC,并将其与低温恒温器内的量子比特放在一起,这将改变游戏规则,迅速实现 QC 扩展。其直接优势包括成本、尺寸以及最重要的减少延迟。下一步将在低温条件下对演示芯片进行表征,以进一步完善和验证模型,帮助提高性能。

IUK资助的联盟是一个完整的生态系统,由具备开发低温耐受半导体IP所需的专业知识和核心能力的公司组成。该项目的目标是开发和验证一套基础 IP,并将其授权给设计人员,使他们能够创建自己的 Cryo-CMOS SoC 解决方案。这样,他们在量子计算领域的竞争优势将大大加快。

sureCore www.sure-cor