作者:Philipp Jacobsohn,SmartDV高级应用工程师

中国已经连续十多年成为全球第一大汽车产销国,智能化也成为了汽车行业发展的一个重要方向,同时越来越多的制造商正在考虑进入无人机和飞行汽车等低空设备,而所有的这些系统产品都需要先进芯片的支撑,其中的许多芯片因其功能都是安全关键型芯片(safety-critical chip)。

所有类型的安全关键型芯片设计都需要深谋远虑和认真规划。本文的目的是阐明在安全关键型应用中使用预先打造的电路功能(也就是IP内核)的益处,并为您在设计芯片时,在做出相关选择和IP内核集成过程中提供一些指导。

遗憾的是,设计师往往低估了在其项目的早期阶段与第三方IP制造商合作的重要性和益处。缺乏与IP供应商之间有计划的密切合作可能会导致误解、时间压力、流片延迟和挫败感。当然,您肯定希望在您的芯片设计项目中避免所有这些问题——那我们就接着往下看。

什么是安全标准?

在我们深入研究安全关键型芯片设计的IP选型之前,让我们先快速了解一下不同的行业针对安全性形成的标准。

适用于汽车行业的标准是ISO 26262,它源自IEC 61508标准。《航空器机载电子设备硬件设计保障指南(DO-254)和AMC 20-152A(基本上是DO-254的补充)是为开发航空机载电子设备硬件的工程师提出要求的通用标准。其他最终用途和设计应用都可能有其自己的专用标准。ISO 21434网络安全标准就是一个例子,它在当今的汽车和航空电子设计中扮演着越来越重要的角色。(出于本文的目的,我将把重点放在安全性上,而不是安全防护。)

我们为什么需要安全标准?以及它们为什么会有这么多不同之处?

接下来我们讨论一下为什么在开发电路的时候需要标准化的问题。坦率地说,这个话题并不新鲜,甚至也不令人兴奋!安全标准甚至经常被视为一种必要的挑战——但是,如果没有明确定义的可靠性和操作安全性规则,电子电路的运行将不再可能。

与航空公司飞行员在起飞前必须通过飞机所有安全相关的标准协议类似,标准化也必须作为电路开发的一部分加以推进。即使飞行员已经经历了数百次相同的过程,并且成功完成了相应数量的飞行,在每次重新起飞之前也必须重新进行该程序;这一措施的唯一目标是避免错误。

同理,这正是ISO 26262和IEC 61508等预定义的标准所希望达到的目的:一个明确定义的计划,有助于发现可能的错误并对问题进行分类,从而使设计能够对不可预见的情况做出充分的反应。如果轮胎损坏,必须阻止飞机起飞,因为它将无法安全着陆。然而,如果机上厨房有缺陷,这对于飞行来说可能是可以接受的,因为它不会对飞机的航空机械性能产生不利影响。

从根本上说,轮船船长和飞行员的目标是完全相同的:即将乘客和货物安全地运送到预定的目的地。由于海上和空中旅行之间的巨大差异,对这些任务就有不同的标准。正是由于这个原因,所以才制定了专门的安全标准。为这些不同运输工具提供设备的任何供应商必须事先知道,例如,他们的陀螺罗盘将要被安装在飞机上还是安装在游船上,以确保其正常工作。这也是IP供应商需要了解将使用其预定义电路功能(IP)的应用环境的原因。

安全标准定义了哪些方面?

安全标准定义了设计过程安全需求的各个阶段:计划(planning)、实施(implementation)、验证(verification)和文档记录(documentation)。

对于所有标准,该程序都有或多或少的统一性,但应该注意的是,每个标准对这四个阶段的适用性要求的定义还是略有不同。必须满足每个步骤的原则,从而符合相关标准。

最终用途和允许的故障概率

为了定义恰当的错误处理机制,就必须对潜在的硬件故障进行分类。就像前面提到的飞机轮胎和厨房的场景一样:汽车信息娱乐系统中的一个错误可能是可以接受的,而影响安全装置的错误则是不可接受的,例如自动制动系统。

因此,需要依次对不同的要求进行分类。例如,IEC 61508标准就被细分为五个安全完整性等级:SIL 0到SIL 4。ISO 26262标准包括四个等级:ASIL A到ASIL D(其中ASIL代表汽车安全完整性级别)。类别级别越高,安全要求越严格,其中SIL 4或ASIL D是最严格的。

在确定设计和验证中必须采用的方法时,产品的最终用途在其中起着至关重要的作用。例如,进入汽车信息娱乐系统的芯片,如果发生故障就会给驾驶员带来麻烦,但不会对人的生命构成任何风险。相比之下,安全气囊或车道管理系统中的芯片故障可能会威胁到驾驶员、乘客、道路上其他车辆甚至行人的安全。

当一种芯片设计的最终用途可能意味着人类的生命会受到威胁时,我们将其称为安全关键型芯片。功能安全在这种设计中是必不可少的:因此,这类设计的完整性级别必须与最终用途相称。必须对软件或硬件引起的潜在故障制定计划并主动解决。

对故障的理解和反应

让我们进一步了解如何理解和应对潜在的故障。从根本上来说,这都是关于系统如何处理故障情况,并确定:1)如何预防故障本身发生,或2)如何应对故障。这里必须区分硬件错误和软件错误,它们要么可以被安全地忽略,要么必须通过不同的方法加以预防或应对。即使是纯粹的硬件错误,也必须了解这些错误实际上会导致什么故障,以及适当的应对措施应该是什么样子。

需要对系统性误差(例如,由电路开发或不充分验证导致的)和随机发生的错误(由外部影响引起)之间进行区分。重要的是要明白,在任何情况下都不可能避免系统性错误。通过良好的验证覆盖、标准化的测试过程、广泛的测试,其中也可能通过使用专用的验证IP(VIP)以及使用专门的工具,有可能显著提升开发无错误产品的可能性。

正如相应的安全标准明确强调的那样,100%的覆盖率在实际中是不可能实现的。对于所谓的极端情况尤其如此,这种情况描述了元器件在异常条件下的操作,并且在电路开发和相关验证中都是一种挑战。

另一方面,也不能完全排除随机错误。在这里,有必要制定对此类错误做出适当反应的策略。为了消除由外部影响(如α因子)引起的潜在故障,必须采用错误检测和校正电路。根据应用领域和无错误操作要求的级别,有必要提供容错实现。容错在发生错误会危及人类生命的情况下尤其重要,比如飞机上的设备。

原则上来说,这样的要求需要大大增加实现的工作量,当然也需要增加验证的工作量。在这个领域,有必要强调的是,芯片设计人员必须要验证电路本身的正确性,还要验证错误检测和纠正电路的正确性。

IP开发是如何受到影响的?

当为安全关键型设计创建或使用IP时,工程师必须要牢记什么?

即使只对最终产品进行认证,但其中每个组件也必须满足适用于整个系统的要求。因此,所有子组件都必须按照严格的规则来执行电路实现要求,以考虑产品在安全性相关应用中的后续使用,并遵守适用标准的开发流程。

就ISO 26262标准而言,设计流程要求包括:

详细的规划——在定义功能安全要求阶段中必须仔细完成

分析——旨在识别危险和可能的错误模式

实施——即对前面两个步骤进行全面的考量

然后,必须对系统进行验证和确认。为了获得认证,所有细分步骤都必须有良好的证明文件,并记录其结果。同时,这个记录必须包括所使用的工具和采用的验证方法等等。

为了获得DO-254认证,必须在规范制定阶段首先就要强制性地使用明确的定义和术语,以确保从一开始就有完全可追溯性,并指出精确的要求,以确保详细的证明文件。

要获得这种类型的认证需要付出很大的努力!还必须承担额外的任务来创建适当的证明文件,如记录验证过程、错误覆盖、错误报告和工具使用等必需环节。还应该注意的是,只有某种产品在获得认证后保持不变的“冻结”版本才是认证合格的。此外,在创建产品时所使用工具的版本也必须保持不变。

获得行业标准机构认证

为了确保符合DO-254或ISO 26262等安全标准,就有必要获得相应的认证。公司必须与独立的组织合作,例如德国的TÜV SÜD等机构,以完成认证过程。全球有许多这样的认证机构。

那么,你应该追求认证吗?这需要视情况而定。

不利的一面是,获得安全标准认证的整个过程非常耗时,而且还需要适当培训人员。还需要在整个认证期间接受认证组织的审核,以检查和证明实现功能安全的措施的完整性。

有利的一面是,认证可以增加客户对其所需的产品质量和可靠性的信任。此外,由于投入了额外的时间和精力,在整个设计过程中对细节的严格关注可以开发出优质的产品。

在大多数情况下,认证IP核这样的单个子组件是没有意义的,因为它们会被用于更复杂的电路中。但是,所有子组件都必须符合适用标准规定的严格规则,并考虑到产品在安全相关应用中的后续使用。

最终考量因素

如前所述,获得认证并不容易,但值得一试。即使只对最终产品进行认证,但包括第三方IP核在内的每个组件都必须满足适用于整个系统的要求。因此,所有子组件都有必要按照适用标准的严格规则进行电路实现,并在开发阶段就为产品的安全关键型最终用途制定规划。前面提到的标准定义流程必须从始至终贯彻。

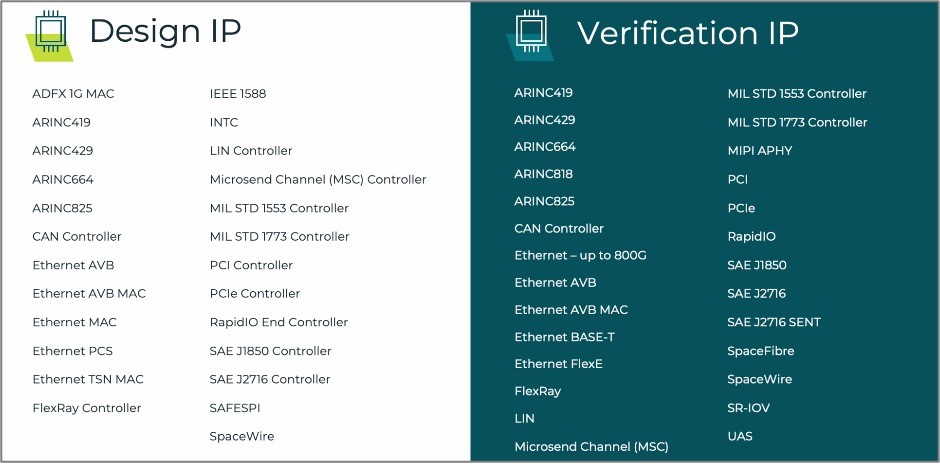

SmartDV已在汽车和航空电子设计方面富有经验和颇有建树,可以成为芯片厂商在探索相关领域时值得信赖的IP合作伙伴。我们的VIP是由具有数十年复杂芯片验证经验的验证工程师所创建。我们还为各种应用提供基于标准的设计IP。下面显示的是我们的一些IP核,它们都适用于本文中讨论的安全关键型设计。

随着芯片的复杂性不断增加,验证也在逐年变得越来越复杂。在当今的芯片设计中,验证往往会消耗大约60%-80%的项目资源,并且通常是整个过程中的瓶颈。正是因为这样的复杂性和重要性,与值得信赖的IP伙伴合作是回报最高的途径,他们将与芯片设计师共同解决其在此过程中遇到的任何问题。

市场差异化带来的定制化需求也在芯片行业中不断凸显。无论您是为下一代SoC、ASIC或FPGA项目采购设计IP,还是寻求验证解决方案(VIP)来完成您的芯片设计,SmartDV都可以快速且可靠地对我们多元化的产品组合进行定制,以满足您独特的设计需求。我们的SmartCompiler™技术使这种定制化可以很完美地实现,并可使芯片设计公司获得更高的回报。IP Your Way™——只需定义您的规格,然后交给我们处理。

我们期待看到您的芯片设计成果应用在道路上或在天空中!

本篇技术文章是Philipp之前发表的同一主题博客文章的后续,他最近也用在线研讨会的方式详细解读了这个话题,大家可以关注“智权半导体”微信公众号,我们将在近期发布他的演讲视频记录。智权半导体科技(厦门)有限公司是SmartDV在中国的全资子公司,其目标是为中国的客户提供更直接和深入的支持,并与中国的合作伙伴开展更全面的合作。

关于Philipp Jacobsohn

Philipp Jacobsohn是SmartDV的高级应用工程师,他为北美和欧洲地区的客户提供设计IP和验证IP方面的支持。除了使SmartDV的客户实现芯片设计成功这项工作,Philipp还是一个狂热的技术作家,乐于分享他拥有的在半导体行业近30年积累的丰富知识。在2023年加入SmartDV团队之前,Philipp在J. Haugg、Synopsys、Synplicity、Epson Europe Electronics、Lattice Semiconductors、EBV Elektronik和SEI-Elbatex等担任过多个工程和现场应用职位。Philipp在瑞士工作。

关于智权半导体

智权半导体科技(厦门)有限公司是SmartDV Technologies™在华设立的全资子公司,其目标是利用SmartDV全球领先的硅知识产权(IP)技术和产品,以及本地化的支持服务来赋能中国集成电路行业和电子信息产业。目前,SmartDV在全球已有300家客户,其中包括十大半导体公司中的七家和四大消费电子公司。

通过将专有的SmartCompiler™技术与数百位专家工程师的知识相结合,SmartDV可以快速、经济、可靠地定制IP,以实现您独特的设计目标。因此,无论您是为下一代SoC、ASIC或FPGA寻找基于标准的设计IP,还是寻求验证解决方案(VIP)来测试您的芯片设计,您都会发现SmartDV的IP非常容易集成,并在性能上可力助您的芯片设计实现差异化。

了解更多关于SmartDV和智权半导体的信息,请浏览:www.smart-ip.cn,或发邮件到:chinasales@smart-ip.cn