移动电子设备通常都是内嵌电池供电,设备的使用/待机时间时刻影响着用户体验。而低功耗的芯片设计,能够极大的降低电子设备的系统功耗,是提升设备续航能力的关键。

芯海科技CSCE2010是一款专为主流消费级笔记本市场打造的32位高性能EC芯片,具有高扩展性、低功耗和开发便捷性的产品特点,已通过英特尔PCL(平台器件列表)认证,以其出色的低功耗IO设计,为笔记本电脑带来更长的续航时间。

MCU 低功耗设计

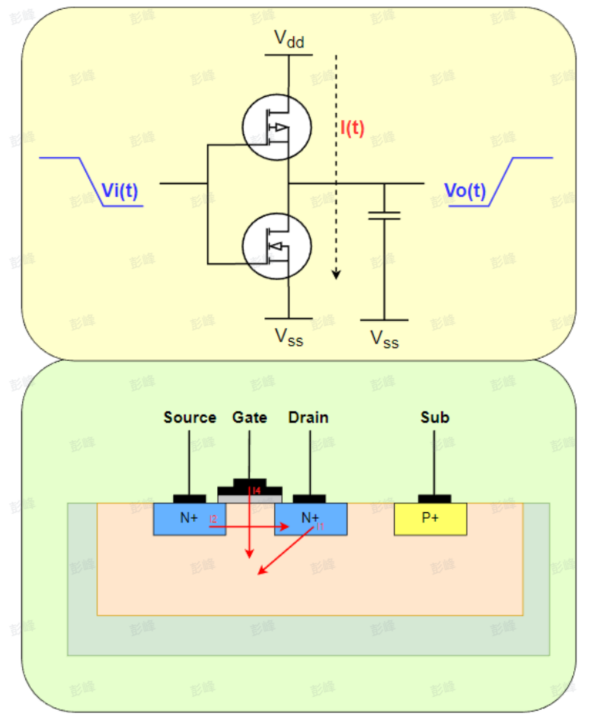

芯片的实质是由逻辑门构成的复杂电路网络。探讨芯片功耗时,我们通常将芯片功耗区分为两种主要类型:静态功耗和动态功耗。

静态功耗,主要由 COMS 电路中器件的漏电流所引起。采用先进的生产工艺技术,能够有效降低静态功耗。

动态功耗,则与芯片器件在工作时的电能消耗密切相关。例如当电路中的信号发生翻转,就会产生短路功耗。同时,驱动元件对负载电容进行充放电时也会产生功耗。这种功耗随着芯片工作状态而变化,因此优化动态功耗需要从电路了设计、工作频率、电压等方面综合考虑。

功耗构成:静态功耗与动态功耗

为了降低上述两种功耗,需运用优化时钟管理、电源管理、设计多种低功耗工作模式,以及通过软件优化来减少不必要的计算和中断,从而达到降低整体功耗的目的。

1. 时钟管理

● 多时钟域,将不同功能模块设置在不同频率的时钟域

● 时钟调节,根据工作负载动态调整时钟频率

● 时钟门控,在空闲时关闭不需要工作模块的的时钟

2. 电源管理

● 多电源域设计,独立控制不同模块的电源

● 动态电压频率缩放(DVFS),根据负载动态调整电压和频率

● 降低内核工作电压、IO 输出电压

3. 低功耗模式

● 空闲模式,在CPU空闲时进入低功耗状态

● 睡眠模式,在系统大部分单元不工作时切换到极低功耗状态

● 掉电模式,保留最少的电路在运行,实现超低功耗

4. 软件优化

● 避免冗长/无效的计算

● 合理使用中断,避免不必要的中断

● 采用低功耗编码算法

根据基础的物理原理,电路的功率与流经电路的电压和电流的乘积成正比。然而,芯片的动态功耗受多个因素影响,不仅仅局限于电压和电流,其动态功耗的计算公式可简化如下:P=C*f*N*V²。

其中:

● C:代表结点电容

● f :表示器件工作频率

● N:是在单时钟周期内翻转的器件数目

● V:代表器件的工作电压

因此可见,通过降低芯片内核的工作电压,可以有效降低芯片的功耗。同理,芯片对外 的IO 输出驱动也会产生功耗,因此降低 IO 驱动电流同样能有效降低芯片的整体功耗。

CSCE2010的低功耗IO设计

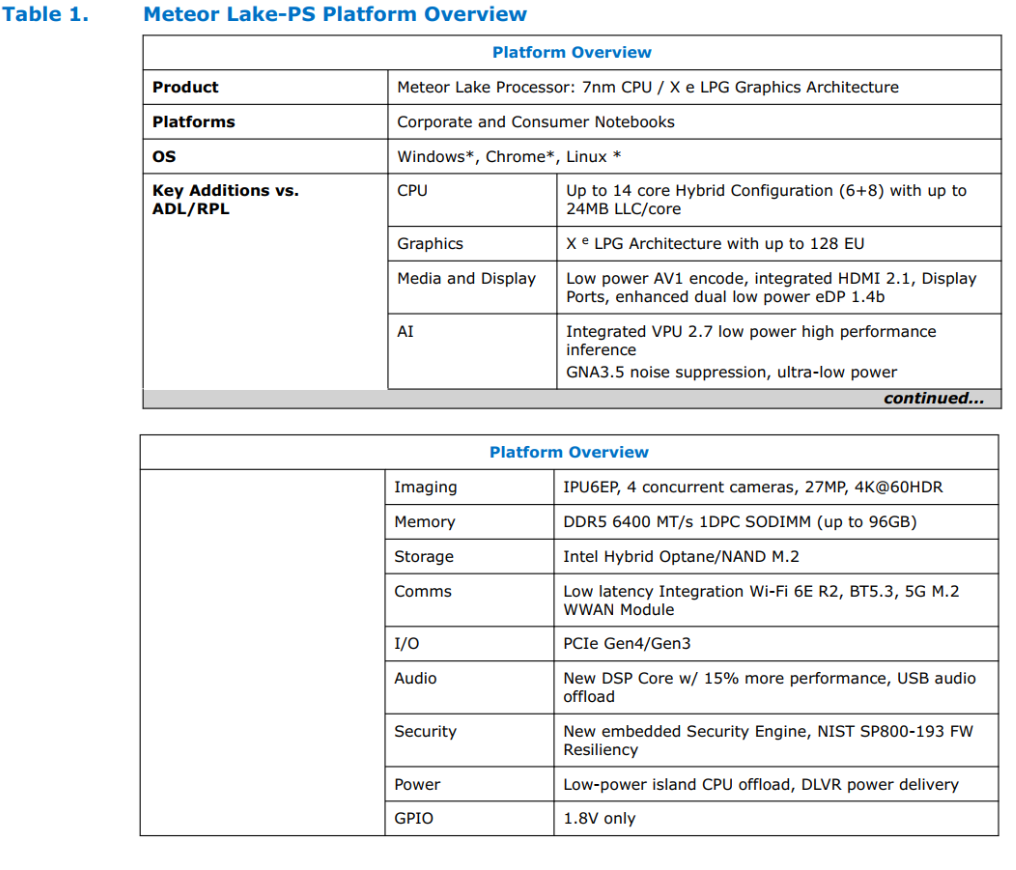

2023年9月, Intel发布了Meteor Lake架构的CPU ,该架构在低功耗设计领域做出了很多改进,其中IO接口已全面升级为1.8V,这一重要改进为降低系统功耗做出了显著贡献。

芯海科技CSCE2010 作为一款高度集成、兼容性能出色的 EC 产品,在设计上展现了其独特的创新。在对外连接的IO方面, 采用了独立电源域设计,使得它在接入不同电压需求的平台时,都能游刃有余地应对。

当与 Meteor Lake 平台1.8V的IO接口相连时,CSCE2010 能够支持1.8V 输入输出(推挽输出),而且无需借助外部上拉电阻,从而大大简化了接口电路,不仅提升了设备的电气性能,还降低了能耗。

更为出色的是,如果需要将CSCE2010 连接到其他使用3.3V IO的CPU平台,它同样可以轻松应对。产品可以灵活的切换为 3.3V的输入输出(推挽输出)模式,并且也无需外部上拉电阻。从而增强了产品的通用型和适应性,满足多样化的应用场景需求。

CSCE2010 独特的 IO 电源设计,不仅展现了其优秀的灵活性与兼容性,更在实际应用中为客户带来了显著便利。通过减少硬件设计中的互联线路复杂性,帮助客户简化了整体设计流程,同时降低了物料清单(BOM )成本,从而为客户创造了更多的价值。

目前,该EC产品已经成功导入各类CPU平台项目, 通过实际应用充分验证了其广泛的兼容性。

除此之外,CSCE2010还集成了 I2C、SPI、UART、I3C、TIMER、eSPI 等丰富外设接口。考虑到不同外设工作需要的频率不同,芯片创新地采用多级 PLL 分频设计,以确保在满足各种外设最小频率要求的同时,最大限度地降低芯片运行功耗。其次,为了更好地满足PC系统在不同使用场景下的低功耗需求,CSCE2010还设计 了Sleep、 DeepSleep 两种低功耗模式,进一步提升效能表现。

芯海科技始终将技术创新视为驱动业务发展的核心力量,致力于构建以EC为核心,横向拓展至PD、HUB、BMS、HapticPad等多元化计算外围产品的PC生态。

未来,芯海科技将持续加强和完善PC系列产品的战略布局。通过PC生态产品的系列化、平台化创新,为全球PC供应链注入更多活力,为客户提供更具竞争力特性的PC产品。

来源:芯海科技