┃ 直播详情 ┃

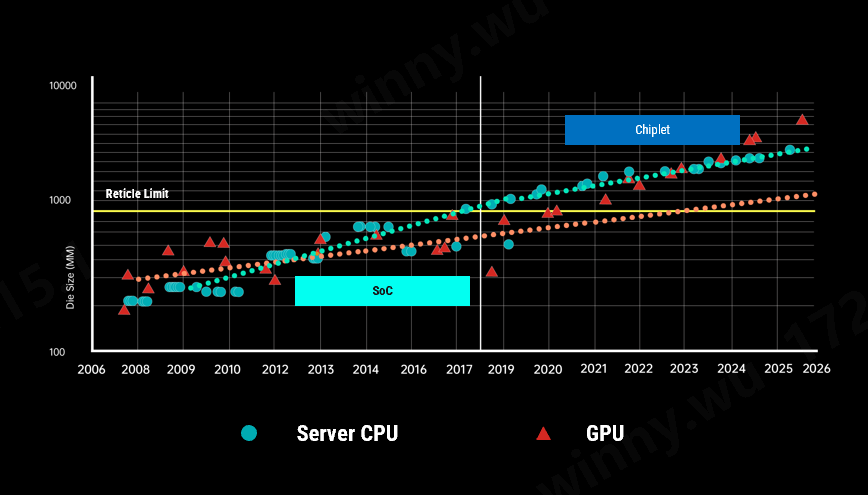

随着半导体制程不断逼近物理极限,越来越多的芯片厂商为了提升芯片性能和效率开始使用Chiplet技术,将多个满足特定功能的芯粒单元通过Die-to-Die互联技术与底层基础芯片封装在一起,形成一个系统级芯片。

在单个芯片内部,基于Chiplet架构的IO Die、Die-to-Die互联技术是增强单个芯片性能和性价比的关键途径。片内的高速互联可以大大降低数据传输的延迟和功耗。通过高速的内部互联,不同的功能模块可以快速共享数据,优化内存访问和计算资源的分配,提高整体能效比。简而言之,Chiplet架构下的内部高速互联,为芯片算力的提升开辟了新的可能。

Die-to-Die片内互联:UCIe互联标准

Die-to-Die互联是Chiplet架构的核心基础,它为芯片内部不同Die之间的紧密协作提供了传输的接口。Universal Chiplet Interconnect Express (UCIe) 是一种开放的行业互联标准,可在 Chiplet 之间提供高带宽、低延迟、节能且经济高效的封装内连接。

自2012年成立以来,UCIe 的既定目标是为Chiplet建立一个开放且无处不在的生态系统。无论这意味着简单地将某些物理方面标准化以简化制造,还是实现真正的混合匹配设置。在这样的生态系统中,客户可以自由地从多家芯片制造商那里挑选使用Chiplet构建的芯片模块,而这些都需要一个强大的基础标准来支撑。

UCIe技术被用于连接多个芯片Die、内存控制器和其他计算资源,形成一个高度集成的系统。这种集成方式允许不同的计算单元之间通过高速的数据通道进行通信,从而提高整体系统的处理能力和效率。此外,使用UCIe技术还可以实现动态功耗管理,通过在不同计算单元之间动态调整功率分配,以优化系统的能效比。UCIe 1.1 于2023年8月发布覆盖涵盖了芯片到芯片之间的I/O 物理层、协议和软件堆栈等规范。之后时隔1年,UCIe 2.0规范正式发布。UCIe 2.0规范引入了对可管理性标准化系统架构的支持,并全面解决了系统级封装(SiP)生命周期中跨多个芯粒的可测试性、可管理性和调试(DFx)的设计难题。

为了让大家了解Chiplet互联趋势与Die-to-Die接口技术,11月5日晚19点,我们特别邀请到奇异摩尔高级设计经理王彧博士做客贸泽电子芯英雄联盟直播间,与大家展开深入讨论,欢迎预约围观!

直播时间:2024年11月5日 19:00~20:30

直播主题:AIGC时代:探索Chiplet互联趋势与Die-to-Die接口技术

▶ 本期看点

① Chiplet&互联主流案例分析

② Die-to-Die技术趋势 (封装形式、数据率、带宽密度、延时等)

③ ISP的发展趋势UCle国际互联标准V1.1-V2.0升级解析

④ 奇异摩尔Kiwifabric统一互联架构产品解决方案

▶ 嘉宾介绍

分享嘉宾————王彧博士

奇异摩尔集成电路设计有限公司高级设计经理,近十年半导体产业经验,主要研究领域为高速互联接口集成电路设计,设计并量产PCIe、DDR、MIPI等多种高速接口,在ISSCC、JSSC、TCAS等集成电路设计顶级会议和期刊上发表论文十余篇,申请和授权国内外专利6项。

关于奇异摩尔:

奇异摩尔成立于2021年,专注于AI网络全栈式互联产品和解决方案。公司依托高性能RDMA和Chiplet技术,开发了统一互联架构Kiwi Fabric,满足超大规模AI计算平台的高性能需求。产品涵盖智能网卡、GPU片间互联芯粒、芯片内算力扩展的IO Die和UCIe Die2Die IP等,构成全链路互联解决方案。核心团队来自NXP、Intel、Broadcom等行业巨头,拥有丰富的AI互联产品开发、量产和管理经验。

主持人————张国斌

电子创新网创始人兼CEO ,

西安电子科技大学电子工程专业毕业,半导体领域知名KOL。

有多年的半导体媒体内容与运营经验,撰写过大量产业分析文章。(微信号:18676786761)

▶ 直播福利

1、预报名奖:20元京东E卡(10名)

通过小鹅通平台填写预约信息,我们将在所有预报名的用户中随机抽取10名,送出价值20元的京东E卡。

2、优秀提问奖:30元京东E卡(5名)

直播期间,在小鹅通平台评论区参与提问,随机抽取5名提问用户,送出价值30元的京东E卡。

注意事项

请预约直播的用户填写正确的邮箱,我们将通过邮件的方式联系获奖者。如因用户信息填写不全无法发放奖励的,自动取消获奖资格,随机抽取其他人员。直播福利的最终解释权归属电子创新网所有。

扫描以下二维码进行预约报名吧!

欢迎扫码加入直播交流群,和同行进行深入沟通交流!