Sondrel 为架构未来 IP 平台补充了封装供应链方案,以降低风险

现成的设计和制造方案可以缩短上市时间

现成的设计和制造方案可以缩短上市时间

由于芯片每秒需要处理的计算越来越多,其设计变得越来越复杂,与此同时,确保芯片中大量数据的及时传输也面临着重大挑战。

确定质量成本的过程很复杂

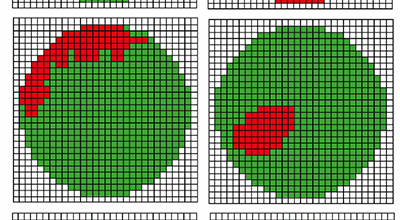

芯片供应链由不同的分包商组成,他们分别独立开展各自相应的任务,因此分包商之间的沟通渠道很容易断开。Sondrel 称其为“沟通鸿沟”,并警告说,沟通鸿沟可能会导致问题波及供应链上的其余各方。

面向ADAS 应用的高性能计算 IP 平台设计的关键动力,即是 FlexNoC 的超强可配性与优越表现

FlexNoC的可配置性和性能是为 ADAS 应用设计高性能计算 IP 平台的关键

半导体市场供应短缺的情况似乎已开始缓解,但Sondrel仍要提醒大家注意供应链中存在一个问题,且很可能会导致订单意外延误。

ASIC设计阶段有一个关键环节就是定义 LINT、CDC(多时钟域检查)、DFT(可测试性) 和 Timing(时序)等各种设计约束。但是,每一种的约束文件都要单独定义和维护,这增加了项目管理和保持一致性的难度。