电子元件工业联合会(JEDEC)刚刚正式发布了 HBM3 高带宽内存标准,可知其较现有的 HBM2 和 HBM2e 标准再次迎来了巨大的提升。JEDEC 官方新闻稿写道,JESD238 为新一代 HBM3 动态随机存储器指定了发展方向。除了 6.4 Gb/s 速率 @ 819 GB/s 的带宽,它还支持 16-Hi 堆栈 @ 64GB 容量。

(来自:JEDEC 官网)

据悉,HBM3 运用了创新方案,旨在带来更高带宽、更低功耗、以及更密集的单位容量,能够极大推动图形处理、高性能计算和服务器等领域的使用体验。

以下是 HBM3 的主要特点:

● 在经过验证的 HBM2 架构的基础上进一步扩展带宽,将每个引脚的速率提升一倍(定义 6.4 GB/s),以实现 819 GB/s 的高带宽。

● 将独立通道数从 HBM2 时代的 8 个提升至 16 个,且每个通道都有两组“伪通道”(Pseudo Channels),意味 HBM3 可虚拟支持 32 通道。

● 支持 4-Hi、8-Hi、12-Hi 的硅通孔(TSV)堆栈,并为将来的 16-Hi 方案实现做好了准备。

● 支持每层 8~32 Gb 的容量密度,可轻松支持 4GB(8Gb 4-Hi)到 64GB(32Gb 16-Hi)设备密度,预计初代产品将基于 16Gb 存储层。

● 为满足市场对高平台层级的可靠性、可用性与可维护性(简称 RAS)需求,HBM3 还一如了强大的、基于符号的片上 ECC,以及实时错误报告和透明度。

● 通过在主机接口端使用低摆幅(0.4V)信号和较低的工作电压(1.1V),来进一步提升能效表现。

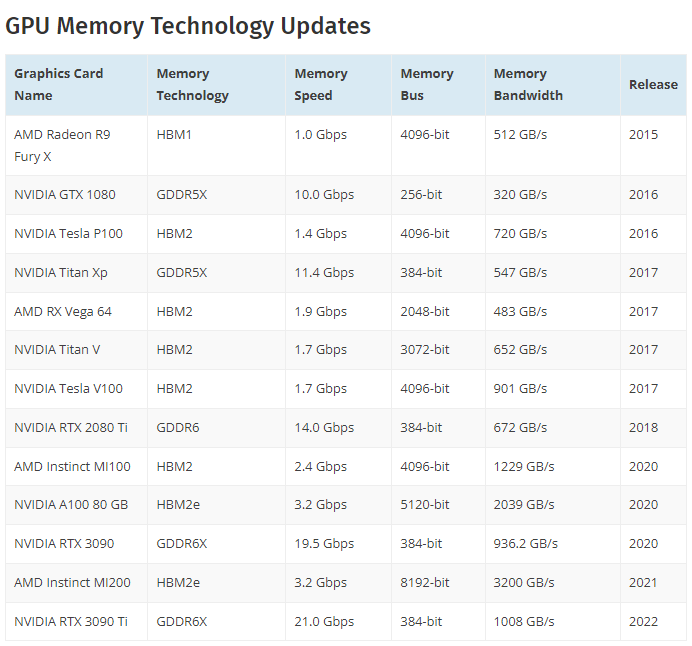

截图(via WCCFTech)

英伟达技术营销总监兼 HBM 小组委员会主席 Barry Wagner 表示:

凭借增强的性能与可靠属性,HBM3 将为需要巨大带宽和容量的新应用提供有力的支撑。

美光高性能内存与网络事业部副总裁兼总经理 Mark Montierth 则称:

HBM3 将使行业攀上更高的性能巅峰,提升可靠性并降低能耗。

美光将凭借先进内存堆叠和封装方面的资深经验,来引领后续的计算平台市场。

SK 海力士 DRAM 产品企划副总裁 Uksong Kang 补充道:

随着 HPC 与 AI 应用的不断进步,对更高性能和能效的需求增长,也较以往进一步加速。

随着 JEDEC HBM3 标准的正式颁布,SK 海力士期待着通过增强型 ECC 方案,为客户提供兼具高性能、最佳能效和更高稳定性的 DRAM 产品。

SK 海力士很高兴能够与行业合作伙伴携手共建强大的 HBM 生态系统,最终为我们的客户提供 TSG 和 TCO 方面的更高价值。

Synopsys IP 与战略营销副总裁 John Koeter 亦表示:

十多年来,Synopsys 一直是 JEDEC 的积极贡献者,帮助推动了 HBM3、DDR5、LPDDR5 等先进内存接口在一系列新兴应用中的开发和采用。

Synopsys 的 HBM3 IP 和验证解决方案,已被公司客户率先采用。通过加速新接口与高性能 SoC 的集成,还有助于具有高内存带宽和能效的多芯片系统级封装的设计与研发。

来源:cnBeta.COM