软件和解决方案部 黄琦

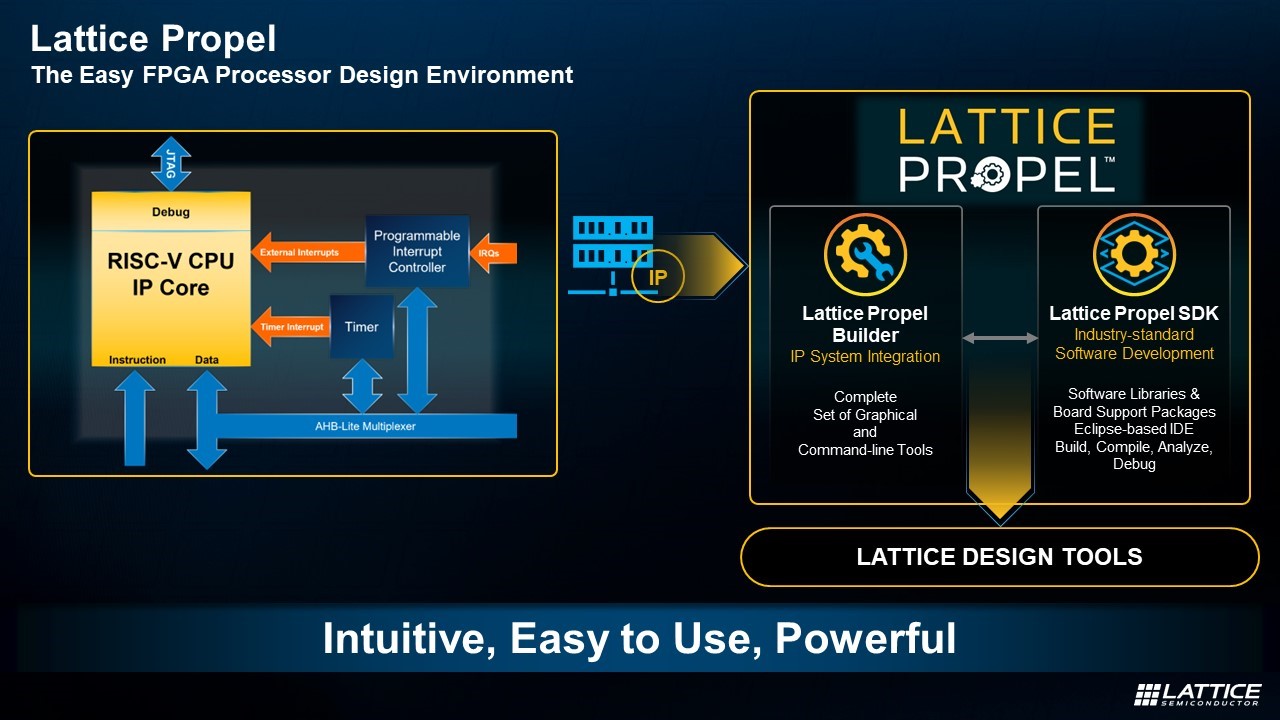

许多嵌入式系统的开发者都对使用基于FPGA的SoC系统感兴趣,但是基于传统HDL硬件描述语言的FPGA开发工具和复杂流程往往会令他们望而却步。为了解决这一问题,莱迪思的Propel工具套件提供了基于图形化设计方法的设计环境,用于创建,分析,编译和调试基于FPGA的嵌入式系统,从而完成系统软硬件设计。

莱迪思的Propel工具套件由两部分组成:Propel Builder提供图形化的SoC系统和硬件设计,通过拖放方式,选择处理器和相关的外设与IP,通过图形化的方式进行配置和连接,从而完成系统层面的硬件设计; Propel SDK通过图形化的集成开发环境(IDE)和工具链,基于Builder提供的硬件信息,完成相对应的软件开发。

在最新版本的莱迪思Propel(2024.1)中,“进一步简化开发周期,改善软硬件设计人员的体验,使他们能够专注于FPGA处理器系统的创新和优化。”仍然是不变的核心设计理念。

例如,具有拖放IP实例化和“构建即正确”的设计方法,大大增强了易用性;通过图形化设计界面的易用性,辅之以命令行工具的快捷性,能够灵活得满足各种技能水平的设计人员的需要;集成的IP服务器和本地端IP仓库,提供了丰富的IP资源,可以帮助开发人员在基于莱迪思的FPGA芯片上快速构建新的SoC嵌入式系统;SDK通过集成的IDE和工具链,中间库,电路板级支持包(BSP),能快速实现软件开发,编译,调试,并协同硬件进行系统集成。

莱迪思Radiant是另一款适用于网络边缘应用的全功能、易于使用的工具套件,通过提供强大的优化和分析功能,实现快速和可预测的设计收敛。其模块化、基于向导的图形用户界面可以直观地引导用户进行设计创建、综合、约束输入、设计分析、调试和编程等设计流程,让软件的易用性达到新的高度。在最新的更新中,Radiant已经可以支持Windows 10/11(64 bit)操作系统和Linux操作系统(Red Hat Enterprise Linux 7.9 64位、8.4或8.8 64位\以及Ubuntu 20.04或22.04 LTS 64位和CentOS 8.4)。

使用多功能行业标准的设计方法,为设计人员和嵌入式软件开发者带来信心,也是莱迪思软件工具的特点。例如,Radiant使用了在FPGA行业中被广泛用于设计约束的SDC格式文件,Propel SDK使用基于Eclipse的行业标准工具。同时,莱迪思综合工具广泛还覆盖了各种设计入门语言,包括FPGA支持的所有标准语言,如VHDL、Verilog和System Verilog。在新版本中,与Verilog类似,Propel 2024.1增强了对VHDL的支持,用VHDL和Verilog编写的RTL代码可转换为胶合逻辑组件,用于系统集成。

除此之外,莱迪思软件工具集中还包括了智能规划功能,比如Radiant和Diamond都可以显示时序图、功耗计算器、布线矩阵、物理布局和拥塞等信息,或者是设计中发生拥塞的位置并进行更改。

这意味着设计人员可以自定义实现方式以满足他们的需求——如确保引脚正确放置,显示模块的位置和可优化的模块等。通过此类高级优化功能,设计人员能够为器件实现最佳的时序和面积优化。此外,精确的分析功能实现了设计的可视化,用户可以通过相关报告,了解是否实现了设计结果。

与智能性、便捷性同等重要的是安全性。如今,网络攻击的频率和复杂性正逐步增加,网络安全和网络保护恢复是所有应用设计人员要考虑的头等大事。为了实现这一目标,莱迪思在其软件中提供了行业领先的安全特性,尤其是Radiant™和Propel™设计软件的最新版本现已支持全新的MachXO5D-NX FPGA系列和最新的Sentry解决方案集合。

总体而言,无论是经验丰富的工程师还是刚刚入门的新手,无论面对的是简单的应用还是复杂的嵌入式控制和数据处理系统,凭借直观的界面和全面的功能,莱迪思软件工具集都将帮助FPGA开发人员在其应用和系统开发中快速、高效地取得设计成功。