Cadence 推出面向硅设计的全新 Neo NPU IP 和 NeuroWeave SDK,加速设备端和边缘 AI 性能及效率

Neo NPU 可有效地处理来自任何主处理器的负载,单核可从 8 GOPS 扩展到 80 TOPS,多核可扩展到数百 TOPS

Neo NPU 可有效地处理来自任何主处理器的负载,单核可从 8 GOPS 扩展到 80 TOPS,多核可扩展到数百 TOPS

2023 年,生成式 AI 如同当红炸子鸡,吸引着全球的目光。当前,围绕这一领域的竞争愈发白热化,全球陷入百模大战,并朝着千模大战奋进。在这场潮流中,AI 芯片成为支撑引擎,为大模型应用提供强有力的支持。

业界卓越的 Tensilica Xtensa LX 平台第 8 代已经上线,可提供显著的系统级性能增强,同时确保理想能效

将 RTL 收敛速度加快 5 倍,结果质量改善 25%

3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是 Cadence 112G-ELR SerDes IP 系列产品的新成员。

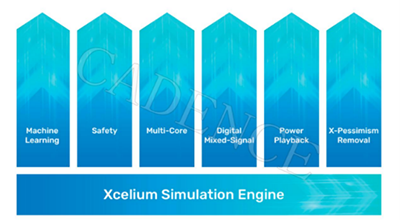

保证覆盖率的同时优化仿真回归

这是一个业界用于打造差异化定制芯片的领先平台,可借助生成式 AI 技术显著提升设计生产力;

新加入的生态系统成员包括 Kudan 和 Visionary.ai,有助于快速部署高性能、高能效的基于 SLAM 和 AI ISP 的解决方案

Allegro X AI 可自动执行 PCB 布局设计和小至中型 PCB 布线设计,将物理布局布线和分析用时从数天缩短至几分钟

Cadence 凭借关键的 EDA、云和 IP 创新荣获 TSMC 大奖;